Verilog 加法器和减法器(4)

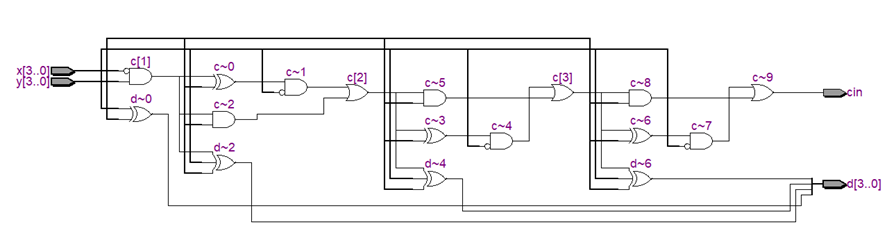

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作。 比如下图是4位二进制减法逻辑电路图。

8位二进制减法的verilog代码如下:

module subn(x, y, d,cin);

parameter n=8; input [n-1:0] x;

input [n-1:0] y;

output reg[n-1:0] d; //diff

output reg cin; //borrow from high bit

reg [n:0] c;

integer k; always @(x,y) begin

c[0] = 1'b0;

for(k = 0; k < n; k = k + 1) begin

d[k] = x[k]^y[k]^c[k];

c[k+1] = (~x[k]&(y[k]^c[k]))|(y[k]&c[k]);

end

cin = c[n]; end endmodule

module subn( x, y, d,cin); parameter n=8;

input [n-1:0] x;

input [n-1:0] y;

output [n-1:0] d;

output cin; assign {cin, d} = x - y ; endmodule

module subn( x, y, d,cin);

parameter n=8;

input [n-1:0] x;

input [n-1:0] y;

output [n-1:0] d;

output cin; wire [n:0] c;

genvar k;

assign c[0]=0;

assign cin=c[n]; generate

for(k = 0; k <= n-1; k = k + 1) begin:subbit

fullsub stage(c[k],x[k],y[k],d[k],c[k+1]);

end

endgenerate endmodule

testbench 代码如下:

`timescale 1ns/1ns

`define clock_period 20 module subn_tb;

reg [7:0] x,y; wire cin;

wire [7:0] d;

reg clk; subn #(.n(8)) subn_0(

.x(x),

.y(y),

.d(d),

.cin(cin)

); initial clk = 0;

always #(`clock_period/2) clk = ~clk; initial begin

x = 0;

repeat(20)

#(`clock_period) x = $random; end initial begin

y = 0;

repeat(20)

#(`clock_period) y = $random; end initial begin

#(`clock_period*20)

$stop;

end endmodule

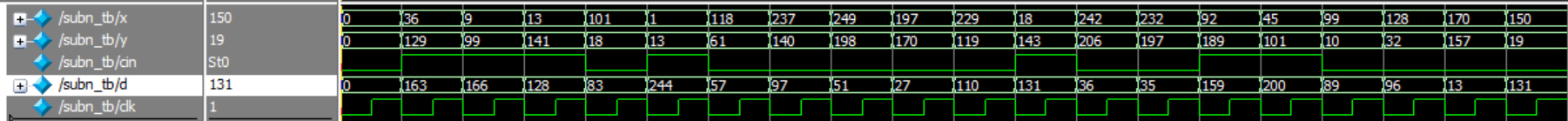

功能验证的波形图如下。注意:我们选择了radix为unsigned

Verilog 加法器和减法器(4)的更多相关文章

- Verilog 加法器和减法器(8)-串行加法器

如果对速度要求不高,我们也可以使用串行加法器.下面通过状态机来实现串行加法器的功能. 设A=an-1an-2-a0, B=bn-1bn-2-b0,是要相加的两个无符号数,相加的和为:sum=sn-1s ...

- Verilog 加法器和减法器(7)

在计算机中浮点数 表示通常采用IEEE754规定的格式,具体参考以下文章. https://www.cnblogs.com/mikewolf2002/p/10095995.html 下面我们在Veri ...

- Verilog 加法器和减法器(6)

为了减小行波进位加法器中进位传播延迟的影响,可以尝试在每一级中快速计算进位,如果能在较短时间完成计算,则可以提高加法器性能. 我们可以进行如下的推导: 设 gi=xi&yi, pi = xi ...

- Verilog 加法器和减法器(3)

手工加法运算时候,我们都是从最低位的数字开始,逐位相加,直到最高位.如果第i位产生进位,就把该位作为第i+1位输入.同样的,在逻辑电路中,我们可以把一位全加器串联起来,实现多位加法,比如下面的四位加法 ...

- Verilog 加法器和减法器(2)

类似半加器和全加器,也有半减器和全减器. 半减器只考虑当前两位二进制数相减,输出为差以及是否向高位借位,而全减器还要考虑当前位的低位是否曾有借位.它们的真值表如下: 对半减器,diff = x ^y, ...

- Verilog 加法器和减法器(1)

两个一位的二进制数x,y相加,假设和为s,进位为cout,其真值表为: 从真值表中,我们可以得到:s = x^y, cout = x&y,实现两个一位数相加的逻辑电路称为半加器. 实现该电路的 ...

- Verilog 加法器和减法器(5)

前面二进制加法运算,我们并没有提操作数是有符号数,还是无符号数.其实前面的二进制加法对于有符号数和无符号数都成立.比如前面的8位二进制加法运算,第一张图我们选radix是unsigned,表示无符号加 ...

- 基于Xilinx的Synthesize

所谓综合.就是讲HDL语言.原理图等设计输入翻译成由与.或.非们和RAM.触发器登记本逻辑单元的逻辑连接(即网表).并依据目标和要求(约束条件)优化生成的逻辑连接. ISE-XST XST是Xilin ...

- FPGA综合工具--Synplify Pro的常用选项及命令

最近要用到Synplify,但以前没使用过,无基础,找到一篇帖子,隧保存下来. 本文转自:http://blog.sina.com.cn/s/blog_65fe490d0100v8ax.html Sy ...

随机推荐

- 反射调用 java bean的set和get方法

一.使用java.beans.PropertyDescriptor import java.beans.IntrospectionException; import java.beans.Proper ...

- 循序渐进学.Net Core Web Api开发系列【8】:访问数据库(基本功能)

系列目录 循序渐进学.Net Core Web Api开发系列目录 本系列涉及到的源码下载地址:https://github.com/seabluescn/Blog_WebApi 一.概述 本篇讨论如 ...

- 异常日志框架Exceptionless结合.NET Core(本地部署)

一.前言 1.分布式异常日志收集框架Exceptionless是开源的工具,根据官方给出的说明: Exceptionless可以为您的ASP.NET.Web API.WebFrm.WPF.控制台和MV ...

- UICollectionView 常用操作

1 iOS开发 - UICollectionView点击展开收起

- java 中的同步机制

对于有些场景,需要a.b线程按照顺序去执行,因为b线程要依赖a线程对某共享资源或 状态处理后,对于这种情况可以使用 private CountDownLatch connectedSignal = n ...

- Bzoj3677:树形DP

首先我们知道这棵树的形态,一眼DP.考虑蓝线的性质,显然蓝线在树上是连接连续三个节点的.这样就有三种情况:连接 一个节点 的 某个孩子->本身->父亲 或者 一个孩子->本身-> ...

- BZOJ2973 : 石头游戏

考虑到$lcm(1,2,3,4,5,6)=60$,所以操作序列每60秒一个循环. 将操作表示成转移矩阵的形式,预处理出前60秒的转移矩阵以及它们的乘积$B$. 那么t秒的转移矩阵为前$t\bmod 6 ...

- phpexcel一个bug

大家好! 我想我发现了这个bug. 如果我从文件中图像删除,它加载正常. 如果有图像时候,何时$ objPHPExcel = PHPExcel_IOFactory :: load($ file);我得 ...

- chrome ui源码剖析-ViewProp

先熟悉set的find原理 http://www.cnblogs.com/Clingingboy/p/3252136.html 这个类改造下,还是非常实用的,可以对于不同的类型做数据存储 一.Vi ...

- linux-socket connect阻塞和非阻塞模式 示例

~/cpp$ ./connect 192.168.1.234 1234 kkkk block mode: ubuntu 14.04 : time used:21.0.001053s connect ...