关于FPGA电源精度要求

FPGA对DC-DC精度的要求不断提升

FPGA厂商不断采用更先进的工艺来降低器件功耗,提高性能,同时FPGA对供电电源的精度要求也越加苛刻,电压必须维持在非常严格的容限内,如果供电电压范围超出了规范的要求,就有会影响到FPGA的可靠性,甚至导致FPGA失效。

无论是Intel (Altera)FPGA还是Xilinx FPGA均在数据手册中明确提出了电源精度要求,其中要求最高的是内核和高速收发器的供电。举例来看,Intel公司的Cyclone V、Cyclone 10 GX、Arria10、Stratix 10的电源精度要求在±30mV以内。

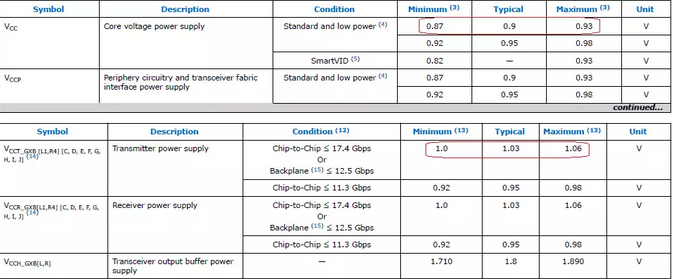

Arria10的core和transceiver数据手册上的供电要求(±30mV):

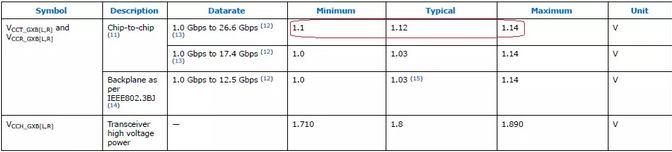

Stratix10的core和transceiver数据手册上的供电要求(±30mV):

如果Stratix10需要支持26.6G transceiver时,收发器供电精度要求 ±20mV以内:

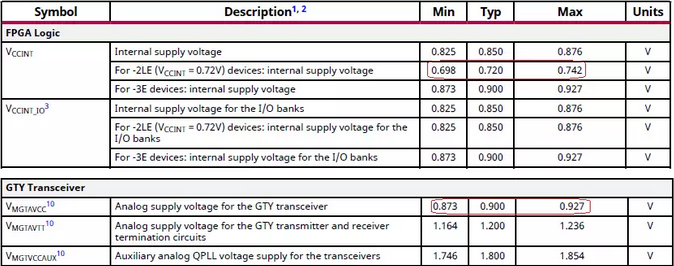

Xilinx公司的Artix 7、Kintex7、Virtex 7等器件电源精度要求也是在±30mV以内,KU+、VU+器件要求电源精度必须达到±22mV以内。

Kintek Ultrascale+的core和transceiver数据手册上的供电要求(±22mV):

由此可见,新一代FPGA的供电精度都在±20-30mv左右,已经是单板中对电源精度要求最为苛刻的器件之一了。

由于输出精度都是理论计算值,并没有考虑单板PCB布线和其他外部设备引入的干扰和误差,因此实际设计产品时,电源输出精度不但必须符合数据手册中的要求,还必须预留一定的余量,通常设计中,我们还会保留50%-100%余量,以保证系统长期可靠工作。

电源的稳态直流精度及计算方法

供电电源的稳态直流精度主要取决于两个因素:电压调整精度和输出电压纹波。这里有一个误区,很多工程师只通过DC-DC数据手册上的电压输出精度来判断器件是否符合要求,其实这是不正确的。 首先很多DC-DC需要外部反馈电阻来决定最终的输出电压,数据手册上的电压调整精度是指芯片本身的输出精度,并没有计算反馈电路引入的偏差。其次,器件数据手册上的电压输出精度并不包含输出电压纹波,必须将两者叠加计算才能得到正确的直流稳态精度。

正确的电源稳态直流精度的计算公式如下:

电源直流稳态精度 =器件输出精度(这里要求全温度,全负载时的精度,很多器件手册只给出典型值,因此要小心)+ ½ 纹波 + 外部反馈电阻精度引入的误差。

高精度电源对减低FPGA功耗的作用

除了电源精度影响整个系统的稳定性和可靠性,更高精度的电源还可以帮助我们降低系统功耗。

我们举一个例子,一个FPGA推荐的典型工作电压为0.85V,最高工作电压为0.88V,最低工作电压为0.82V, 假设供电DC-DC实际稳态直流精度是±30mV ,那么DC-DC必须正好工作在0.85V,如果电压更低,就会低于FPGA对电压下限的要求。

文章参考 来源:骏龙ALTERA社区

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间

关于FPGA电源精度要求的更多相关文章

- 使用Intel的FPGA电源设计FPGA 供电的常用反馈电阻阻值

使用Intel的FPGA电源设计FPGA 供电的常用反馈电阻阻值. 当前仅总结使用EN5339芯片的方案 Vout = Ra*0.6/Rb + 0.6 芯片手册推荐Ra取348K,则 3.3V时,取R ...

- FPGA电源设计

LDO(低压差线性稳压器),FPGA需要3.3V.2.5V和1.2V,可选用凌力尔特LINEAR:LT1083/84/85,低压差正压可调稳压器. 应用电路如图所示: 输入端加10UF电解电容,输出端 ...

- 【转】分享II→IV FPGA本人的几个版本电源模块设计的方案

很多人问我FPGA的电源怎么怎么着,当然也有人瞎忽悠乱设计,当然我的设计也不是很完美...这里把我当年第一次设计FPGA,到现在的电源方案,几个演变.分析的过程,给大家讲讲... (1)FPGA电源方 ...

- FPGA设计中的电源管理(转载)

过去,FPGA设计者主要关心时序和面积使用率问题.但随着FPGA不断取代ASSP和ASIC器件,设计者们现正期望能够开发低功耗设计,在设计流程早期就能对功耗进行正确估算,以及管理和对与FPGA相关的各 ...

- FPGA的引脚VCCINT 、VCCIO VCCA

首先是看到FPGA在配置的时候有三种不同的电VCCINT .VCCIO VCCA,于是就查了下有什么不同: FPGA一般会有许多引脚,那它们都有什么用呢? VCCINT为施加于 FPGA 内核逻辑的电 ...

- 关于FPGA的一些小见解

Xilinx FPGA配置bit流文件 Xilinx FPGA的供电是采用USB作为电源,使用Verilog HDL或VHDL实现的逻辑电路通过Xilinx的综合工具生成bit流文件,通过Digile ...

- FPGA噪声干扰

在FPGA高速AD采集设计中,PCB布线差会产生干扰.今天小编为大家介绍一些布线解决方案. 1.信号线的等长 以SDRAM或者DDRII为例,数据线,命令线,地址线以及时钟线最好等长,误差不要超过50 ...

- 通俗讲解MOSFET

一位工程师曾经对我讲,他从来不看MOSFET数据表的第一页,因为“实用”的信息只在第二页以后才出现.事实上,MOSFET数据表上的每一页都包含有对设计者非常有价值的信息.但人们不是总能搞得清楚该如何解 ...

- SDRAM 学习笔记(一)

前面几篇博客已经讲到了关于0V7725的相关驱动问题,那么OV7725驱动成功之后,设定OV7725输出RGB565格式,那么对于640x480x16,那么若是选用FIFO,应该设置为位宽16bit, ...

随机推荐

- ASP.NET MVC 路由系统类

RouteData public class RouteData { private RouteValueDictionary _dataTokens; private IRouteHandler _ ...

- ZOJ 2965 Accurately Say "CocaCola"!(预处理)

Accurately Say "CocaCola"! Time Limit: 2 Seconds Memory Limit: 65536 KB In a party he ...

- 通过Fegin远程调用 ,返回JPA Page 对象报错

Caused by: com.fasterxml.jackson.databind.JsonMappingException: Can not construct instance of org.sp ...

- 【PL/SQL编程】块结构

[DECLARE] --声明部分,可选 BEGIN --执行部分,必须 [EXCEPTION] --异常处理部分,可选 END

- 浅谈js异步

大家都知道,js是一个单线程的语言(只有一个线程来执行js函数),所以如果某一个函数执行任务耗时比较长的话,就会造成阻塞,使得后续任务一直处于等待状态. 一.阻塞示例 function f1(){ ; ...

- FFmpeg再学习 -- 硬件加速编解码

为了搞硬件加速编解码,用了一周时间来看 CUDA,接下来开始加以总结. 一.什么是 CUDA (1)首先需要了解一下,什么是 CUDA. 参看:百度百科 -- CUDA 参看:CUDA基础介绍 参看: ...

- 【Java实战】源码解析Java SPI(Service Provider Interface )机制原理

一.背景知识 在阅读开源框架源码时,发现许多框架都支持SPI(Service Provider Interface ),前面有篇文章JDBC对Driver的加载时应用了SPI,参考[Hibernate ...

- 4. 什么是应用服务器? - JavaEE基础系列

本文是JavaEE基础系列的第四节. Java EE简介 - JavaEE基础系列 JSR简介 - JavaEE基础系列 什么是JSR参考实现? - JavaEE基础系列 上一节介绍了什么是JSR参考 ...

- linux 系统优化+定时任务

安装软件 通过yum安装 自动补全工具:yum completion yum install -y tree bash-completion wget vim find -[TAB] 更改系统的yum ...

- PHP 关于empty和isset对于参数的判断结果

<?php class test{} $a1 = null; $a2 = ""; //$a3 = $a4 = 0; $a5 = '0'; $a6 = false; $a7 = ...