基础004_V7-DSP Slice

主要参考ug479.pdf。之前的文章:FIR调用DSP48E_05。本文主要记录基本用法。

一、DSP48核

A-参数说明

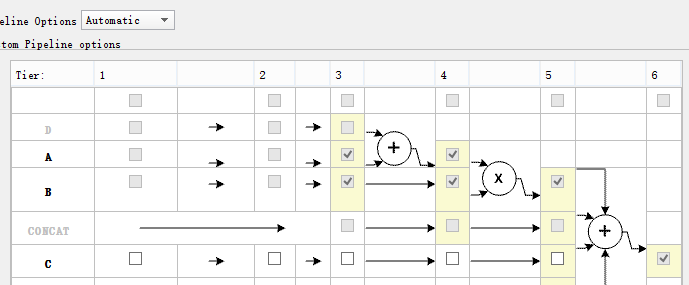

- instrctions,多个功能,通过sel选用

目前没发现C勾选与否,有何影响。

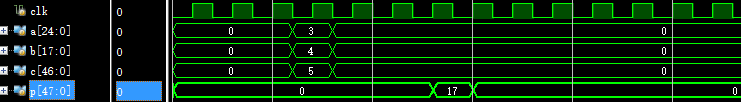

如上图所示,结果3拍后输出:

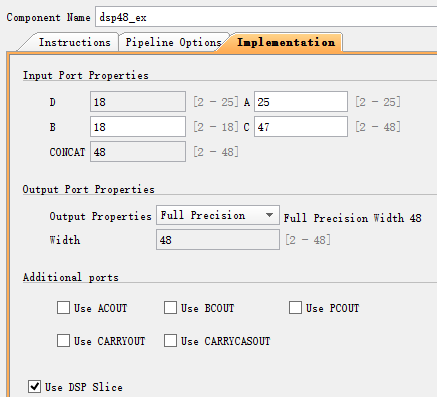

其他参数:

B-IP调用

生成IP核,参数设置完毕直接调用即可

dsp48_ex dsp_inst(

.CLK(clk),

.A(a),

.B(b),

.C(c),

.P(p)

);

二、原语示例

主要参考pg148-dsp48 macro.pdf用到再细化补充。

Ex1:

// m = b * (a + d)

// p = c+m or p+m

`timescale 1ns / 1ps // m = b * (a + d)

// p = c+m or p+m

module dsp48_wrap_f

(

input clock,

input ce1,

input ce2,

input cem,

input cep,

input signed [24:0] a,

input signed [17:0] b,

input signed [47:0] c,

input signed [24:0] d, // this has two fewer pipe stages

// X+Y is usually the multiplier output (M)

// Z is either P, PCIN or C

// bit 1:0: 0: Z+X+Y 3:Z-(X+Y) 1: -Z + (X+Y) 2: -1*(Z+X+Y+1)

// bits 3:2, 0: Z=0, 1: Z=PCIN, 2: Z=P, 3: Z = C

// bit 4: sub in pre add

input [4:0] mode,

input signed [47:0] pcin,

output signed [47:0] pcout,

output signed [47-S:0] p); parameter S = 0; parameter USE_DPORT = "FALSE"; // enabling adds 1 reg to A path

parameter AREG = 1;

parameter BREG = 1; // 0 - 2 wire signed [47:0] dsp_p;

assign p = dsp_p[47:S]; DSP48E1

#(

.A_INPUT("DIRECT"), // "DIRECT" "CASCADE"

.B_INPUT("DIRECT"), // "DIRECT" "CASCADE"

.USE_DPORT(USE_DPORT),

.USE_MULT("MULTIPLY"),// "MULTIPLY" "DYNAMIC" "NONE"

.USE_SIMD("ONE48"), // "ONE48" "TWO24" "FOUR12"

// pattern detector - not used

.AUTORESET_PATDET("NO_RESET"), .MASK(48'h3fffffffffff),

.PATTERN(48'h000000000000), .SEL_MASK("MASK"),

.SEL_PATTERN("PATTERN"), .USE_PATTERN_DETECT("NO_PATDET"),

// register enables

.ACASCREG(1), // pipeline stages between A/ACIN and ACOUT (0, 1 or 2)

.ADREG(1), // pipeline stages for pre-adder (0 or 1)

.ALUMODEREG(1), // pipeline stages for ALUMODE (0 or 1)

.AREG(AREG), // pipeline stages for A (0, 1 or 2)

.BCASCREG(1), // pipeline stages between B/BCIN and BCOUT (0, 1 or 2)

.BREG(BREG), // pipeline stages for B (0, 1 or 2)

.CARRYINREG(1), // this and below are 0 or 1

.CARRYINSELREG(1),

.CREG(1),

.DREG(1),

.INMODEREG(1),

.MREG(1),

.OPMODEREG(1),

.PREG(1))

dsp48_i

(

// status

.OVERFLOW(),

.PATTERNDETECT(), .PATTERNBDETECT(),

.UNDERFLOW(),

// outs

.CARRYOUT(),

.P(dsp_p),

// control

.ALUMODE({2'd0, mode[1:0]}),

.CARRYINSEL(3'd0),

.CLK(clock),

.INMODE({1'b0,mode[4],3'b100}),

.OPMODE({1'b0,mode[3:2],4'b0101}),

// signal inputs

.A({5'd0,a}), // 30

.B(b), // 18

.C(c), // 48

.CARRYIN(1'b0),

.D(d), // 25

// cascade ports

.ACOUT(),

.BCOUT(),

.CARRYCASCOUT(),

.MULTSIGNOUT(),

.PCOUT(pcout),

.ACIN(30'h0),

.BCIN(18'h0),

.CARRYCASCIN(1'b0),

.MULTSIGNIN(1'b0),

.PCIN(pcin),

// clock enables

.CEA1(ce1), .CEA2(ce2),

.CEAD(1'b1),

.CEALUMODE(1'b1),

.CEB1(ce1), .CEB2(ce2),

.CEC(1'b1),

.CECARRYIN(1'b1),

.CECTRL(1'b1), // opmode

.CED(1'b1),

.CEINMODE(1'b1),

.CEM(cem), .CEP(cep),

.RSTA(1'b0),

.RSTALLCARRYIN(1'b0),

.RSTALUMODE(1'b0),

.RSTB(1'b0),

.RSTC(1'b0),

.RSTCTRL(1'b0),

.RSTD(1'b0),

.RSTINMODE(1'b0),

.RSTM(1'b0),

.RSTP(1'b0)

); endmodule // dsp48_wrap_f

Ex2:

/ /p = c + b * a 3 cycles if r else p = p + b * a

// p = c + b * a 3 cycles if r else p = p + b * a

module macc

(

input clock,

input [2:0] ce, // bit 0 = a, 1 = b , 2 = c

input r, // reset accumulator to c + a*b

input signed [24:0] a,

input signed [17:0] b,

input signed [47:0] c,

output signed [47-S:0] p; parameter S = 0;

parameter AREG = 1; // 0 - 2

parameter BREG = 1; // 0 - 2 wire signed [47:0] dsp_p;

assign p = dsp_p[47:S]; // X+Y is usually the multiplier output (M)

// Z is either P, PCIN or C

// bit 1:0: 0: Z+X+Y 3:Z-(X+Y) 1: -Z + (X+Y) 2: -1*(Z+X+Y+1)

// bits 3:2, 0: Z=0, 1: Z=PCIN, 2: Z=P, 3: Z = C

// bit 4: sub in pre add

wire [4:0] mode = {1'b0, r ? 2'b11 : 2'b10, 2'b00}; DSP48E1

#(

.A_INPUT("DIRECT"), // "DIRECT" "CASCADE"

.B_INPUT("DIRECT"), // "DIRECT" "CASCADE"

.USE_DPORT("FALSE"),

.USE_MULT("MULTIPLY"),// "MULTIPLY" "DYNAMIC" "NONE"

.USE_SIMD("ONE48"), // "ONE48" "TWO24" "FOUR12"

// pattern detector - not used

.AUTORESET_PATDET("NO_RESET"), .MASK(48'h3fffffffffff),

.PATTERN(48'h000000000000), .SEL_MASK("MASK"),

.SEL_PATTERN("PATTERN"), .USE_PATTERN_DETECT("NO_PATDET"),

// register enables

.ACASCREG(1), // pipeline stages between A/ACIN and ACOUT (0, 1 or 2)

.ADREG(1), // pipeline stages for pre-adder (0 or 1)

.ALUMODEREG(1), // pipeline stages for ALUMODE (0 or 1)

.AREG(AREG), // pipeline stages for A (0, 1 or 2)

.BCASCREG(1), // pipeline stages between B/BCIN and BCOUT (0, 1 or 2)

.BREG(BREG), // pipeline stages for B (0, 1 or 2)

.CARRYINREG(1), // this and below are 0 or 1

.CARRYINSELREG(1),

.CREG(1),

.DREG(1),

.INMODEREG(1),

.MREG(1),

.OPMODEREG(1),

.PREG(1))

dsp48_i

(

// status

.OVERFLOW(),

.PATTERNDETECT(), .PATTERNBDETECT(),

.UNDERFLOW(),

// outs

.CARRYOUT(),

.P(dsp_p),

// control

.ALUMODE({2'd0, mode[1:0]}),

.CARRYINSEL(3'd0),

.CLK(clock),

.INMODE({1'b0,mode[4],3'b100}),

.OPMODE({1'b0,mode[3:2],4'b0101}),

// signal inputs

.A({5'd0,a}), // 30

.B(b), // 18

.C(c), // 48

.CARRYIN(1'b0),

.D(25'd0), // 25

// cascade ports

.ACOUT(),

.BCOUT(),

.CARRYCASCOUT(),

.MULTSIGNOUT(),

.PCOUT(),

.ACIN(30'h0),

.BCIN(18'h0),

.CARRYCASCIN(1'b0),

.MULTSIGNIN(1'b0),

.PCIN(48'h0),

// clock enables

.CEA1(1'b1), .CEA2(ce[0]),

.CEAD(1'b1),

.CEALUMODE(1'b1),

.CEB1(1'b1), .CEB2(ce[1]),

.CEC(ce[2]),

.CECARRYIN(1'b1),

.CECTRL(1'b1), // opmode

.CED(1'b1),

.CEINMODE(1'b1),

.CEM(1'b1), .CEP(1'b1),

.RSTA(1'b0),

.RSTALLCARRYIN(1'b0),

.RSTALUMODE(1'b0),

.RSTB(1'b0),

.RSTC(1'b0),

.RSTCTRL(1'b0),

.RSTD(1'b0),

.RSTINMODE(1'b0),

.RSTM(1'b0),

.RSTP(1'b0)

); endmodule

Ex3:(35bit * 25bit,级联)

// wide multiply using 2x DSP48E1

// p = ((a * b) + c), 4 clock pipe delay

`timescale 1ns / 1ps // wide multiply using 2x DSP48E1

// p = ((a * b) + c), 4 clock pipe delay

module mult_35x25

(

input clock,

input signed [24:0] a,

input signed [34:0] b,

input signed [47:0] c,

output signed [64:0] p); wire signed [29:0] low_acout;

wire signed [47:0] low_pcout;

wire [47:0] p_low3;

reg [16:0] p_low4; DSP48E1 #(.A_INPUT("CASCADE"), .AREG(1), .BREG(2)) dsp48_high

(

// status

.OVERFLOW(), .PATTERNDETECT(), .PATTERNBDETECT(), .UNDERFLOW(),

// outs

.P(p[64:17]), .CARRYOUT(),

// control

.ALUMODE(4'b0), .CARRYINSEL(3'd0),

.CLK(clock),

.INMODE(5'b00000),

.OPMODE(7'b1010101), // a*b + pcin >> 17

// signal inputs

.A(30'b0), .B(b[34:17]), .C(48'b0), .CARRYIN(1'b0), .D(25'b0),

// cascade ports

.ACOUT(), .BCOUT(), .CARRYCASCOUT(), .MULTSIGNOUT(), .PCOUT(),

.ACIN(low_acout), .BCIN(18'h0), .CARRYCASCIN(1'b0), .MULTSIGNIN(1'b0),

.PCIN(low_pcout),

// clock enables, resets

.CEA1(1'b1), .CEA2(1'b1), .CEAD(1'b1), .CEALUMODE(1'b1),

.CEB1(1'b1), .CEB2(1'b1), .CEC(1'b1), .CECARRYIN(1'b1),

.CECTRL(1'b1), .CED(1'b1), .CEINMODE(1'b1), .CEM(1'b1), .CEP(1'b1),

.RSTA(1'b0), .RSTALLCARRYIN(1'b0), .RSTALUMODE(1'b0),

.RSTB(1'b0), .RSTC(1'b0), .RSTCTRL(1'b0), .RSTD(1'b0),

.RSTINMODE(1'b0), .RSTM(1'b0), .RSTP(1'b0)

); DSP48E1 #(.ACASCREG(1), .AREG(1), .BREG(1)) dsp48_low

(

// status

.OVERFLOW(), .PATTERNDETECT(), .PATTERNBDETECT(), .UNDERFLOW(),

// outs

.P(p_low3), .CARRYOUT(),

// control

.ALUMODE(4'b0), .CARRYINSEL(3'd0),

.CLK(clock),

.INMODE(5'b00000), .OPMODE(7'b0110101),

// signal inputs

.A({{5{a[24]}},a}), .B({1'b0,b[16:0]}),

.C(c),

.CARRYIN(1'b0),

.D(25'b0),

// cascade ports

.ACOUT(low_acout), .BCOUT(), .CARRYCASCOUT(), .MULTSIGNOUT(), .PCOUT(low_pcout),

.ACIN(30'h0), .BCIN(18'h0), .CARRYCASCIN(1'b0), .MULTSIGNIN(1'b0), .PCIN(48'h0),

// clock enables, resets

.CEA1(1'b1), .CEA2(1'b1), .CEAD(1'b1), .CEALUMODE(1'b1),

.CEB1(1'b1), .CEB2(1'b1), .CEC(1'b1), .CECARRYIN(1'b1),

.CECTRL(1'b1), .CED(1'b1), .CEINMODE(1'b1), .CEM(1'b1), .CEP(1'b1),

.RSTA(1'b0), .RSTALLCARRYIN(1'b0), .RSTALUMODE(1'b0),

.RSTB(1'b0), .RSTC(1'b0), .RSTCTRL(1'b0), .RSTD(1'b0),

.RSTINMODE(1'b0), .RSTM(1'b0), .RSTP(1'b0)

); always @ (posedge clock)

begin

p_low4 <= p_low3[16:0];

end assign p[16:0] = p_low4; initial

begin

$dumpfile("dump.vcd");

$dumpvars(0);

end endmodule

基础004_V7-DSP Slice的更多相关文章

- 【前端基础系列】slice方法将类数组转换数组实现原理

问题描述 在日常编码中会遇到将类数组对象转换为数组的问题,其中常用到的一种方式使用Array.prototype.slice()方法. 类数组对象 所谓的类数组对象,JavaScript对它们定义为: ...

- golang基础---Slice切片

切片Slice在go语言中是单独的类型(指向底层的数组),不同于python(对可迭代对象操作的工具),注意区分数组和slice的区别 定义一个空slice,格式var s []int,这种既没有长度 ...

- 基础008_定浮点转化[floating point IP]

作者:桂. 时间:2018-05-15 21:55:50 链接:http://www.cnblogs.com/xingshansi/p/9042564.html 前言 本文为Xilinx float ...

- 【不定期更新】FPGA/IC岗位常见笔试面试题总结(基础知识)

1 数字IC(ASIC)设计流程: IC设计分为前端和后端.前端设计主要将HDL语言-->网表,后端设计是网表-->芯片版图. 前端主要有需求分析与架构设计.RTL设计.仿真验证.逻辑综合 ...

- [转] 对Array.prototype.slice.call()方法的理解

在看别人代码时,发现有这么个写法:[].slice.call(arguments, 0),这到底是什么意思呢? 1.基础 1)slice() 方法可从已有的数组中返回选定的元素. start:必需.规 ...

- 对Array.prototype.slice.call()方法的理解

在看别人代码时,发现有这么个写法:[].slice.call(arguments, 0),这到底是什么意思呢? 1.基础 1)slice() 方法可从已有的数组中返回选定的元素. start:必需.规 ...

- TI DSP 6657 SRIO 简介

目录 TI DSP 6657 SRIO 简介 SRIO 协议介绍 RapidIO 基础 TI DSP 6657 SRIO 简介 SRIO 协议介绍 TI 的 KeyStone 系列设备中实现了 Rap ...

- 对Array.prototype.slice.call()方法的理解在看别人代码时,发现有这么个写法:[].slice.call(arguments, 0),这到底是什么意思呢?

1.基础 1)slice() 方法可从已有的数组中返回选定的元素. start:必需.规定从何处开始选取.如果是负数,那么它规定从数组尾部开始算起的位置.也就是说,-1 指最后一个元素,-2 指倒数第 ...

- 【转】DSP是什么--DSP是神马东东??

原文:http://www.eepw.com.cn/article/272908.htm 导读:本文主要介绍的是DSP是什么,不懂得童鞋们快随小编一起学习一下DSP到底是个神马东东吧! 本文引用地址: ...

- Array.prototype.slice.call()方法的理解

1.基础1)slice() 方法可从已有的数组中返回选定的元素. start:必需.规定从何处开始选取.如果是负数,那么它规定从数组尾部开始算起的位置.也就是说,-1 指最后一个元素,-2 指倒数第二 ...

随机推荐

- Spring学习笔记六:Spring整合Hibernate

转载请注明原文地址:http://www.cnblogs.com/ygj0930/p/6785323.html 前言:整合概述 Spring整合Hibernate主要是把Hibernate中常用的S ...

- vim note write

Try: :vert sb N which will open a left vertical split (by default, unless you have modified some opt ...

- Flash: Event.PASTE Flash获取剪贴板内容 触发paste事件 how to get paste event

actionscript把文字存放到剪贴板这个就非常简单了,一般网站做点击复制基本都是这么做的. 但是,基本没有人做flash粘贴内容.今天本来想尝试一下,通过flash实现网页编辑器粘贴图片,但貌似 ...

- phoneGap+jquery mobile项目经验

最近一个月,一直在用phoneGap+jquery mobile来开发一项目. 下面谈谈自己在开发过程中遇到的一些问题以及解决方法. 开始选择框架时,曾试过采用其他框架做UI,例如chocol ...

- Dom4j操作XML实战,解析和插入XML实例

本例子是用XML来代替数据库的,XML的每个节点代替数据库一行数据. 直说过程: XML文件结构:定义了一个名为:User.xml的文件: <?xml version="1.0&quo ...

- adjustResize和adjustPan的比较

在下面的描述中,编辑框的maxLine都设定为10. 在信息列表界面中,编辑框在RelativeLayout中定义.编辑框上边(above)的列表组件的高度不会缩小为0,导致显示出现一点问题. 当信息 ...

- ios中tableview侧栏的折叠

#import "ViewController.h" #define Ksmall 40.0f #define Klarge 80.0f #define KNoOpen @&quo ...

- java日期格式(年月日时分秒毫秒)

package test.remote.tools.combine; import java.text.SimpleDateFormat; import java.util.Calendar; imp ...

- 如何找出阻止windows睡眠的原因或软件

1.开始菜单 2.搜索程序和文件里输入 CMD 3.cmd.exe上右键点击以管理员权限运行 4.在cmd黑屏窗口里输入 powercfg -requests如下图所示

- iOS 10 的一个重要更新-自定义的通知界面

续上篇,在简单闹钟的例子上,在通知界面上显示图片动画,并用通知关联的按钮更新通知界面.介绍 iOS 10 通知 API 的扩展:自定义通知显示界面. 新框架可以统一处理本地通知和远程推送,同时增加了一 ...