SDRAM初始化

DDR配置过程比较复杂,基本上是按照DDR控制器的时序要求来做的,其中很多参数要结合DDR芯片本身的参数来定,还有些参数是时序参数,要去详细计算。所以DDR配置非常繁琐、细致、专业。所以我们对DDR初始化的态度就是:学会这种思路和方法,结合文档和代码能看懂,会算一些常见的参数即可。

.global sdram_asm_init sdram_asm_init:

ldr r0, =0xf1e00000

ldr r1, =0x0

str r1, [r0, #0x0] /* DMC0 Drive Strength (Setting 2X) */ ldr r0, =ELFIN_GPIO_BASE ldr r1, =0x0000AAAA

str r1, [r0, #MP1_0DRV_SR_OFFSET] // 寄存器中对应0b10,就是2X ldr r1, =0x0000AAAA

str r1, [r0, #MP1_1DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_2DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_3DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_4DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_5DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_6DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP1_7DRV_SR_OFFSET] ldr r1, =0x00002AAA

str r1, [r0, #MP1_8DRV_SR_OFFSET] /* DMC1 Drive Strength (Setting 2X) */ ldr r0, =ELFIN_GPIO_BASE ldr r1, =0x0000AAAA

str r1, [r0, #MP2_0DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_1DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_2DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_3DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_4DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_5DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_6DRV_SR_OFFSET] ldr r1, =0x0000AAAA

str r1, [r0, #MP2_7DRV_SR_OFFSET] ldr r1, =0x00002AAA

str r1, [r0, #MP2_8DRV_SR_OFFSET] /* DMC0 initialization at single Type*/

ldr r0, =APB_DMC_0_BASE ldr r1, =0x00101000 @PhyControl0 DLL parameter setting, manual 0x00101000

str r1, [r0, #DMC_PHYCONTROL0] ldr r1, =0x00000086 @PhyControl1 DLL parameter setting, LPDDR/LPDDR2 Case

str r1, [r0, #DMC_PHYCONTROL1] ldr r1, =0x00101002 @PhyControl0 DLL on

str r1, [r0, #DMC_PHYCONTROL0] ldr r1, =0x00101003 @PhyControl0 DLL start

str r1, [r0, #DMC_PHYCONTROL0] find_lock_val:

ldr r1, [r0, #DMC_PHYSTATUS] @Load Phystatus register value

and r2, r1, #0x7

cmp r2, #0x7 @Loop until DLL is locked

bne find_lock_val and r1, #0x3fc0

mov r2, r1, LSL #

orr r2, r2, #0x100000

orr r2 ,r2, #0x1000 orr r1, r2, #0x3 @Force Value locking

str r1, [r0, #DMC_PHYCONTROL0] #if /* Memory margin test .. */

orr r1, r2, #0x1 @DLL off

str r1, [r0, #DMC_PHYCONTROL0]

#endif

/* setting DDR2 */

ldr r1, =0x0FFF2010 @ConControl auto refresh off

str r1, [r0, #DMC_CONCONTROL] ldr r1, =DMC0_MEMCONTROL @MemControl BL=, chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL] ldr r1, =DMC0_MEMCONFIG_0 @MemConfig0 256MB config, banks,Mapping Method[:]:linear, :linterleaved, :Mixed

str r1, [r0, #DMC_MEMCONFIG0] ldr r1, =DMC0_MEMCONFIG_1 @MemConfig1

str r1, [r0, #DMC_MEMCONFIG1] ldr r1, =0xFF000000 @PrechConfig

str r1, [r0, #DMC_PRECHCONFIG] ldr r1, =DMC0_TIMINGA_REF @TimingAref .8us*133MHz=(0x40E), 100MHz=(0x30C), 20MHz=(0x9C), 10MHz=(0x4E)

str r1, [r0, #DMC_TIMINGAREF] ldr r1, =DMC0_TIMING_ROW @TimingRow for @200MHz

str r1, [r0, #DMC_TIMINGROW] ldr r1, =DMC0_TIMING_DATA @TimingData CL=

str r1, [r0, #DMC_TIMINGDATA] ldr r1, =DMC0_TIMING_PWR @TimingPower

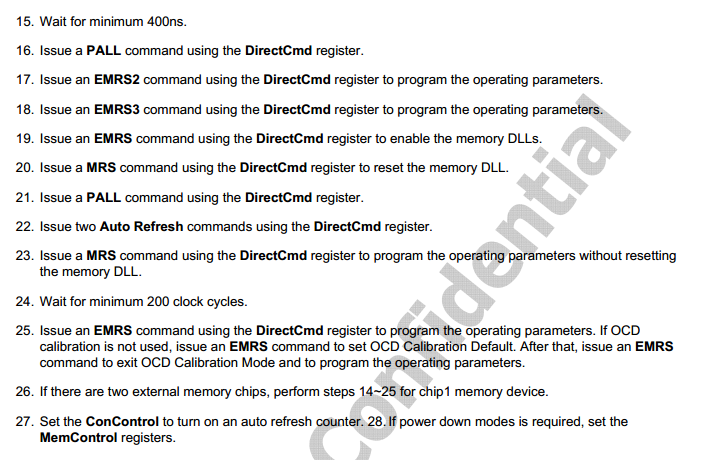

str r1, [r0, #DMC_TIMINGPOWER] ldr r1, =0x07000000 @DirectCmd chip0 Deselect

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00020000 @DirectCmd chip0 EMRS2

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00030000 @DirectCmd chip0 EMRS3

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00000542 @DirectCmd chip0 MRS (MEM DLL reset) CL=, BL=

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01000000 @DirectCmd chip0 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05000000 @DirectCmd chip0 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00000442 @DirectCmd chip0 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00010780 @DirectCmd chip0 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00010400 @DirectCmd chip0 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x07100000 @DirectCmd chip1 Deselect

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00120000 @DirectCmd chip1 EMRS2

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00130000 @DirectCmd chip1 EMRS3

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (MEM DLL on, DQS# disable)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00100542 @DirectCmd chip1 MRS (MEM DLL reset) CL=, BL=

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x01100000 @DirectCmd chip1 PALL

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x05100000 @DirectCmd chip1 REFA

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00100442 @DirectCmd chip1 MRS (MEM DLL unreset)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00110780 @DirectCmd chip1 EMRS1 (OCD default)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x00110400 @DirectCmd chip1 EMRS1 (OCD exit)

str r1, [r0, #DMC_DIRECTCMD] ldr r1, =0x0FF02030 @ConControl auto refresh on

str r1, [r0, #DMC_CONCONTROL] ldr r1, =0xFFFF00FF @PwrdnConfig

str r1, [r0, #DMC_PWRDNCONFIG] ldr r1, =0x00202400 @MemControl BL=, chip, DDR2 type, dynamic self refresh, force precharge, dynamic power down off

str r1, [r0, #DMC_MEMCONTROL] // 上面是DRAM0初始化步骤

SDRAM初始化的更多相关文章

- SDRAM的初始化与刷新操作---看时序图写代码

SDRAM的初始化与刷新操作---看时序图写代码 1.SDRAM的常见操作 2.初始化就是配置SDRAM 3.SDRAM初始化时序 时序解释如下: 4.刷新操作

- ARM裸板开发:04_MMU 链接地址与运行地址不一致时,(SDRAM)初始化程序地址无关码问题的分析

ARM裸板开发过程,程序的链接地址设置为为0x30000000,而前期的启动代码以及相关硬件的初始化代码需要在内部iRAM(steppingstone,起始地址0x0)的4K中运行.链接地址与运行地址 ...

- SDRAM学习(二)之初始化

目录 1.SDRAM初始化的内容(结合英文数据手册) 2.SDRAM初始化的时序 3.代码的编写 4.modesim的仿真 SDRAM初始化的内容 SDRAMs must be powered up ...

- SDRAM和dcfifo的联合

SDRAM和dcfifo的联合 设计原理 在"SDRAM突发读写页"实验中,留下了一个问题,就是从SDRAM读取数据的速度要与SDRAM的驱动时钟同步,这就造成了读出的数据的速率过 ...

- SDRAM读写一字(下)

SDRAM读写一字 SDRAM控制模块 上电后进行初始化状态,初始化完成后进入空闲状态,在此进行判断如下判断: 如果自刷新时间到,则进行自刷新操作,操作完成后重新进入空闲状态: 如果读使能有效则进行读 ...

- SDRAM读写一字(上)

SDRAM读写一字 系统设计 SDRAM指令 指令 常量名 CKE CSn RAS CASn WEn 备注 空操作 NOP 1 0 1 1 1 行激活 ACTIVE 1 0 0 1 1 读操作 ...

- Smart210学习记录-------内存初始化

买了Smart210的板子,开始学习中,,,,, 今天看了重定位DRAM ,然而内存需要初始化,早上信心满满的我到现在崩溃的我....也不知遭受了什么样的蹂躏 ,,还是记下一点学到的知识吧.. 数据手 ...

- Tiny6410之重定位代码到SDRAM

在上一章中,将代码重定位到了SRAM中,但是这样的做法作用不大.正确的做法的是将代码重定位到更大的主存中,即DRAM.Tiny6410的DRAM控制寄存器最多只能支持两个同一类型的芯片.每个芯片最多可 ...

- 第2阶段——编写uboot之硬件初始化和制作链接脚本lds(1)

目标: 1.关看门狗 2.设置时钟 3.初始化SDRAM (初始化寄存器以及清除bss段) 4.重定位 (将nand/nor中代码COPY到链接地址上,需要初始化nandflash,读flash) 5 ...

随机推荐

- 实现Bidirectional LSTM Classifier----深度学习RNN

双向循环神经网络(Bidirectional Recurrent Neural Networks,Bi-RNN),Schuster.Paliwal,1997年首次提出,和LSTM同年.Bi-RNN,增 ...

- tensorflow学习笔记(4)-学习率

tensorflow学习笔记(4)-学习率 首先学习率如下图 所以在实际运用中我们会使用指数衰减的学习率 在tf中有这样一个函数 tf.train.exponential_decay(learning ...

- Tic-Tac-Toe

Description Kim likes to play Tic-Tac-Toe. Given a current state, and now Kim is going to take his n ...

- TensorFlow源码框架 杂记

一.为什么我们需要使用线程池技术(ThreadPool) 线程:采用“即时创建,即时销毁”策略,即接受请求后,创建一个新的线程,执行任务,完毕后,线程退出: 线程池:应用软件启动后,立即创建一定数量的 ...

- 算法与数据结构实验题 6.4 Summary

★实验任务 可怜的 Bibi 丢了好几台手机以后,看谁都像是小偷,他已经在小本本上记 下了他认为的各个地点的小偷数量. 现在我们将 Bibi 的家附近的地形抽象成一棵有根树.每个地点都是树上的 一个节 ...

- Java中I/O流之数据流

Java 中的数据流: 对于某问题:将一个 long 类型的数据写到文件中,有办法吗? 转字符串 → 通过 getbytes() 写进去,费劲,而且在此过程中 long 类型的数需要不断地转换. ...

- java的参数传递

1按值传递:传递的是原始值的副本,而不是原始值的内存地址 基本数据类型是传原始值的副本 class Test02 { public static void main(String[] args) { ...

- LintCode-35.翻转链表

翻转链表 翻转一个链表 样例 给出一个链表 1->2->3->null ,这个翻转后的链表为 3->2->1->null 挑战 在原地一次翻转完成 标签 链表 优步 ...

- lintcode-14-二分查找

二分查找 给定一个排序的整数数组(升序)和一个要查找的整数target,用O(logn)的时间查找到target第一次出现的下标(从0开始),如果target不存在于数组中,返回-1. 样例 在数组 ...

- IPReversePathFilter

nstat TcpExtIPReversePathFilter for i in /proc/sys/net/ipv4/conf/*/rp_filter ; do > echo 0 > $ ...