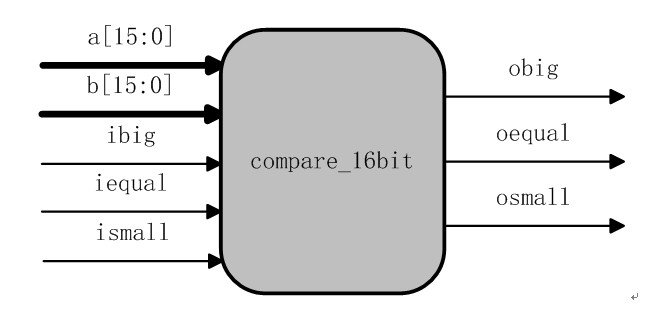

基于FPGA的16位带级联信号数值比较器设计

1.项目介绍

数值比较器就是对两数A、B进行比较,以判断其大小的逻辑电路。

2. 设计要求:

(1)设计一个16位比较器,比较两个数a和b的大小,有三个输出端(大于、小于或等于)。当a大于b,则obig=1,其余为0;当a小于b,则osmall=1,其余为0;当a等于b时,则oequal=1,其余为0。

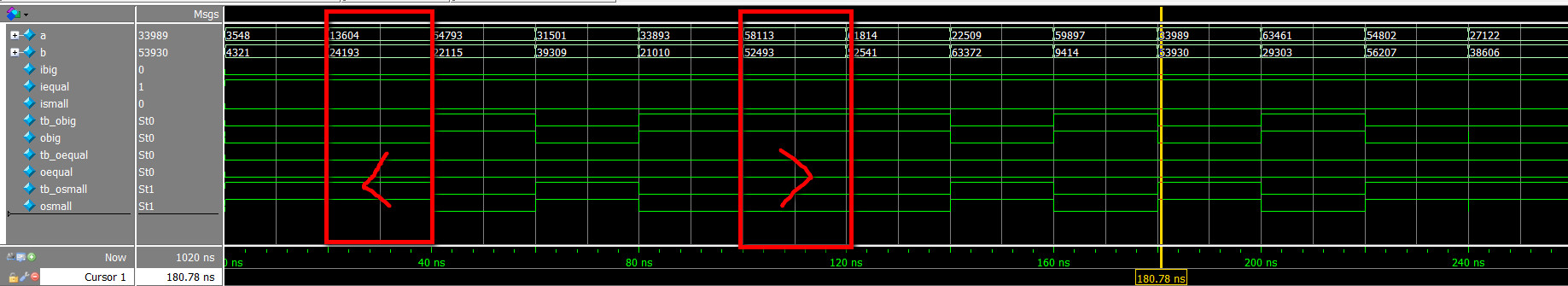

(2)写出测试模块,随机产生两个16位输入数据,每隔20ns产生两个新的随机数,观察仿真波形,并对仿真波形做分析,说明设计的正确性。

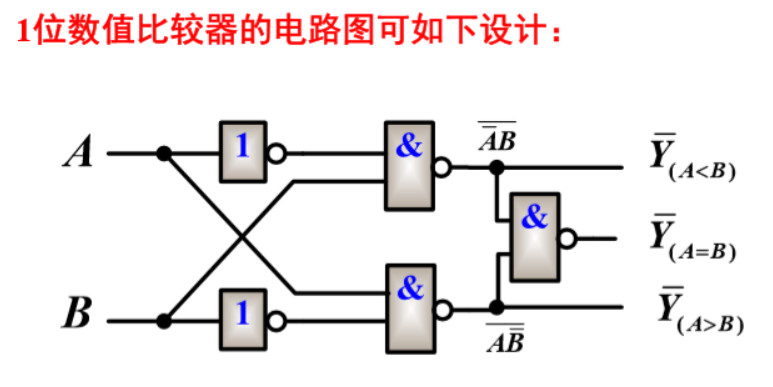

3.实验原理

在比较两个多位数的大小时,必须自高而低的逐位比较,而且只有在高位相等时,才需比较较低位。该设计命名为compare_16bit,a[15:0]和b[15:0]为比较数值,ibig (A>B)、iequal(A=B)、ismall(A<B)为级联信号,用来将高位的结果与低位级联,即接收来自高位比较器的输出结果。若级联信号ibig(A>B)==1或者ismall(A<B)==1,即高位不相等,则无需比较低位;若级联信号iequal(A=B)==1,最终结果取决于低位结果。

4. 设计实现

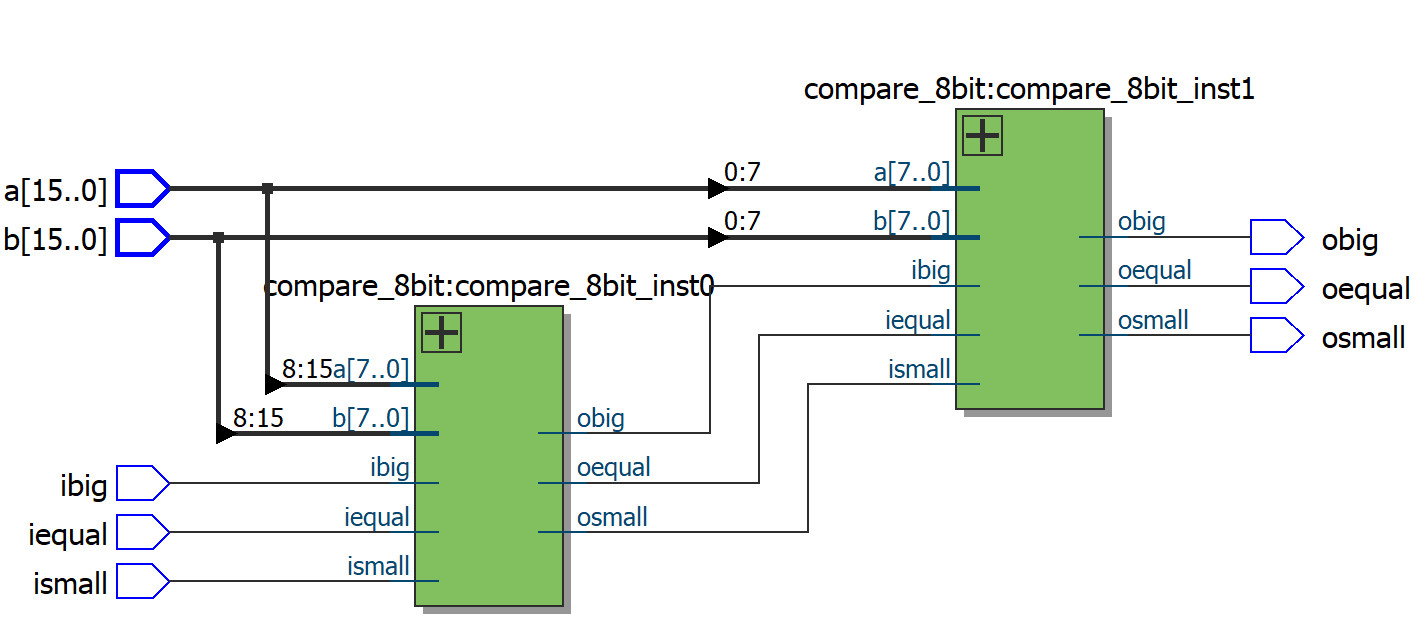

(1)16位数据比较器由2个8位数据比较器构成

1 module compare_16bit(

2

3 input wire [15:0] a,

4 input wire [15:0] b,

5 input wire ibig,

6 input wire iequal,

7 input wire ismall,

8

9 output wire obig,

10 output wire oequal,

11 output wire osmall

12 );

13

14 wire obig8;

15 wire oequal8;

16 wire osmall8;

17

18

19 compare_8bit compare_8bit_inst0(

20

21 .a (a[15:8]),

22 .b (b[15:8]),

23 .ibig (ibig),

24 .iequal (iequal),

25 .ismall (ismall),

26

27 .obig (obig8),

28 .oequal (oequal8),

29 .osmall (osmall8)

30 );

31

32 compare_8bit compare_8bit_inst1(

33

34 .a (a[7:0]),

35 .b (b[7:0]),

36 .ibig (obig8),

37 .iequal (oequal8),

38 .ismall (osmall8),

39

40 .obig (obig),

41 .oequal (oequal),

42 .osmall (osmall)

43 );

44

45 endmodule

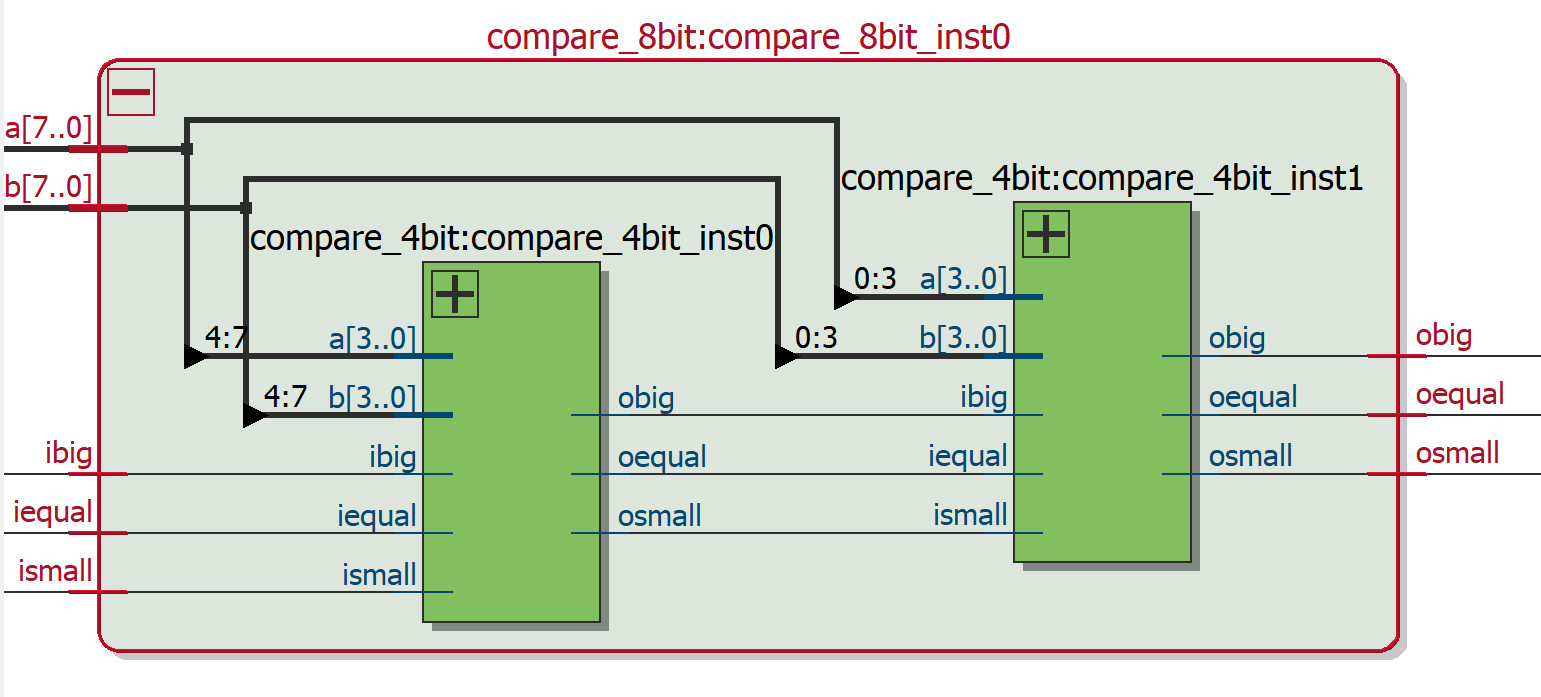

(2)8位数值比较器由2个4位数据比较器构成

1 module compare_8bit(

2

3 input wire [7:0] a,

4 input wire [7:0] b,

5 input wire ibig,

6 input wire iequal,

7 input wire ismall,

8

9 output wire obig,

10 output wire oequal,

11 output wire osmall

12 );

13

14 wire obig4;

15 wire oequal4;

16 wire osmall4;

17

18 compare_4bit compare_4bit_inst0(

19

20 .a (a[7:4]),

21 .b (b[7:4]),

22 .ibig (ibig),

23 .iequal (iequal),

24 .ismall (ismall),

25

26 .obig (obig4),

27 .oequal (oequal4),

28 .osmall (osmall4)

29 );

30

31 compare_4bit compare_4bit_inst1(

32

33 .a (a[3:0]),

34 .b (b[3:0]),

35 .ibig (obig4),

36 .iequal (oequal4),

37 .ismall (osmall4),

38

39 .obig (obig),

40 .oequal (oequal),

41 .osmall (osmall)

42 );

43

44 endmodule

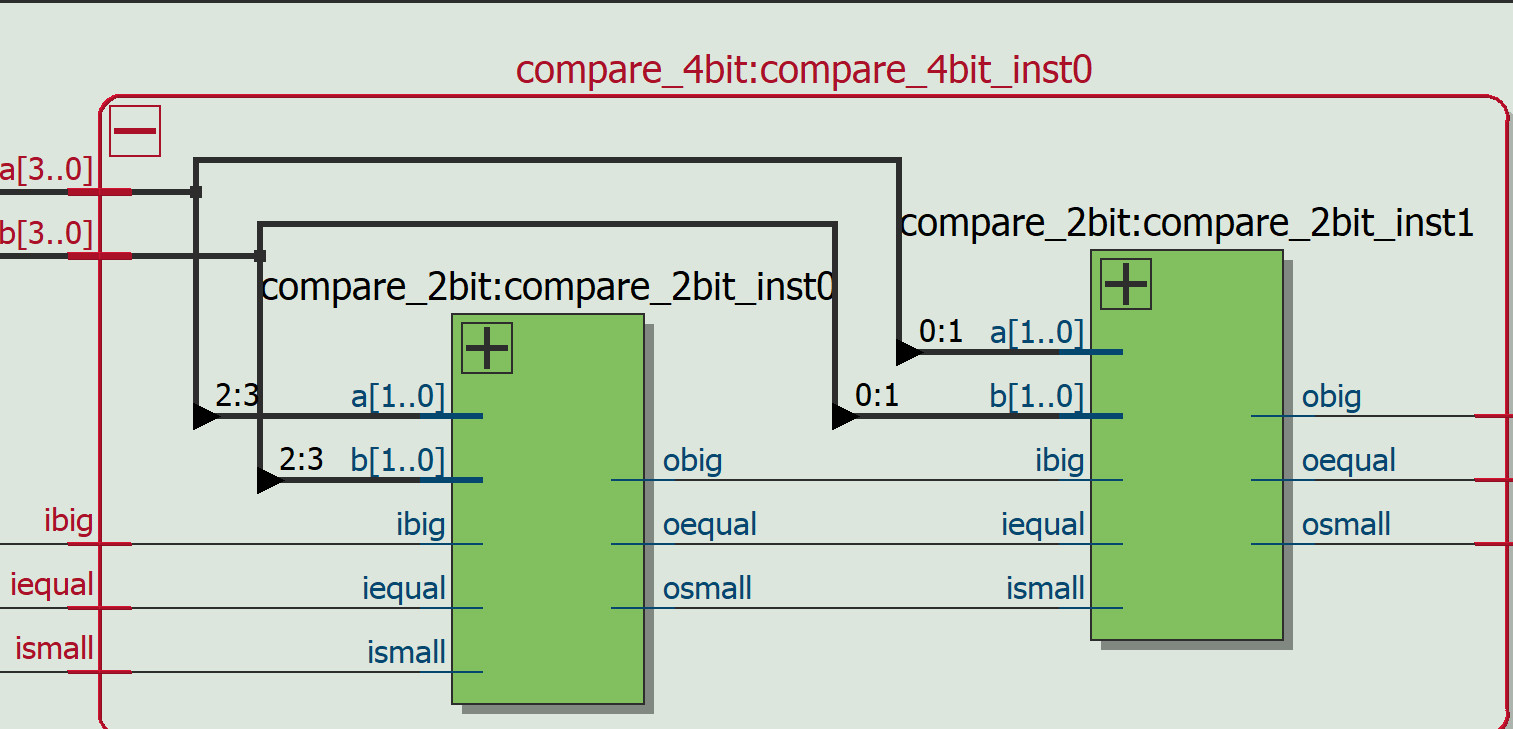

(3)4位数值比较器由2个2位数据比较器构成

1 module compare_4bit(

2

3 input wire [3:0] a,

4 input wire [3:0] b,

5 input wire ibig,

6 input wire iequal,

7 input wire ismall,

8

9 output wire obig,

10 output wire oequal,

11 output wire osmall

12 );

13

14 wire obig2;

15 wire oequal2;

16 wire osmall2;

17

18

19 compare_2bit compare_2bit_inst0(

20

21 .a (a[3:2]),

22 .b (b[3:2]),

23 .ibig (ibig),

24 .iequal (iequal),

25 .ismall (ismall),

26

27 .obig (obig2),

28 .oequal (oequal2),

29 .osmall (osmall2)

30 );

31

32 compare_2bit compare_2bit_inst1(

33

34 .a (a[1:0]),

35 .b (b[1:0]),

36 .ibig (obig2),

37 .iequal (oequal2),

38 .ismall (osmall2),

39

40 .obig (obig),

41 .oequal (oequal),

42 .osmall (osmall)

43 );

44

45 endmodule

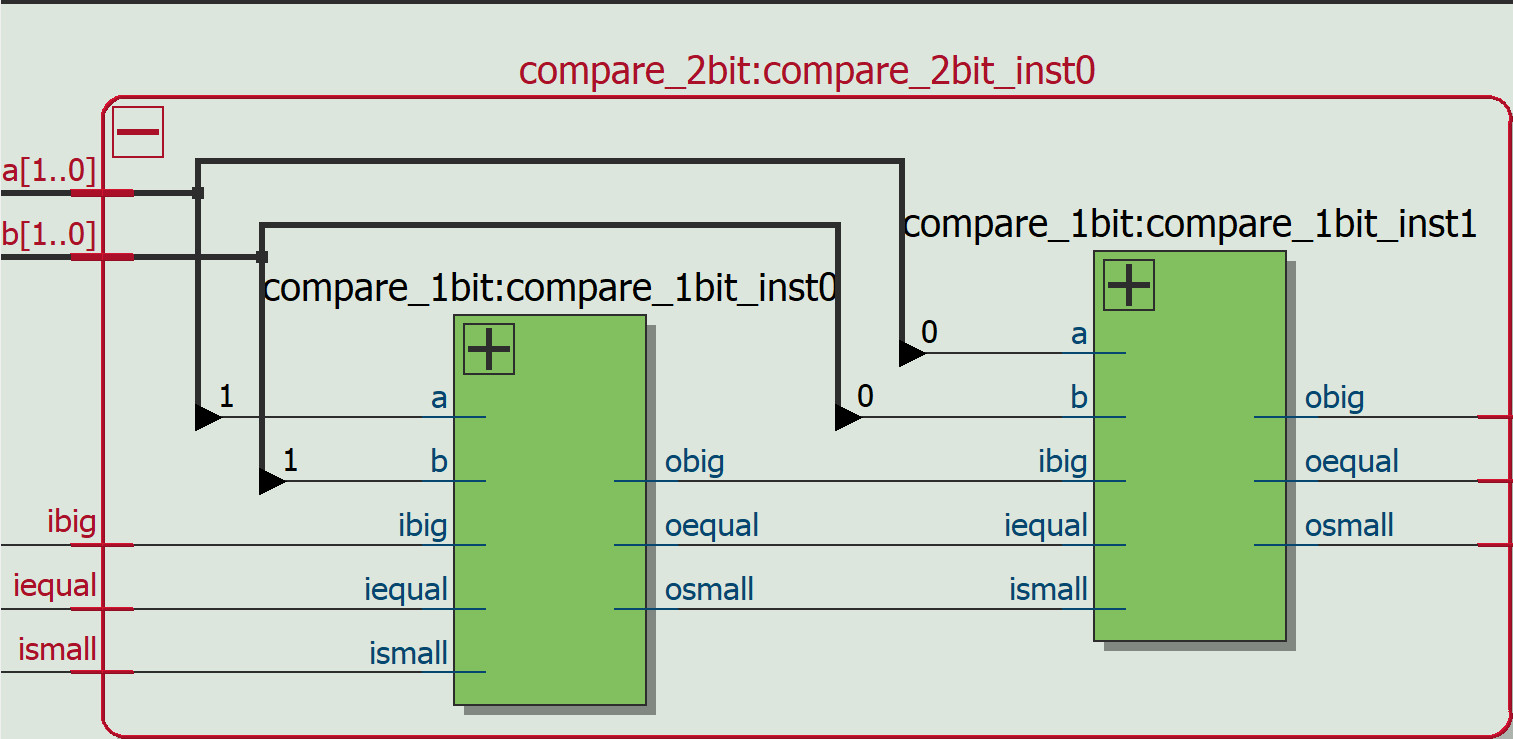

(4)2位数值比较器由2个1位数据比较器构成

1 module compare_2bit(

2

3 input wire [1:0] a,

4 input wire [1:0] b,

5 input wire ibig,

6 input wire iequal,

7 input wire ismall,

8

9 output wire obig,

10 output wire oequal,

11 output wire osmall

12 );

13

14 wire obig_reg;

15 wire oequal_reg;

16 wire osmall_reg;

17

18

19 compare_1bit compare_1bit_inst0(

20

21 .a (a[1]),

22 .b (b[1]),

23 .ibig (ibig),

24 .iequal (iequal),

25 .ismall (ismall),

26

27 .obig (obig_reg),

28 .oequal (oequal_reg),

29 .osmall (osmall_reg)

30 );

31

32 compare_1bit compare_1bit_inst1(

33

34 .a (a[0]),

35 .b (b[0]),

36 .ibig (obig_reg),

37 .iequal (oequal_reg),

38 .ismall (osmall_reg),

39

40 .obig (obig),

41 .oequal (oequal),

42 .osmall (osmall)

43 );

44

45 endmodule

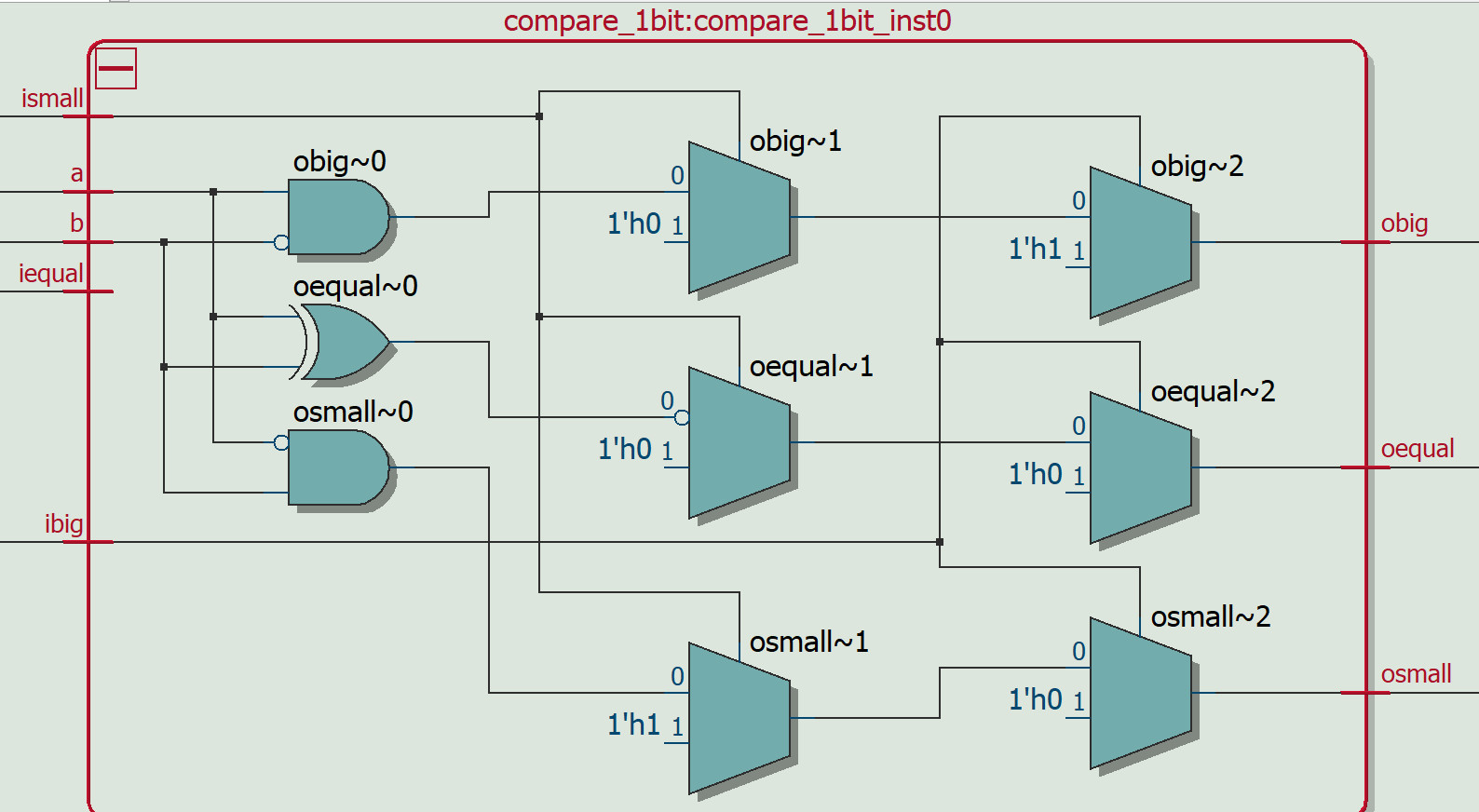

(5)1位带级联信号的数值比较器

1 module compare_1bit(

2

3 input wire a,

4 input wire b,

5 input wire ibig,

6 input wire iequal,

7 input wire ismall,

8

9 output reg obig,

10 output reg oequal,

11 output reg osmall

12 );

13

14 always@(*)begin

15 if(ibig == 1'b1)

16 obig = 1'b1;

17 else

18 if(ismall == 1'b1)

19 obig = 1'b0;

20 else

21 obig = a & (~b);

22 end

23

24 always@(*)begin

25 if(ibig == 1'b1)

26 oequal = 1'b0;

27 else

28 if(ismall == 1'b1)

29 oequal = 1'b0;

30 else

31 oequal = ~(a ^ b);

32 end

33

34 always@(*)begin

35 if(ibig == 1'b1)

36 osmall = 1'b0;

37 else

38 if(ismall == 1'b1)

39 osmall = 1'b1;

40 else

41 osmall = (~a) & b;

42 end

43

44 endmodule

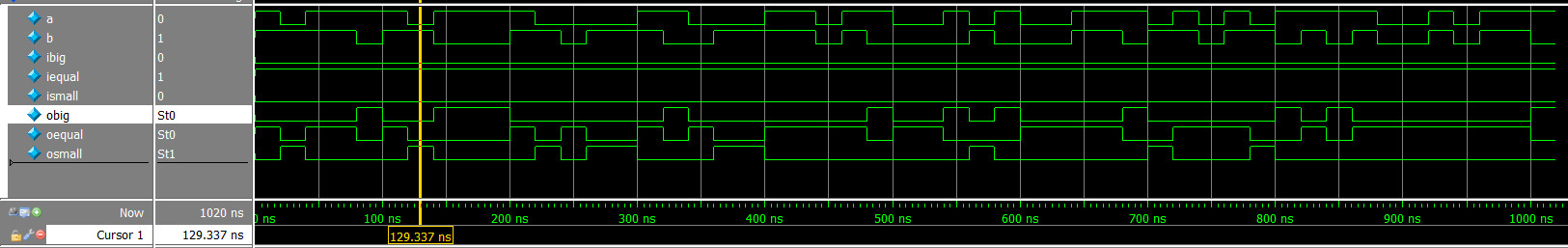

4. 验证仿真

(1)1位带级联信号的数值比较器(不考虑高位影响,假设高位都相等)

1 `timescale 1ns/1ps

2

3 module compare_1bit_tb();

4

5 reg a;

6 reg b;

7 reg ibig;

8 reg iequal;

9 reg ismall;

10

11 wire obig;

12 wire oequal;

13 wire osmall;

14

15

16 compare_1bit compare_1bit_inst(

17

18 .a (a),

19 .b (b),

20 .ibig (ibig),

21 .iequal (iequal),

22 .ismall (ismall),

23

24 .obig (obig),

25 .oequal (oequal),

26 .osmall (osmall)

27 );

28

29 initial begin

30 a = 1'b1; b = 1'b1;

31 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0; //不考虑高位的影响

32 #20;

33 repeat(50)begin

34 a = {$random}%2; b = {$random}%2;

35 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0;

36 #20;

37 end

38 end

39

40 endmodule

(2)16位带级联信号的数值比较器

1 `timescale 1ns/1ps

2

3 module compare_16bit_tb();

4

5 reg [15:0] a;

6 reg [15:0] b;

7 reg ibig;

8 reg iequal;

9 reg ismall;

10

11 wire obig;

12 wire oequal;

13 wire osmall;

14

15 wire tb_obig;

16 wire tb_oequal;

17 wire tb_osmall;

18

19 assign tb_obig = a > b;

20 assign tb_oequal = a == b;

21 assign tb_osmall = a < b;

22

23 compare_16bit compare_16bit_inst(

24

25 .a (a),

26 .b (b),

27 .ibig (ibig),

28 .iequal (iequal),

29 .ismall (ismall),

30

31 .obig (obig),

32 .oequal (oequal),

33 .osmall (osmall)

34 );

35

36 initial begin

37 a = 16'd3548; b = 16'd4321;

38 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0; //不考虑高位的影响

39 #20;

40 repeat(50)begin

41 a = {$random}%65536; b = {$random}%65536;

42 ibig = 1'b0; iequal = 1'b1; ismall = 1'b0;

43 #20;

44 end

45 end

46

47 endmodule

5. 参考资料

(1)陪您一起学习FPGA-郝旭帅团队_哔哩哔哩_bilibili

(2)(43条消息) (十三)【数电】(组合逻辑电路)比较器和奇偶校检器_二进制 人工智能的博客-CSDN博客

基于FPGA的16位带级联信号数值比较器设计的更多相关文章

- 基于FPGA的16阶级联型iir带通滤波器实现

警告 此文章将耗费你成吨的流量,请wifi下阅读,造成的流量浪费本人不承担任何责任.初版源代码获取(请勿用作他用,仅供学习):https://gitee.com/kingstacker/iir.git ...

- 基于FPGA的HDTV视频图像灰度直方图统计算法设计

随着HDTV的普及,以LCD-TV为主的高清数字电视逐渐进入蓬勃发展时期.与传统CRT电视不同的是,这些高清数字电视需要较复杂的视频处理电路来驱动,比如:模数转换(A/D Converter).去隔行 ...

- verilog实现16位五级流水线的CPU带Hazard冲突处理

verilog实现16位五级流水线的CPU带Hazard冲突处理 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4292869.html所增加的Hazard处 ...

- FMC145-四路16位125Msps AD FMC子卡模块 模拟信号 中频信号采集 信号发出

FMC145-四路16位125Msps AD FMC子卡模块 一.概述 该板卡可实现4路16bit 125Msps AD 功能,是xilinx开发板设计的标准板卡.FMC连接器是一种高速多pin的互连 ...

- 关于FPGA设计16位乘法器的两…

原文地址:关于FPGA设计16位乘法器的两种算法作者:ChrisChan 部分原代码如下: 用特权的右移算法虽复杂点,但节省不少LEs,如下图: 用左移算法尽管浅显易懂,但因每次都会从最右端移位,会占 ...

- 《汇编语言 基于x86处理器》第十章 - 运行一个 16位实地址汇编程序

▶ 书上第 10 章,主要讲了宏,引用了一个 16 位实地址的程序,从代码开始到运行 ● 代码 ; main.asm INCLUDE Macros.inc IF IsDefined( RealMode ...

- 基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)

1 设计内容 本设计是基于FPGA的音频信号FIR低通滤波,根据要求,采用Matlab对WAV音频文件进行读取和添加噪声信号.FFT分析.FIR滤波处理,并分析滤波的效果.通过Matlab的分析验证滤 ...

- 基于FPGA的线阵CCD实时图像采集系统

基于FPGA的线阵CCD实时图像采集系统 2015年微型机与应用第13期 作者:章金敏,张 菁,陈梦苇2016/2/8 20:52:00 关键词: 实时采集 电荷耦合器件 现场可编程逻辑器件 信号处理 ...

- 基于FPGA的PCIe接口实现(具体讲解了数据流向)

时间:2014-12-09 来源:西安电子科技大学电子工程学院 作者:姜 宁,陈建春,王 沛,石 婷 摘要 PCI Express是一种高性能互连协议,被广泛应用于网络适配.图形加速器.网络存储.大数 ...

- FMC228- 四路16位1.2Gsps DA FMC子卡模块

FMC228- 四路16位1.2Gsps DA FMC子卡模块 一.概述 FMC连接器是一种高速多pin的互连器件,广泛应用于板卡对接的设备中,特别是在xilinx公司的所有开发板中 ...

随机推荐

- 你应该懂的AI大模型(八)之 微调 之 增量微调

一.什么是微调 1.1.什么是微调?为什么要做微调? 模型微调(Fine-tuning)指的是将一个预训练好的模型(通常在大规模通用数据集上训练)针对特定任务或领域进行优化的过程. 那么什么是预训练好 ...

- CentOS云服务器WordPress搭建(BT.CN)

该随笔为大学时期的建站记录,图片等等,由于域名到期,七牛云回收资源,图床失效等等,已无法考究,语雀也没法恢复文档,仅作为参考用. 此教程适用于国内的建站,英文外贸建站请移步购买位于国外的服务器[外贸建 ...

- 十、buildroot系统 桌面配置

4.4.桌面控制 4.4.1.weston 文件夹路径 /common/overlays/10-weston 1.核心设置 配置 Weston 的核心设置 文件 /etc/xdg/weston/wes ...

- ChatGPT学习之旅 (1) 初步了解ChatGPT

大家好,我是Edison. 之前说过,我们即将开始一段AIGC学习之旅,从ChatGPT到Github Copilot再到Semantic Kernel,第一站是ChatGPT.在这一站,我们花一点时 ...

- AWTK 嵌入式Linux平台实现多点触控缩放旋转以及触点丢点问题解决

前言 最近涉及海图的功能交互,多点触摸又开始找麻烦. 在PC/Web平台awtk是通过底层的sdl2库来实现多点触摸,但是在嵌入式Linux平台,可能是考虑到性能原因,awtk并没有采用sdl库来做事 ...

- vmware workstation 安装 Debian

下载安装 vmware workstation 本文中用的是 VMware Workstation Pro v17. 点击这里,跳转至下载页. 下载 debian 点击这里跳转官网下载. 创建一个虚拟 ...

- CF724G Xor-matic Number of the Graph 题解

CF724G Xor-matic Number of the Graph 直接维护异或和之和,显然不可能.由于二进制位相互独立,我们考虑维护每一个二进制位的出现次数,再乘以位权加入结果. 对于路径的维 ...

- 生成式对抗网络(GAN)模型原理概述

生成对抗网络(Generative Adversarial Network, GAN)是一种通过对抗训练生成数据的深度学习模型,由生成器(Generator)和判别器(Discriminator) ...

- 扩散模型(Diffusion Model)原理概述

一.核心思想 扩散模型(Diffusion Model)是一种生成模型,受热力学中扩散过程的启发,通过模拟数据从噪声中逐步去噪的过程来生成样本.其核心思想是渐进式地添加噪声(正向过程)和逐步去噪( ...

- TODO FIXME XXX 含义

转载: https://www.cnblogs.com/pengyingh/articles/2445826.html 代码里面增加的小注释. 实际上,在阅读一些开源代码时,我们常会碰到诸如:TODO ...