Verilog之SOS信号-仿顺序操作

SOS信号:. . . _ _ _ . . .

1.

module sos_module

(

CLK, RSTn, Pin_Out, SOS_En_Sig

); input CLK;

input RSTn;

input SOS_En_Sig;

output Pin_Out; /****************************************/ parameter T1MS = 'd49_999;//DB4CE15开发板使用的晶振为50MHz,50M*0.001-1=49_999 /***************************************/ reg [:]Count1; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count1 <= 'd0;

else if( isCount && Count1 == T1MS )

Count1 <= 'd0;

else if( isCount )

Count1 <= Count1 + 'b1;

else if( !isCount )

Count1 <= 'd0; /****************************************/ reg [:]Count_MS; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count_MS <= 'd0;

else if( isCount && Count1 == T1MS )

Count_MS <= Count_MS + 'b1;

else if( !isCount )

Count_MS <= 'd0; /******************************************/ reg isCount;

reg rPin_Out;

reg [:]i; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

begin

isCount <= 'b0;

rPin_Out <= 'b0;

i <= 'd0;

end

else

case( i ) 'd0 :

if( SOS_En_Sig ) i <= 'd1; 'd1, 5'd3, 'd5,

'd13, 5'd15, 'd17 :

if( Count_MS == 'd100 ) begin isCount <= 1'b0; rPin_Out <= 'b0; i <= i + 1'b1; end // short

else begin isCount <= 'b1; rPin_Out <= 1'b1; end 'd7, 5'd9, 'd11 :

if( Count_MS == 'd300 ) begin isCount <= 1'b0; rPin_Out <= 'b0; i <= i + 1'b1; end // long

else begin isCount <= 'b1; rPin_Out <= 1'b1; end 'd2, 5'd4, 'd6,

'd8, 5'd10, 'd12,

'd14, 5'd16, 'd18 :

if( Count_MS == 'd50 ) begin isCount <= 1'b0; i <= i + 'b1; end// interval

else isCount <= 'b1; 'd19 :

begin rPin_Out <= 'b0; i <= 5'd0; end // end endcase /***************************************************/ assign Pin_Out = rPin_Out; /***************************************************/ endmodule

2.

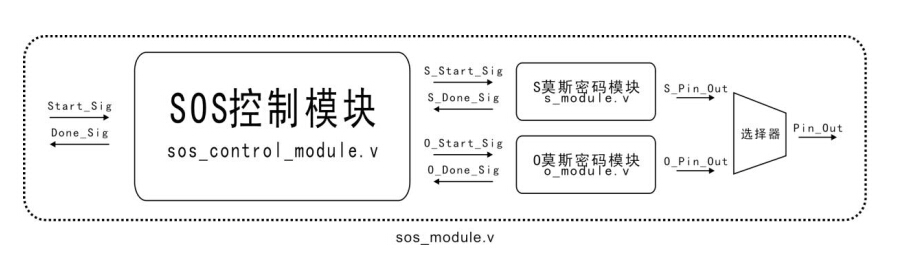

“Start_Sig”如同 C 语言中的调用指令,“Done_Sig”如同 C 语言的返回指令。这两个信号的存在就是为了控制模块的调用。

module sos_control_module

(

CLK, RSTn,

Start_Sig,

S_Done_Sig, O_Done_Sig,

S_Start_Sig, O_Start_Sig,

Done_Sig

); input CLK;

input RSTn;

input Start_Sig;

input S_Done_Sig, O_Done_Sig;

output S_Start_Sig, O_Start_Sig;

output Done_Sig; /*************************************/ reg [:]i;

reg isO;

reg isS;

reg isDone; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

begin

i <= 'd0;

isO <= 'b0;

isS <= 'b0;

isDone <= 'b0;

end

else if( Start_Sig )

case( i ) 'd0:

if( S_Done_Sig ) begin isS <= 'b0; i <= i + 1'b1; end

else isS <= 'b1; 'd1:

if( O_Done_Sig ) begin isO <= 'b0; i <= i + 1'b1; end

else isO <= 'b1; 'd2:

if( S_Done_Sig ) begin isS <= 'b0; i <= i + 1'b1; end

else isS <= 'b1; 'd3:

begin isDone <= 'b1; i <= 4'd4; end 'd4:

begin isDone <= 'b0; i <= 4'd0; end endcase /*****************************************/ assign S_Start_Sig = isS;

assign O_Start_Sig = isO;

assign Done_Sig = isDone; /*****************************************/ endmodule

module s_module

(

CLK, RSTn,

Start_Sig,

Done_Sig,

Pin_Out

); input CLK;

input RSTn;

input Start_Sig;

output Done_Sig;

output Pin_Out; /****************************************/ parameter T1MS = 'd49_999; /***************************************/ reg [:]Count1; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count1 <= 'd0;

else if( Count1 == T1MS )

Count1 <= 'd0;

else if( isCount )

Count1 <= Count1 + 'b1;

else if( !isCount )

Count1 <= 'd0; /****************************************/ reg [:]Count_MS; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count_MS <= 'd0;

else if( Count_MS == rTimes )

Count_MS <= 'd0;

else if( Count1 == T1MS )

Count_MS <= Count_MS + 'b1; /******************************************/ reg [:]i;

reg rPin_Out;

reg [:]rTimes;

reg isCount;

reg isDone; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

begin

i <= 'd0;

rPin_Out <= 'b0;

rTimes <= 'd1000;

isCount <= 'b0;

isDone <= 'b0;

end

else if( Start_Sig )

case( i ) 'd0, 4'd2, 'd4:

if( Count_MS == rTimes ) begin rPin_Out <= 'b0; isCount <= 1'b0; i <= i + 'b1; end

else begin isCount <= 'b1; rPin_Out <= 1'b1; rTimes <= 'd100; end 'd1, 4'd3, 'd5:

if( Count_MS == rTimes ) begin isCount <= 'b0; i <= i + 1'b1; end

else begin isCount <= 'b1; rTimes <= 10'd50; end 'd6:

begin isDone <= 'b1; i <= 4'd7; end 'd7:

begin isDone <= 'b0; i <= 4'd0; end endcase /******************************************/ assign Done_Sig = isDone;

assign Pin_Out = !rPin_Out; /******************************************/ endmodule

module o_module

(

CLK, RSTn,

Start_Sig,

Done_Sig,

Pin_Out

); input CLK;

input RSTn;

input Start_Sig;

output Done_Sig;

output Pin_Out; /****************************************/ parameter T1MS = 'd49_999; /***************************************/ reg [:]Count1; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count1 <= 'd0;

else if( Count1 == T1MS )

Count1 <= 'd0;

else if( isCount )

Count1 <= Count1 + 'b1;

else if( !isCount )

Count1 <= 'd0; /****************************************/ reg [:]Count_MS; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

Count_MS <= 'd0;

else if( Count_MS == rTimes )

Count_MS <= 'd0;

else if( Count1 == T1MS )

Count_MS <= Count_MS + 'b1; /******************************************/ reg [:]i;

reg rPin_Out;

reg [:]rTimes;

reg isCount;

reg isDone; always @ ( posedge CLK or negedge RSTn )

if( !RSTn )

begin

i <= 'd0;

rPin_Out <= 'b0;

rTimes <= 'd1000;

isCount <= 'b0;

isDone <= 'b0;

end

else if( Start_Sig )

case( i ) 'd0, 4'd2, 'd4:

if( Count_MS == rTimes ) begin rPin_Out <= 'b0; isCount <= 1'b0; i <= i + 'b1; end

else begin isCount <= 'b1; rPin_Out <= 1'b1; rTimes <= 'd400; end 'd1, 4'd3, 'd5:

if( Count_MS == rTimes ) begin isCount <= 'b0; i <= i + 1'b1; end

else begin isCount <= 'b1; rTimes <= 10'd50; end 'd6:

begin isDone <= 'b1; i <= 4'd7; end 'd7:

begin isDone <= 'b0; i <= 4'd0; end endcase /******************************************/ assign Done_Sig = isDone;

assign Pin_Out = !rPin_Out; /******************************************/ endmodule

module sos_module

(

CLK, RSTn,

Start_Sig,

Done_Sig,

Pin_Out

); input CLK;

input RSTn;

input Start_Sig;

output Done_Sig;

output Pin_Out; /*****************************/ wire S_Done_Sig;

wire S_Pin_Out; s_module U1

(

.CLK( CLK ),

.RSTn( RSTn ),

.Start_Sig( S_Start_Sig ), // input - from U3

.Done_Sig( S_Done_Sig ), // output - to U3

.Pin_Out( S_Pin_Out ) // output - to selector ) ; /*********************************/ wire O_Done_Sig;

wire O_Pin_Out; o_module U2

(

.CLK( CLK ),

.RSTn( RSTn ),

.Start_Sig( O_Start_Sig ), // input - from U3

.Done_Sig( O_Done_Sig ), // output - to U3

.Pin_Out( O_Pin_Out ) // output - to selector

); /*********************************/ wire S_Start_Sig;

wire O_Start_Sig; sos_control_module U3

(

.CLK( CLK ),

.RSTn( RSTn ),

.Start_Sig( Start_Sig ), // input - from top

.S_Done_Sig( S_Done_Sig ), // input - from U1

.O_Done_Sig( O_Done_Sig ), // input - from U2

.S_Start_Sig( S_Start_Sig ), // output - to U1

.O_Start_Sig( O_Start_Sig ), // output - to U2

.Done_Sig( Done_Sig ) // output - to top

); /*********************************/ //selector reg Pin_Out; always @ ( * )

if( S_Start_Sig ) Pin_Out = S_Pin_Out; // select from U1

else if( O_Start_Sig ) Pin_Out = O_Pin_Out; // select from U2

else Pin_Out = 'bx; /*********************************/ endmodule

Verilog之SOS信号-仿顺序操作的更多相关文章

- 【黑金教程笔记之006】【建模篇】【Lab 05 SOS信号之一】—笔记

sos_module.v是产生SOS信号的功能模块.即有次序的输出莫斯码:点.画.间隔.control_module.v是一个定时触发器,每一段时间使能sos_module.v. 模块: /***** ...

- 【黑金教程笔记之007】【建模篇】【Lab 06 SOS信号之二】—笔记

控制模块的协调角色. 实验六用到了实验四的按键消抖模块debounce_module.v和实验五的sos_module.v. 设计思路: debounce_module.v看成一个输入,sos_mod ...

- 【黑金教程笔记之001】veriloghdl 扫盲文—笔记&勘误

001_veriloghdl 扫盲文—笔记&勘误 2014/10/31 原文作者:akuei2 联系方式:blog.ednchina.con/akuei2 勘误001: Page 3 0.1 ...

- 【设计经验】1、Verilog中如何规范的处理inout信号

在FPGA的设计过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号).比如,IIC总线中的SDA信号就是一个双向信号,QSPI Flash的四线操作的时候四根信号线均为双向信号. ...

- verilog实现中值滤波

前言 项目需要,想要实现算法中的其中一步即中值滤波,同时,因为图像处理部分中值滤波相对来说还是比较简单的,将中值滤波的硬件实现作为进入FPGA领域的第一次尝试.虽然说网上有较多关于中值滤波的文档,可是 ...

- 基于Proteus仿真的Arduino学习(1)——Arduino Uno最小系统及LED的简单使用

一.前言: A.Arduino简介 Arduino是由一个欧洲开发团队于2005年冬季开发.其成员包括Massimo Banzi.David Cuartielles.Tom Igoe.Gianluc ...

- SPI通信实验---verilog(FPGA作为从机,使用可读可写)

本实验讲究实用性,故设计思想为:主机先向从机发送地址,若是向从机写入数据,则向从机发送数据,若是读取从机数据,则向从机发送时钟,然后在时钟下降沿读取数据即可.cs信号上升沿作为SPI通信的结束信号.r ...

- SPI的通信试验 --verilog (从机-全双工)

SPI的 有关知识参考FPGA作为主机的通信实验. 本实验中FPGA作为从机通过SPI与MCU等通信的试验,可以在时钟上升沿接收数据并且在时钟下降沿发送数据,模仿全双工模式.接收的 数据作为地址,通过 ...

- 【接口时序】2、Verilog实现流水灯及与C语言的对比

一. 软件平台与硬件平台 软件平台: 1.操作系统:Windows-8.1 2.开发套件:ISE14.7 3.仿真工具:ModelSim-10.4-SE 硬件平台: 1.FPGA型号:XC6SLX45 ...

随机推荐

- OneNote 2013 快捷键

越来越喜欢onenote这个笔记本软件,找了下提高效率的办法,收藏学习下: 转载自:http://onenoter.com/2013/04/5792 记录笔记和设置笔记格式 键入和编辑笔记 操作 按键 ...

- [系统开发] Django Admin上传图片简单校验

我的 models里有个ImageField字段,用来保存用户头像,希望通过Django Admin上传时校验头像大小,如果太大就报错,并且不保存. 网上有不少方法,有的通过第三方软件实现,有的通过自 ...

- 整理QQ数据库sql语句

设置数据库的时候 qq 号如果用整型,设置成UNSIGNED,不然超过一定数值就错误 UPDATE `sao_qq` SET qq_num = REPLACE ( qq_num, '@qq.com', ...

- X5 内核浏览器对json格式支持的一个小区别

var json1 = { "data": [{ "type": "pic", "filename": "P6 ...

- 在win下开发c++代码, 推荐一个工具dev c++

官方地址:http://bloodshed-dev-c.en.softonic.com/

- java变量的作用域

1.可分为成员变量和局部变量 两者的作用域不同:局部变量的作用域仅限于定义它的方法,方法外部无法访问,成员变量的作用域在整个类内部都可以访问如果访问权限允许的话,类外部也可以使用 初始值不同:对于成员 ...

- Entity Framwork(EF) 7——在现在数据库的甚而上开发MVC 新项目

一.开发背景: 由于老系统已经无法满足实际业务需求,需在现有数据库的甚而上开发新的项目. 二.困难点: 而EF默认情况下是要删除现有数据库表格后重新创建,这是不允许的.当你创建数据库对象时系统会提示“ ...

- java获取当前执行文件的路径

需要知道执行jar包时,jar包所在的路径. 开始使用了 p.getClass().getResource("/").getPath(); 结果在IDE里面使用是好的,但是在命令行 ...

- 调用百度地图API的应用混淆后出问题

1 混淆后出问题,程序异常退出 在proguard-project.txt中添加 -libraryjars libs/BaiduLBS_Android.jar -keep class com.baid ...

- 解决VMware“该虚拟机似乎正在使用中”问题

http://jingyan.baidu.com/article/4ae03de3fa2ae93eff9e6bb0.html