FPGA VGA时序的理解

最近在做FPGA毕业设计,毕业设计规划的是摄像头采集图像,经过均值滤波,中值滤波,高斯滤波,然后通过VGA接口控制显示器显示出来,所以最近学习了一下FPGA的VGA驱动的相关内容。

VGA接口

如上图所示,VGA接口一共15针,分为3*5。

主要使用的信号线是上面的5根线,行同步信号,场同步信号和R,G,B基色的模拟信号。

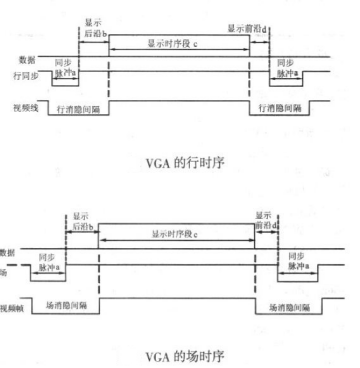

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

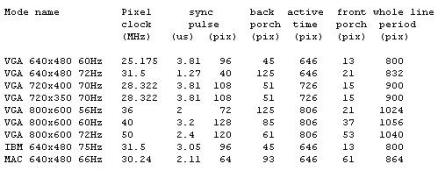

VGA水平扫描时序

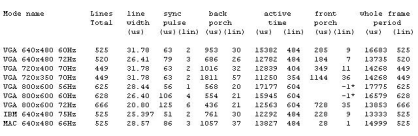

VGA垂直扫描时序

VGA时序图

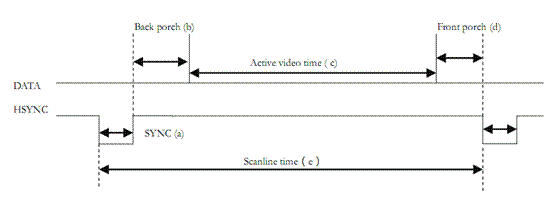

如上图VGA显示时序所示,VGA每次显示都需要同步信号,经过同步脉冲a,显示后沿b,显示时序段c,显示前沿d,然后是同步脉冲a,这样一个循环。

根据VGA协议标准,以640*480 60HZ为例,每秒钟要显示60次,一次显示800*525个点,其中640*480为显示时序段的有效点,其他的是为了同步时序的无效点。

如下图所示黄色区域为800个点的行周期,红色区域为525个点的场周期,只有行周期和场周期同时有效的橘色区域640*480才是有效显示区域。

VGA时序分析

一秒钟需要显示800*525*60个点,而时序的时钟频率是25MHZ,所以显示一个点的时间是25M/(800*525*60)=40ns.

行时序如上图所示:

a段的持续时间是96*40ns

b段的持续时间是45*40ns

c段的持续时间是646*40ns

d段的持续时间是13*40ns

e段的持续时间是800*40ns(e段是整个行周期)

场时序如上图所示:

o段的持续时间是2*e

p段的持续时间是30*e

q段的持续时间是484*e

r段的持续时间是9*e

S段的持续时间是528*e

只有行时序处于c段和场时序处于q段的时候发送的才是有效数据,一个行周期要显示640个点,一个场周期要显示480个行。

代码如下,代码只实现了VGA时序,时钟默认25MHZ。需要进一步修改。

- module vga_driver(

- clk ,

- rst_n ,

- din ,

- vga_hys ,

- vga_vys ,

- vga_rgb

- );

- parameter DATA_W = 16;

- input clk ;

- input rst_n ;

- input din ;

- output vga_hys ;

- output vga_vys ;

- output [DATA_W-1:0] vga_rgb ;

- reg vga_hys;

- reg vga_vys;

- reg [DATA_W-1:0] vga_rgb;

- reg [9:0] cnt_hys;

- reg [9:0] cnt_vys;

- wire add_cnt_hys;

- wire end_cnt_hys;

- wire add_cnt_vys;

- wire end_cnt_vys;

- reg display_area;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_hys <= 0;

- end

- else if(add_cnt_hys)begin

- if(end_cnt_hys)

- cnt_hys <= 0;

- else

- cnt_hys <= cnt_hys + 1;

- end

- end

- assign add_cnt_hys = 1;

- assign end_cnt_hys = add_cnt_hys && cnt_hys== 800-1;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_vys <= 0;

- end

- else if(add_cnt_vys)begin

- if(end_cnt_vys)

- cnt_vys <= 0;

- else

- cnt_vys <= cnt_vys + 1;

- end

- end

- assign add_cnt_vys = end_cnt_hys;

- assign end_cnt_vys = add_cnt_vys && cnt_vys==525-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_hys <= 0;

- end

- else if(add_cnt_hys && cnt_hys == 96-1)begin

- vga_hys <= 1;

- end

- else if(end_cnt_hys)begin

- vga_hys <= 0;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_vys <= 0;

- end

- else if(add_cnt_vys && cnt_vys == 2-1)begin

- vga_vys <= 1;

- end

- else if(end_cnt_vys)begin

- vga_vys <= 0;

- end

- end

- always @(*)begin

- display_area = cnt_hys >= 141 && cnt_hys <= (141+646) && cnt_vys >= 32 && cnt_vys < (32+484);

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_rgb <= 0;

- end

- else if(display_area)

- begin

- vga_rgb <= din;

- end

- else begin

- vga_rgb <= 0;

- end

- end

- endmodule

FPGA VGA时序的理解的更多相关文章

- 图像处理算法的仿真平台之VGA时序

一 概述 图像处理算法一般是用matla或OpenCV实现的,若是用FPGA实现,设计思路差别极大.matlab和opencv的优势:这些工具的优势在于可以方便地载入图像文件,或输出数据到图像文件, ...

- 【转载】VGA时序与原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- VGA 时序标准

VGA 显示器扫描方式从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行同步:当扫描完所有的行 ...

- VGA时序及其原理(转载)

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- FPGA时序约束理解记录

最近整理了一下时序约束的内容,顺便发出来分享记录一下. 任何硬件想要工作正常,均需满足建立和保持时间,至于这个概念不再陈述. 下面将重点介绍两个概念:建立余量和保持余量.FPGA内部进行时序分析无非就 ...

- fpga vga 显示

VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高.显示速率快.颜色丰富等优点,在彩色显示器领域得到了广泛的应用.不支持热插拔, ...

- 【转】 VGA时序及其原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- 每天进步一点点------FPGA 静态时序分析模型——reg2reg

2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满 ...

随机推荐

- 微信小程序添加底部导航栏

修改 app.json 文件即可 "tabBar": { "selectedColor": "#1296db", "list&qu ...

- Head First设计模式 1 设计模式入门 策略模式 观察者模式

关于基本的OOP特征: OOP的几大特征是抽象 继承 封装 多态. 我们把共同的部分抽象出来作为抽象类的存在,使用继承和接口来实现多态,然后私有的部分封装起来.一定程度上说,这些概念都是简单的设计模式 ...

- [LeetCode 92] Reverse Linked List II 翻转单链表II

对于链表的问题,根据以往的经验一般都是要建一个dummy node,连上原链表的头结点,这样的话就算头结点变动了,我们还可以通过dummy->next来获得新链表的头结点.这道题的要求是只通过一 ...

- Springboot项目全局异常统一处理

转自https://blog.csdn.net/hao_kkkkk/article/details/80538955 最近在做项目时需要对异常进行全局统一处理,主要是一些分类入库以及记录日志等,因为项 ...

- GitHub入门和项目托管

(博主原创文章,转载请注明出处: http://www.cnblogs.com/xianlei/git) 前言: 本文目标: Git入门,能够在Github托管项目,能够进行实际项目开发 本文主要内容 ...

- vue cli3 项目配置

[转]https://juejin.im/post/5c63afd56fb9a049b41cf5f4 基于vue-cli3.0快速构建vue项目 本章详细介绍使用vue-cli3.0来搭建项目. 本章 ...

- 【leetcode】815. Bus Routes

题目如下: We have a list of bus routes. Each routes[i] is a bus route that the i-th bus repeats forever. ...

- Java多线程和并发(一),进程与线程的区别

目录 1.进程和线程的由来 2.进程和线程的定义 3.进程和线程的区别 一.进程和线程的区别 1.进程和线程的由来 2.进程和线程的定义 进程是资源分配的最小单位,线程是CPU调度的最小单位 3.进程 ...

- max函数结合lambda使用

说明:d.keys() 以及列表可以看做lambda函数的实参,max的判断对象是key的值.最终返回的是使得key的值最大的那个实参.

- JavaScript实现页面滚动到div区域div以动画方式出现

用JavaScript实现页面滚动效果,以及用wow.js二种方式实现网页滚动效果 要实现效果是页面滚动到一块区域,该区域以动画方式出现. 这个效果需要二点: 一:我们要先写好一个css动画. 二:用 ...