FPGA VGA时序的理解

最近在做FPGA毕业设计,毕业设计规划的是摄像头采集图像,经过均值滤波,中值滤波,高斯滤波,然后通过VGA接口控制显示器显示出来,所以最近学习了一下FPGA的VGA驱动的相关内容。

VGA接口

如上图所示,VGA接口一共15针,分为3*5。

主要使用的信号线是上面的5根线,行同步信号,场同步信号和R,G,B基色的模拟信号。

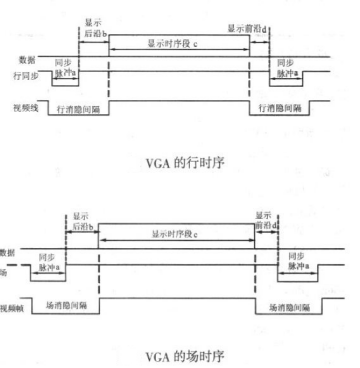

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号进行同步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行扫一线,完成一屏后在返回来扫描剩下的线,隔行扫描的显示器闪烁的厉害,会让使用者的眼睛疲劳。

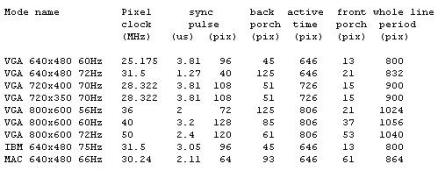

VGA水平扫描时序

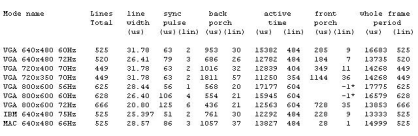

VGA垂直扫描时序

VGA时序图

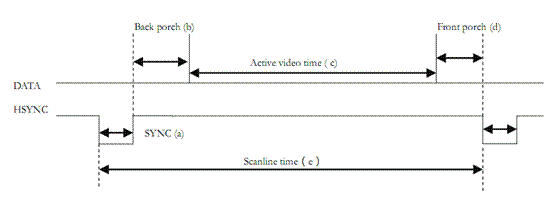

如上图VGA显示时序所示,VGA每次显示都需要同步信号,经过同步脉冲a,显示后沿b,显示时序段c,显示前沿d,然后是同步脉冲a,这样一个循环。

根据VGA协议标准,以640*480 60HZ为例,每秒钟要显示60次,一次显示800*525个点,其中640*480为显示时序段的有效点,其他的是为了同步时序的无效点。

如下图所示黄色区域为800个点的行周期,红色区域为525个点的场周期,只有行周期和场周期同时有效的橘色区域640*480才是有效显示区域。

VGA时序分析

一秒钟需要显示800*525*60个点,而时序的时钟频率是25MHZ,所以显示一个点的时间是25M/(800*525*60)=40ns.

行时序如上图所示:

a段的持续时间是96*40ns

b段的持续时间是45*40ns

c段的持续时间是646*40ns

d段的持续时间是13*40ns

e段的持续时间是800*40ns(e段是整个行周期)

场时序如上图所示:

o段的持续时间是2*e

p段的持续时间是30*e

q段的持续时间是484*e

r段的持续时间是9*e

S段的持续时间是528*e

只有行时序处于c段和场时序处于q段的时候发送的才是有效数据,一个行周期要显示640个点,一个场周期要显示480个行。

代码如下,代码只实现了VGA时序,时钟默认25MHZ。需要进一步修改。

- module vga_driver(

- clk ,

- rst_n ,

- din ,

- vga_hys ,

- vga_vys ,

- vga_rgb

- );

- parameter DATA_W = 16;

- input clk ;

- input rst_n ;

- input din ;

- output vga_hys ;

- output vga_vys ;

- output [DATA_W-1:0] vga_rgb ;

- reg vga_hys;

- reg vga_vys;

- reg [DATA_W-1:0] vga_rgb;

- reg [9:0] cnt_hys;

- reg [9:0] cnt_vys;

- wire add_cnt_hys;

- wire end_cnt_hys;

- wire add_cnt_vys;

- wire end_cnt_vys;

- reg display_area;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_hys <= 0;

- end

- else if(add_cnt_hys)begin

- if(end_cnt_hys)

- cnt_hys <= 0;

- else

- cnt_hys <= cnt_hys + 1;

- end

- end

- assign add_cnt_hys = 1;

- assign end_cnt_hys = add_cnt_hys && cnt_hys== 800-1;

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)begin

- cnt_vys <= 0;

- end

- else if(add_cnt_vys)begin

- if(end_cnt_vys)

- cnt_vys <= 0;

- else

- cnt_vys <= cnt_vys + 1;

- end

- end

- assign add_cnt_vys = end_cnt_hys;

- assign end_cnt_vys = add_cnt_vys && cnt_vys==525-1 ;

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_hys <= 0;

- end

- else if(add_cnt_hys && cnt_hys == 96-1)begin

- vga_hys <= 1;

- end

- else if(end_cnt_hys)begin

- vga_hys <= 0;

- end

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_vys <= 0;

- end

- else if(add_cnt_vys && cnt_vys == 2-1)begin

- vga_vys <= 1;

- end

- else if(end_cnt_vys)begin

- vga_vys <= 0;

- end

- end

- always @(*)begin

- display_area = cnt_hys >= 141 && cnt_hys <= (141+646) && cnt_vys >= 32 && cnt_vys < (32+484);

- end

- always @(posedge clk or negedge rst_n)begin

- if(rst_n==1'b0)begin

- vga_rgb <= 0;

- end

- else if(display_area)

- begin

- vga_rgb <= din;

- end

- else begin

- vga_rgb <= 0;

- end

- end

- endmodule

FPGA VGA时序的理解的更多相关文章

- 图像处理算法的仿真平台之VGA时序

一 概述 图像处理算法一般是用matla或OpenCV实现的,若是用FPGA实现,设计思路差别极大.matlab和opencv的优势:这些工具的优势在于可以方便地载入图像文件,或输出数据到图像文件, ...

- 【转载】VGA时序与原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- VGA 时序标准

VGA 显示器扫描方式从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行同步:当扫描完所有的行 ...

- VGA时序及其原理(转载)

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左像右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- FPGA时序约束理解记录

最近整理了一下时序约束的内容,顺便发出来分享记录一下. 任何硬件想要工作正常,均需满足建立和保持时间,至于这个概念不再陈述. 下面将重点介绍两个概念:建立余量和保持余量.FPGA内部进行时序分析无非就 ...

- fpga vga 显示

VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高.显示速率快.颜色丰富等优点,在彩色显示器领域得到了广泛的应用.不支持热插拔, ...

- 【转】 VGA时序及其原理

显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT对电子束进行消隐,每行结束时,用行同步信 ...

- FPGA VGA+PLL+IP核笔记

1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ.2.分辨率使用了800*600@72HZ.3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色.VGA图形基 ...

- 每天进步一点点------FPGA 静态时序分析模型——reg2reg

2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满 ...

随机推荐

- 程序包管理工具yum

yum 首先要有一个网络上或本地或远程的yum仓库.然后需要yum安装程序的机器去yum仓库下载yum元数据(包括包信息和依赖信息)到本地的cache里.当需要安装程序的时候,会查看yum源数据里是否 ...

- 【银川网络赛G】Factories

题目大意:给定一棵 N 个节点的树,边有边权,选定 M 个叶子节点,使得任意两个叶子节点的树上距离之和最小,求最小值是多少. 题解:任意两点的树上距离和问题应从边的贡献角度考虑. 设 \(f[u][i ...

- 【The 13th Chinese Northeast Collegiate Programming Contest E题】

题目大意:给定一棵 N 个点的树,边有边权,定义"线树"为一个图,其中图的顶点是原树中的边,原树中两条有公共端点的边对应在线图中存在一条边,边权为树中两条边的边权和,求线图的最小生 ...

- qt5--定时器

定时器方式一:----定时器事件 需要 #include <QTimerEvent> #include "win.h" #include <QDebug& ...

- Java三大体系JavaEE、JavaSE、JavaME的区别

Java由四方面组成: ●Java编程语言,即语法. ●Java文件格式,即各种文件夹.文件的后缀. ●Java虚拟机(JVM),即处理*.class文件的解释器. ●Java应用程序接口(Java ...

- JDK 7升8 maven 编译报错

在JDK由版本7升级到8时,使用maven编译会报doc错误,原因是JAVA8不支持JAVA7编写的doc,报错信息如下: @param name 未找到 @return 的用法无效 可以使添加配置- ...

- List集合遍历的三种方法

测试数据: List<String> list = new ArrayList<String>(); list.add("java"); list.add( ...

- JS大文件上传断点续传解决方案

1 背景 用户本地有一份txt或者csv文件,无论是从业务数据库导出.还是其他途径获取,当需要使用蚂蚁的大数据分析工具进行数据加工.挖掘和共创应用的时候,首先要将本地文件上传至ODPS,普通的小文件通 ...

- ueditor+实现word图片自动上传

最近公司做项目需要实现一个功能,在网页富文本编辑器中实现粘贴Word图文的功能. 我们在网站中使用的Web编辑器比较多,都是根据用户需求来选择的.目前还没有固定哪一个编辑器 有时候用的是UEditor ...

- C语言博客作业04数组

0.展示PTA总分 1.本章学习总结 1.1 学习内容总结 1.int a[10];为定义数组,表示数组有10个数 2.数组的下标都是从0开始,到n-1结束 3.数组里元素的个数不能大于数组的长度 4 ...