PCB 布线,直角线,差分线,蛇形线

1、直角线

直角走线的一般标准是PCB布线中要尽量避免的情况,也几乎成为衡量布线好坏的标准之一。

直角走线对信号的影响主要体系那在下面三个方面

1、保教可以等效为传输线是哪个的容性负载,减缓上升时间。

2、阻抗不连续会造成信号的反射。

3、直角尖端会产生EMI

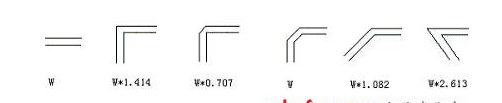

如图不同角度的走线拐角线宽变化。

传输线的直角带来的寄生电容可以有下面这个经验公式来计算。

C = 61w(Er)[size = 1]1/2[/size]/Z0

C:拐角的等效电容pF,w:走线宽度inch,Er:介质的介电常数,Z0:传输线的特征阻抗

在很多实际测试的结果中显示,直角走线并不会比直线产生明显的EMI。

总的来说直角走线并不是想象中的那么可怕,至少在GHz一下的应用中,但是随着PCB处理的信号频率不断提高,到了10GHz以上的RF领域,这些直角就会成为重点对象(总之不推荐)

2、差分走线

什么是差分走线,通俗的来说就是驱动端发送两个等值,相反的信号,接收端通过比较这两个电压的差值来判断逻辑状态,而承载差分信号的那一对走线就称为差分走线。(就会增加接口口的使用数量)

差分走线的优势

1、抗信号干扰能力强,因为差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两根信号的差值,所以外界的工模噪声可以被完全抵消掉。

2、能够有效的抑制EMI,由于两根信号线的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,外界的电磁能量就越少。

3、时序定位精确。

差分走线的基本要求:等长、等距。等长是为了保证两个差分信号时刻保持极性相反,减少共模分量,等距主要是为了保证两者差分阻抗一致,减少反射。

3、蛇形走线

主要目的是为了调节延时,满足系统设计要求,但是蛇形走线会破坏信号质量,改变传输延时,布线是要尽量避免使用。但在实际设计中,为了保证有足够的保持时间,或者减小同组信号之间的时间偏移。信号在蛇形走线上传输是,相互平行的线段之间会产生耦合,呈差摸形式,s越小,LP越大,则耦合程度也会越大,可能会导致传输延时减小,以及由于串扰大大的降低信号的质量。 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

PCB分层策略

1、布线层的投影平面应该在其回流平面区域内,布线层如果不在其回流平面层投影区内,在布线时将会有信号线在投影区域外,导致“边缘辐射”问题,并且还会导致信号回路面积增大,导致差摸辐射增大。

2、尽量避免布线层相邻的设置,因为相邻布线层上的平行信号走线会导致信号串扰,所以如果无法避免布线层相邻,应该适当拉大两布线层间距,缩小布线层与其信号回路之间的层间距。

3、相邻平面层应该避免其投影平面重叠,因为投影重叠时,层与层之间的耦合电容会导致各层之间的噪声互相耦合。

多层板设计:

1、关键布线层(时钟线、总线、接口信号线、射频线、复位信号线、片选信号线以及各种控制信号线等所在层)应该与完整地平面相邻,优选两地平面之间,关键信号线一般都是强辐射或者敏感的信号线,靠近地平面布线能够使信号回路面积减小,减小其辐射强度或者提高干扰能力。

2、电源平面应该相对于相邻平面内缩,电源平面响度与其回流地平面雷所可以有效的抑制 边缘辐射问题。

3、单板TOP、Bottom层是否无大于50MHz信号线,如果有,最好将高频信号在两个平面层之间,以抑制对空间辐射。

PCB 布线,直角线,差分线,蛇形线的更多相关文章

- PCB走线分析——直角、差分、蛇形线

PCB直角走线的影响 布线(Layout)是PCB设计工程师最基本的工作技能之一.走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过 Layout 得以实现并验证,由此可见,布 ...

- [置顶]PADS PCB功能使用技巧系列之NO.002- 如何走差分线?

差分信号在高速电路设计中应用越来越广泛,如USB.HDMI.PCI.DDR*等,承载差分信号的差分线主要优势有:抗干扰能力强,能有效抑制EMI.时序定位精确等,对于PCB工程师来说,最关注的是如何确保 ...

- PCB差分线学习

问:何为差分信号? 答:通俗地说,就是驱动端发送两个等值.反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”. 问:差分线的优势在哪? 答:差分信号和普通的单端信号走线相比,最明 ...

- Altium Designer 画"差分线"

Altium Designer 画"差分线" 如何在 Altium Designer 中快速进行差分对走线1:在原理图中让一对网络前缀相同,后缀分别为_N 和_P,并且加上差分队对 ...

- 差分线Layout的两个误区

误区一:认为差分线可以相互之间耦合,所以可以相互之间提供回流路径,不需要地作为回流路径: 其实在信号回流分析上,差分走线和普通的单端走线的机理是一致的,即高频信号总是沿着电感最小的回路进行回流.最大的 ...

- PCB Genesis加邮票孔(线与线)实现算法

一.Genesis加邮票孔(线与线)实现算法 1.鼠标点击位置P点, 2.通过P点求出,垂足2个点:P1C与P2C (两个点即距离2条线段垂直的垂足点) 3.计算P1C到P2C方位角(假设置为变量PA ...

- PCB布线经验

查看: 3645|回复: 11 [经验] PCB设计经验(1)——布局基本要领 [复制链接] ohahaha 927 TA的帖子 0 TA的资源 纯净的硅(中级) 发消息 加好友 电 ...

- PCB Layout设计规范——PCB布线与布局

1.PCB布线与布局隔离准则:强弱电流隔离.大小电压隔离,高低频率隔离.输入输出隔离,分界标准为相差一个数量级.隔离方法包括:空间远离.地线隔开. 2. 晶振要尽量靠近IC,且布线要较粗 ...

- PCB布线总的原则

转自张飞实战电子公众号 PCB布线总的原则 最短路径和减少干扰 PCB布线的总的流程大致如下: 1了解制造厂商的制造规范-线宽,线间距,过孔要求及层数要求: 2确定层数并定义各层的功能: 3设计布线规 ...

随机推荐

- 八、自定义starter

starter: 1.这个场景需要使用到的依赖是什么? 2.如何编写自动配置 @Configuration //指定这个类是一个配置类 @ConditionalOnXXX //在指定条件成立的情况下自 ...

- iis子站点

在iis已有的站点下可以继续添加”应用程序”,就构成子站点:需要访问子站点app下的程序,只想在controller/action前,加个app就行,即app/controller/action 这样 ...

- 【叶问】 MySQL常用的sql调优手段或工具有哪些

MySQL常用的sql调优手段或工具有哪些1.根据执行计划优化 通常使用desc或explain,另外可以添加format=json来输出更详细的json格式的执行计划,主要注意点如下: ...

- 前端 HTML body标签相关内容

想要在网页上展示出来的内容一定要放在body标签中. 常用标签: 标题标签 h1-h6 段落标签 p标签 超链接标签 a标签 列表标签 ul,ol,li 定义列表<dl> 子标签 div ...

- navicat如何导出mysql数据表结构

我们在创建数据库时会对字段进行设置,比如类型.长度等,如果字段多的话一个个设置非常麻烦,可以从其他地方已有的表导入数据表结构,怎么操作呢?我们拿navicat导出mysql数据表结构为例: 1.点击“ ...

- 升级my.cnf注意

升级my.cnf注意 mkdir -p /ngbs/data/{logs,tmp} vi /etc/init.d/mysqlbasedir=/usr/local/mysql datadir=/ngb ...

- 20170712 SQL Server 日志文件收索

-- 1 日志文件增长过快,未进行任务计划截断备份 造成文件过大199G 左右,而可用空间不足8% -- 2 日志备份之前,需要一次完整备份 再进行截断备份 出现可用空间99% 此时可以选择收索数据库 ...

- TlistView基本使用

//增加 procedure TForm1.Button1Click(Sender: TObject); var lsItem: TListItem; begin lsItem := ListView ...

- dxCalloutPopup 简单使用教程

Panel1.Visible := False; // 设置panel初始不显示 dxCalloutPopup1.PopupControl := Panel1; // 设置弹出窗口内容为哪个控件 dx ...

- Mysql事务原理介绍

事务 一个事务会涉及到大量的cpu计算和IO操作,这些操作被打包成一个执行单元,要么同时都完成,要么同时都不完成. 事务是一组原子性的sql命令或者说是一个独立的工作单元,如果数据库引擎能够成功的对数 ...