04-时序逻辑电路设计之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献

实验目的:以计数器为例学会简单的时序逻辑电路设计

实验平台:芯航线FPGA核心板

实验原理:

时序逻辑电路是指电路任何时刻的稳态输出不仅取决于当前的输入,还与前一时刻输入形成的状态有关。这跟组合逻辑电路相反,组合逻辑的输出只会跟目前的输入成一种函数关系。换句话说,时序逻辑拥有储存元件(内存)来存储信息,而组合逻辑则没有。

计数器的核心元件是触发器,基本功能是对脉冲进行计数,其所能记忆脉冲最大的数目称为该计数器的模/值,常用在分频、定时等处。计数器的种类很多,按照计数方式的不同可以分为二进制计数器、十进制计数器以及任意进制计数器,按照触发器的时钟脉冲信号来源可分为同步计数器与异步计数器。按照计数增减可分为加法计数器、减法计数器以及可逆计数器。

此处设计一个计数器,使其使能板载LED每500ms,状态翻转一次。核心板晶振为50MHz,也就是说时钟周期为20ns,这样可以计算得出500ms = 500_000_000ns/20 = 25_000_000;即需要计数器计数25_000_000次,也就是需要一个至少25位的计数器。且每当计数次数达到需要清零并重新计数。

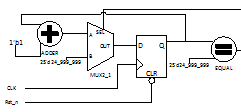

VerilogHDL之所以被称为硬件电路描述语言,就是因为我们不是在类似C一样进行普通的编程,我们是在编写一个实际的硬件电路,例如02中设计的一个二选一选择器最后就是被综合称为一个真正的选择器。上面提到计数器即为加法器、比较器、寄存器以及选择器构成,如图4-1所示。

图4-1 计数器逻辑电路图

实验内容:

按照02章所讲,建立工程子文件夹后,新建一个以名为counter的工程保存在prj下,并在本工程目录的rtl文件夹下新建verilog file文件在此文件下输入以下内容并以counter.v保存。这里之所以在计数值计数到25'd24_999_999而不是25'd25_000_000是因为计数器是从0开始计数而不是1。这里每当计数器计数到预设的值后就让led取反一次。

|

module counter(Clk50M,Rst_n,led);

input Clk50M; input Rst_n;

output

reg

//计数器计数进程 always@(posedge Clk50M or if(Rst_n == cnt <= else cnt <= else cnt <= cnt +

//led输出控制进程 always@(posedge Clk50M or if(Rst_n == led <= else led <= else led <= led;

endmodule |

进行分析和综合直至没有错误以及警告。

为了测试仿真编写测试激励文件,新建counter_tb.v文件并输入以下内容再次进行分析和综合直至没有错误以及警告,保存到testbench文件夹下。这里生成了一个周期为20ns的时钟clk,并且例化了需要测试的counter.v。

|

`timescale `define clock_period 20 module counter_tb; reg clk; reg rst_n;

wire led;

counter counter0( .Clk50M(clk), .Rst_n(rst_n), .led(led) );

initial clk = always

initial rst_n = #(`clock_period rst_n = #2000000000; $stop; end

endmodule |

设置好仿真脚本后进行功能仿真,可以看到如图3-2所示的波形文件,可以看出高低电平变化的时间均是0.5s也就是500ms,得出符合既定的设计要求,至此功能仿真结束。

图3-2 功能仿真波形文件

在进行上述的功能仿真时可以发现需要仿真时间较长,这是由于将计数器的计数值太大,因此可以将counter.v的cnt计数值修改为24_999来减少仿真时间,这时会发现仿真时间大幅度缩短,且图3-3中高低电平变化时间变为500_000ns,相比500ms缩短了1000倍,也可以说明功能仿真正确。

图3-3 缩小计数值后的功能仿真波形

进行全编译后进行门级仿真,可以看到如图3-4所示波形图,在这可以看出由于门电路的延迟高低电平变化时间并不严格等于0.5s。

图3-4 时序仿真波形

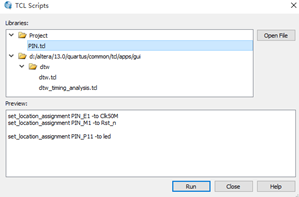

现进行分配引脚,此处介绍另一种分配引脚的方式,采用tcl文件。首先在File—New中选中Tcl Script File,新建一个tcl文件。并输入以下内容后以PIN.tcl名称保存到prj文件夹下。此处由于不同批次可能会引脚分配略有不同,请根据对应的引脚表来编写。

图3-5 新建tcl文件

|

set_location_assignment PIN_E1 -to Clk50M set_location_assignment PIN_M1 -to Rst_n

set_location_assignment PIN_P11 -to led |

然后单击Tools--Tcl Script,弹出图3-7对话框后选中编写好的PIN.tcl文件,点击Open Files编写的内容就会出现在下面的框图中,此时再点击Run会弹出图3-8对话框,提示已经运行完毕。我们这时可以打开Pin planer查看分配好的引脚。

图3-7 设置Tcl脚本

图3-8运行Tcl脚本

图3-9 脚本运行成功

全编译后可以在RTL viewer中可以看到图3-10所示的硬件逻辑电路,也存在前面讲到的加法器、比较器、寄存器以及选择器构成的计数器。下载到开发板中可以看到图3-11现象,LED0以500ms的时间进行闪烁,如果有示波器也可以测量这时候的引脚波形进行观察。

图3-10 RTL viewer

图3-11 实验现象

至此,就完成了一个基本的时序逻辑,计数器的设计。请以此为基础自行设计使得每个灯以不同的频率闪烁,并进行仿真以及板级验证。

04-时序逻辑电路设计之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档的更多相关文章

- 03-组合逻辑电路设计之译码器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1. 再次熟悉Quartus II工程的建立以及完整的FPGA开发流程 2. 以译码器为例学会简单组合逻辑电路设计 实验平台:无 实验原理: 组合逻辑, ...

- 05-IP核应用之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯顿队长精心奉献 实验目的:了解FPGA的IP核相关知识并以计数器IP核为例学会基本IP使用的流程 实验平台:无 实验原理: IP核(Intellectual Propert ...

- 06-BCD计数器设计与应用——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.掌握BCD码的原理.分类以及优缺点 2.设计一个多位的8421码计数器并进行验证 3.学会基本的错误定位以及修改能力 ...

- 09A-独立按键消抖实验01——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习状态机的设计思想并以此为基础实现按键消抖 2.单bit异步信号同步化以及边沿检测 3.在激励文件中学会使用随机数发生函数$random 4.仿真模 ...

- 08-FPGA状态机设计实例——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:1.学习状态机的相关概念 2.理解一段式.两段式以及三段式状态机的区别以及优缺点 实验平台:芯航线FPGA核心板 实验原理: 状态机全称是有限状态机(fin ...

- 02-FPGA设计流程介绍——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线——普利斯队长精心奉献 课程目标: 1.了解并学会FPGA开发设计的整体流程 2.设计一个二选一选择器并进行功能仿真.时序仿真以及板级验证 实验平台:芯航线FPGA开发板.杜邦线 实验内容: 良 ...

- 10-8位7段数码管驱动实验——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.实现FPGA驱动数码管动态显示: 2.使用In system sources and probes editor工具,输入需要显示在数码管上的的数据, ...

- 09B-独立按键消抖实验02——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的: 1.复习按键的设计 2.用模块化设计的方式实现每次按下按键0,4个LED显示状态以二进制加法格式加1,每次按下按键1,4个LED显示状态以二进制加法格式减 ...

- 07-阻塞赋值与非阻塞赋值原理分析——小梅哥FPGA设计思想与验证方法视频教程配套文档

芯航线--普利斯队长精心奉献 实验目的:掌握阻塞赋值与非阻塞赋值的区别 实验平台:无 实验原理: 阻塞赋值,操作符为"=","阻塞"是指在进程语句( ...

随机推荐

- php中提示Undefined index的解决方法

我们经常接收表单POST过来的数据时报Undefined index错误,如下: $act=$_POST['action']; 用以上代码总是提示 Notice: Undefined index: a ...

- POJ3468 线段树(区间更新,区间求和,延迟标记)

A Simple Problem with Integers Time Limit: 5000MS Memory Limit: 131072K Total Submissions: 97196 ...

- css3效果

1. 放大图片: /*galleryImage css*/ a.galleryImage{ display:block;} .galleryImage img{ transition:all .4s ...

- JS简单的图片左右滚动

<div id="scroll" style="overflow:hidden;width:757px;"> <table cellpaddi ...

- c#中文转全拼或首拼

参考:http://www.jb51.net/article/42217.htmhttp://blog.csdn.net/cstester/article/details/4758172 Chines ...

- html - 自动播放音乐

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <title> ...

- 安卓模拟器研究-root

http://www.bluestacks.cn/index.asp 下载最新的 BlueStacks 尝试了很久都没有root成功. 百度搜索 找到经验文档 http://jingyan.baid ...

- Harris角点检测算法优化

Harris角点检测算法优化 一.综述 用 Harris 算法进行检测,有三点不足:(1 )该算法不具有尺度不变性:(2 )该算法提取的角点是像素级的:(3 )该算法检测时间不是很令人满意. 基于以上 ...

- IOS第七天(3:UiTableView 模型和数据的分组的显示)

*************UiTableView模型和数据的分组的显示 #import "HMViewController.h" #import "HMHero.h&qu ...

- 安卓中級教程(2):@InjectView中的對象inject

package com.example.ele_me.util; import java.lang.annotation.Annotation; import java.lang.reflect.Fi ...