SPI总线协议及SPI时序图详解

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

---------------------------------------------------

1 0--1 101010x 1010101

1 1--0 01010100101011 1

---------------------------------------------------

2 0--1 010100x 0101011

2 1--0 10101001010110 101001x 1010110

0101101 010010x 0101101

1011010 100101x 1011010

5 1--0 01001010110101 001010x 0110101

1101010 010101x 1101010

1010101

0

---------------------------------------------------

这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、 sdo相对于主机而言的。根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU与各种外围器件进行全双工、同步串行通讯。

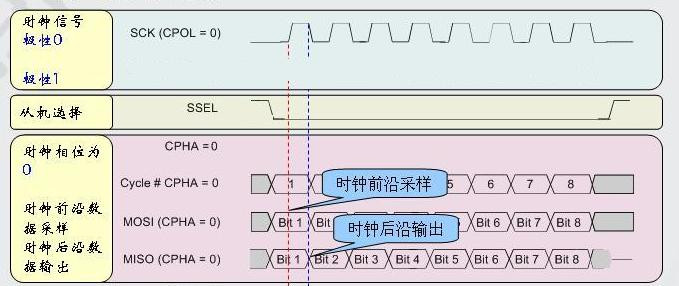

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。 SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI时序图详解-SPI接口在模式0下输出第一位数据的时刻

SPI接口在模式0下输出第一位数据的时刻

SPI接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。图1中表现了这四种时序,

时序与CPOL、CPHL的关系也可以从图中看出。

CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,

空闲电平为高电平。CPHA是用来决定采样时刻的,CPHA=0,在每个周期的第一个时钟沿采样,

CPHA=1,在每个周期的第二个时钟沿采样。

只关注模式0的时序。

在时钟的后沿输出数据(下降沿,第二个时钟沿)。首先来看主器件,主器件的输出口(MOSI)输出的数据bit1,

在时钟的前沿被从器件采样,那主器件是在何时刻输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,

比 SCK的上升沿还要早半个时钟周期。bit1的输出时刻与SSEL信号没有关系。再来看从器件,

主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时刻输出bit1的呢。

从器件是在SSEL信号有效后,立即输出bit1,尽管此时SCK信号还没有起效。关于上面的主器件

和从器件输出bit1位的时刻,可以从图3、4中得到验证。

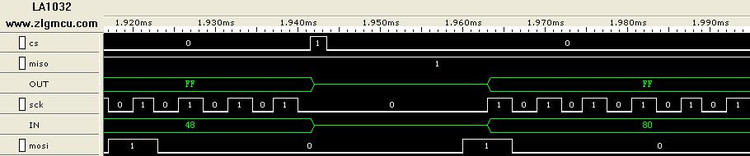

延时了一段时间,之后再向数据寄存器写入了要发送的数据,来观察主器件输出bit1的情况(MOSI)。

可以看出,bit1(值为1)是在SCK信号有效之前的半个时钟周期的时刻开始输出的(与CS信号无关),

到了SCK的第一个时钟周期的上升沿正好被从器件采样。

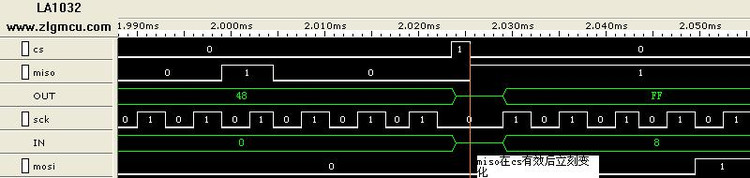

图4中,注意看CS和MISO信号。我们可以看出,CS信号有效后,从器件立刻输出了bit1(值为1)。

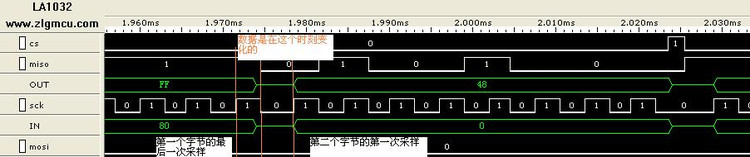

通常我们进行的spi操作都是16位的。图5记录了第一个字节和第二个字节间的相互衔接的过程。

第一个字节的最后一位在SCK的上升沿被采样,随后的SCK下降沿,从器件就输出了第二个字节的第一位。

SPI总线协议介绍(接口定义,传输时序)

一、技术性能

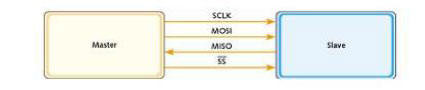

SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

-------------------------------------------------------

二、接口定义

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

(2)MISO:主器件数据输入,从器件数据输出

(3)SCLK :时钟信号,由主器件产生

(4)/SS:从器件使能信号,由主器件控制

-------------------------------------------------------

三、内部结构

四、传输时序

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如下图所示,在SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

SPI总线协议及SPI时序图详解的更多相关文章

- SPI总线协议及SPI时序图详解【转】

转自:https://www.cnblogs.com/adylee/p/5399742.html SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接 ...

- UML之时序图详解

原文链接:https://blog.csdn.net/fly_zxy/article/details/80911942 什么是时序图 时序图(Sequence Diagram),又名序列图.循序图,是 ...

- 关于I2C和SPI总线协议【转】

关于I2C和SPI总线协议 IICvs SPI 现今,在低端数字通信应用领域,我们随处可见IIC (Inter-Integrated Circuit) 和 SPI (Serial Peripheral ...

- 【转】SPI总线协议

SPI总线协议 By Xiaomin | April 17, 2016| 技术 概述 SPI(Serial Peripheral Interface)总线是主要应用于嵌入式系统内部通信的串行同步传输总 ...

- 搞懂分布式技术4:ZAB协议概述与选主流程详解

搞懂分布式技术4:ZAB协议概述与选主流程详解 ZAB协议 ZAB(Zookeeper Atomic Broadcast)协议是专门为zookeeper实现分布式协调功能而设计.zookeeper主要 ...

- (转)CAS (4) —— CAS浏览器SSO访问顺序图详解(CAS Web Flow Diagram by Example)

CAS (4) —— CAS浏览器SSO访问顺序图详解(CAS Web Flow Diagram by Example) tomcat版本: tomcat-8.0.29 jdk版本: jdk1.8.0 ...

- HTTP协议头部与Keep-Alive模式详解

HTTP协议头部与Keep-Alive模式详解 .什么是Keep-Alive模式? 我们知道HTTP协议采用“请求-应答”模式,当使用普通模式,即非KeepAlive模式时,每个请求/应答客户和服务器 ...

- 十图详解tensorflow数据读取机制(附代码)转知乎

十图详解tensorflow数据读取机制(附代码) - 何之源的文章 - 知乎 https://zhuanlan.zhihu.com/p/27238630

- CAS (6) —— Nginx代理模式下浏览器访问CAS服务器网络顺序图详解

CAS (6) -- Nginx代理模式下浏览器访问CAS服务器网络顺序图详解 tomcat版本: tomcat-8.0.29 jdk版本: jdk1.8.0_65 nginx版本: nginx-1. ...

随机推荐

- Linux内核分析——进程描述与创建

20135125陈智威 原创作品转载请注明出处 <Linux内核分析>MOOC课程http://mooc.study.163.com/course/USTC-1000029000 实验内容 ...

- android 内存查看的不同数据指标

内存耗用:VSS/RSS/PSS/USS 的介绍 VSS - Virtual Set Size 虚拟耗用内存(包含共享库占用的内存) RSS - Resident Set Size 实际使用物理内存( ...

- 如何启动app时全屏显示Default.png(图片)?

- java并发编程学习笔记(一)初识并发原子性

1.并发的意义 现在是一个多核的时代,并发的存在意义就是为了能够充分利用多核计算机的优势,提高程序的运行效率: 2.并发的风险 竞争-----多个线程对内存数据数据进行读写操作时,对数据处理结果的一个 ...

- Huffman编码(测试源代码)

1.此程序为c++程序 2.以下代码可实现手动输入,即去掉代码中的/*...*/注释符,并同时去掉赋值代码段 3.源代码 #include<iostream> using namespac ...

- 2016-12-19 php修改数据库数据

让info表在网页中显示 <h1>人员表</h1><table width="100%" cellpadding="opx" ce ...

- Linux的课程总结

Linux的课程总结 20125133 马国祥 通过16周的学习明白学好linux不是一件一蹴而就的事,一定要能坚持使用它,特别是在使用初期,由于在linux中,用户权限很大,做任何事情都很自由,所以 ...

- PAT (Advanced Level) Practise:1001. A+B Format

[题目链接] Calculate a + b and output the sum in standard format -- that is, the digits must be separate ...

- 修改VS 所有项目的Include目录和Lib目录

像以前的方法 在 工具--选项--项目和解决方案里的修改已经被弃用.

- debain 8安装为知笔记(how to install wiznote in debain 8)

刚装了debain8后想安装为知笔记,百度之后发现为知笔记原来是开源软件.代码托管在github上:https://github.com/WizTeam/WizQTClient 但是上面只有Ubunt ...