FPGA数字鉴相鉴频器的开发记录

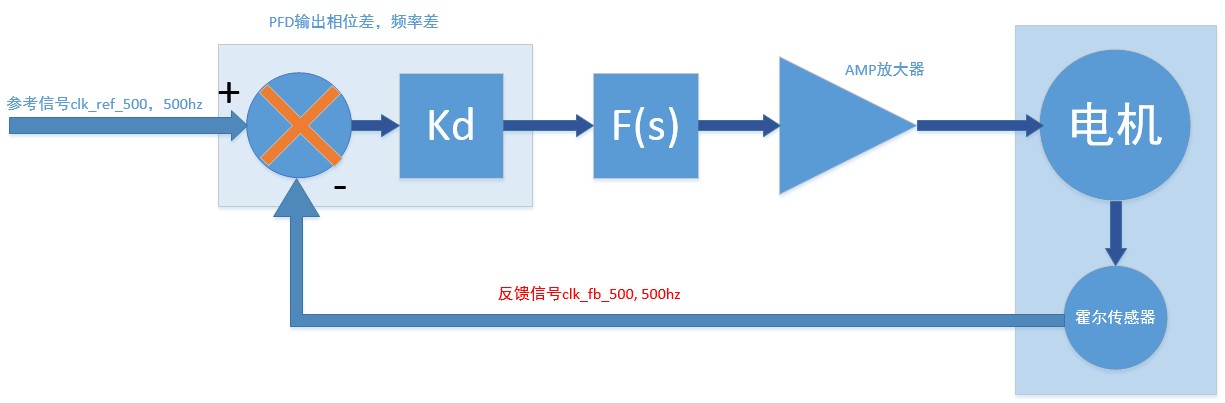

1. 对于电机的锁相控制,需要对相差进行PI性质的环路滤波,但现有的锁相环中鉴频鉴相器输出为相差脉冲而非数字量,难以直接进行PI特性的环路滤波。

通过对晶振的非整数分频获取准确的参考时钟,基于触发器机制实现了PFD相差脉冲的数字量化,且可以输出频差数字量。锁相环是频率和相位的同步控制系统,实现输入参考信号和反馈信号的频率相等,相位差恒定。利用锁相环技术可实现数字信号的同步,将这个思想引入电机的速度控制系统中,则能够实现稳态精度很高的转速控制。综合起来就是电机转速的控制反馈系统,因为要求相位差恒定,所以需要准确的检测相位差,而本次的设计就是检测相位差。锁相环和数字鉴相鉴频器是两个东西,前者是控制,后者是检测。

2. Pi性质的环路滤波?难道是PID控制,在反馈系统中,用输出的实际值和理论值的差值去反馈进系统的输入。PID就是反馈的比例,积分和微分。不过这里的滤波是什么?电机的锁相环控制中,电机加霍尔传感器是二阶系统。什么是二阶系统? y=ax^2+bx+c?

3. 做鉴相鉴频器的目的是为了稳速,不过现在还没明白,如何提高速度。这并不是我们关心的,假设电机转速500转每秒(霍尔传感器采样得到500MHz),晶振时钟是40MHz。

4.为了得到500 Hz的参考时钟,需要对40 MHz的晶振时钟进行两次分频操作。分频系数为N-0.5(N为整数)时,就是半整数分频。本次需要实现奇数分频,还有半整数分频。对40 MHz的晶振时钟先后进行等占空比125分频和2. 5半整数分频,得到320 kHz和128 kHz的时钟,经过时钟预分频器分频后的固定占空比128 kHz的时钟信号经过8位计数器,得到500 Hz的参考输入信号,反馈时钟输入并检测到其上升沿。

5. 在每个反馈信号的上升沿保存8位寄存器的值,这个值就是频率差(非线性)和相位差(线性)。同时用一个标志位,为1说明有上升沿,为0说明无上升沿,代码如下

module pfd(reset, clk_40mhz, clk_128k, clk_fb_500, phase_value, clk_ref_out); input reset;

input clk_128k; //两次分频得到的128Khz的时钟

input clk_fb_500; //电机的反馈时钟500hz

input clk_40mhz; reg clk_ref_500;

output [:] phase_value;

reg [:] phase_reg;

output clk_ref_out; reg [:] cout_8bit; //8位计数器

reg [:] ph_reg; //8位寄存器

reg have_flag;

reg clk_fb_prv;

reg clk_ref_prv;

reg [:] phase_value_1;

reg [:] phase_value_tmp;

parameter PHASE_MAX_VALUE = 'h7F; wire cout_en; //8位计数器,一个always里面可以写2个if语句吗?

always @(posedge clk_128k or negedge reset) begin

if(!reset)

cout_8bit <= 'b0;

else

cout_8bit <= cout_8bit + 'b1;

end //产生参考时钟500HZ

always @(posedge clk_40mhz) begin if(cout_8bit == 'h0)

clk_ref_500 <= ;

else if(cout_8bit == 'h7f)

clk_ref_500 <= ;

else

clk_ref_500 <= clk_ref_500;

end //D触发器,边沿检测反馈信号上升沿和参考信号下降沿

/*

always @(posedge clk_fb_500 or negedge clk_ref_500) begin

if(clk_fb_500 == 1) begin

have_flag = 1;

clk_fb_prv = clk_fb_500;

phase_value_1 = cout_8bit; end

else if(clk_ref_500 == 0) begin

have_flag = 0;

phase_value = phase_value_tmp; end

else

have_flag = 0; end

*/ always @(posedge clk_40mhz) begin

clk_fb_prv <= clk_fb_500;

clk_ref_prv <= clk_ref_500;

if({clk_fb_prv,clk_fb_500} == 'b01) begin //判断反馈信号的上升沿

have_flag <= ;

phase_value_1 <= cout_8bit; end

else if({clk_ref_prv,clk_ref_500} == 'b01) begin //判断参考信号的上升沿

have_flag <= ;

phase_reg <= phase_value_tmp; end

else

have_flag <= have_flag; end //怎么去解决一个周期内有2个反馈信号的上升沿的问题?

//总线选通开关

always @(posedge clk_40mhz)begin

if(have_flag == )

phase_value_tmp <= phase_value_1;

else

phase_value_tmp <= PHASE_MAX_VALUE; end

//PFD输出

//always @(posedge clk_128k) assign clk_ref_out = clk_ref_500;

assign phase_value = phase_reg;

endmodule

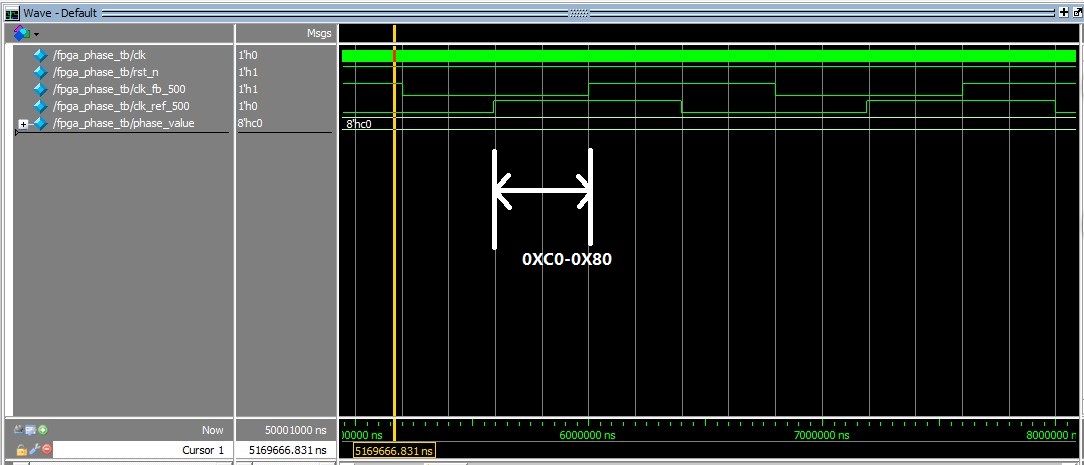

6. 实际仿真如下,当反馈信号滞后于参考信号1/4周期的时候,输出为0xc0,那么高位为1,说明是滞后(0xff-0xc0=0xff/4),不过波形都是相对的周期,换种说法说是超前0xc0也是对的,主要是看对比前一个参考上升沿还是下一个参考上升沿。两种定义都可以。

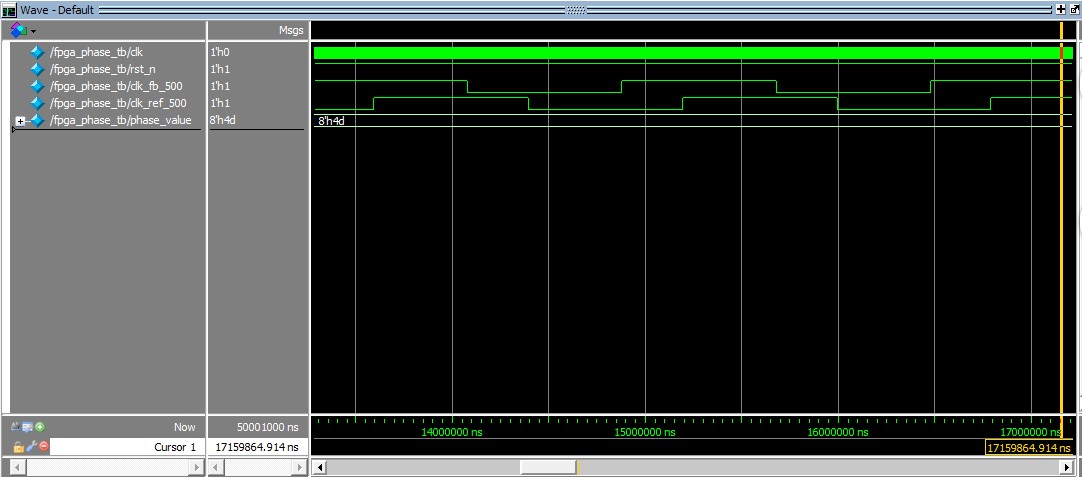

7. 当反馈信号超前于参考信号的时候,输出为0x4d,那么高位为0,说明是超前(0x4d)

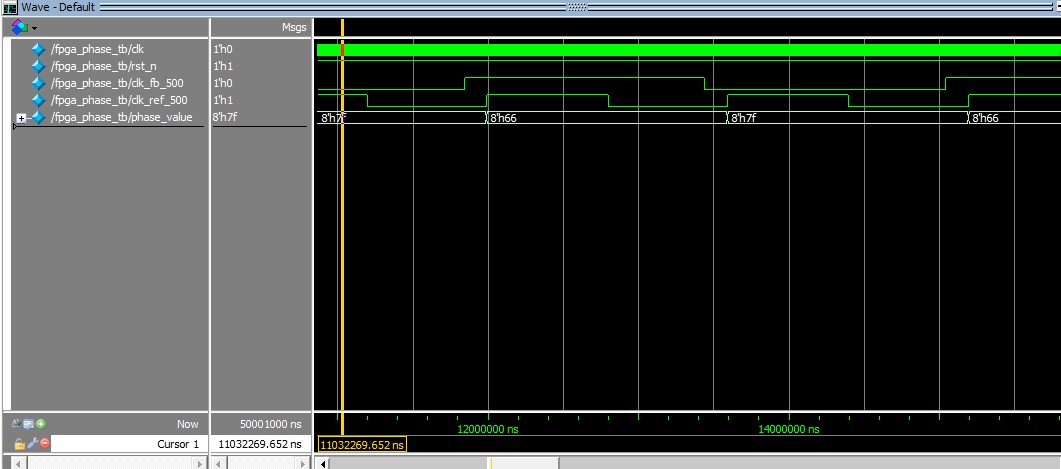

8. 频率差,当反馈信号的频率高于参考信号时,在一个参考时钟周期内会有多个反馈时钟的上升沿出现,PFD的输出将会是最后一个反馈时钟沿对应的寄存的值,是一个负数,表明反馈信号超前参考信号。锁相环路将会降低VCO的输出降低反馈信号的频率。当反馈信号的频率低于参考信号时,在某个参考时钟周期内将不会有反馈信号的上升沿出现,此时PFD会复位触发器,输出对应于最大滞后量的7FH,此时锁相环路将会提高VCO的输出提高反馈信号的频率。下图是输出0X7FH的仿真。当然在下一个周期,仍然会检测到反馈信号的上升沿,所以0X7FH和0X66H间隔出现,证明了本次仿真是正确的。

FPGA数字鉴相鉴频器的开发记录的更多相关文章

- Python全栈开发记录_第一篇(循环练习及杂碎的知识点)

Python全栈开发记录只为记录全栈开发学习过程中一些难和重要的知识点,还有问题及课后题目,以供自己和他人共同查看.(该篇代码行数大约:300行) 知识点1:优先级:not>and 短路原则:a ...

- 你要的fpga&数字前端笔面试题都在这儿了

转自http://ninghechuan.com 你要的FPGA&数字前端笔面试题来了 FPGA&ASIC基本开发流程 题目:简述ASIC设计流程,并列举出各部分用到的工具. 勘误:C ...

- CozyRSS开发记录22-界面退化

CozyRSS开发记录22-界面退化 1.问题1-HtmlTextBlock 找的这个HtmlTextBlock有很严重的bug,有时候显示不完全,有时候直接就崩了.然后看了下代码,完全是学生仔水平写 ...

- CozyRSS开发记录21-默认RSS源列表

CozyRSS开发记录21-默认RSS源列表 1.默认列表 在第一次使用CozyRSS的情况下,我们让它内置五个RSS源吧: 2.响应RSS源的更新 先不处理RSS源列表项的点击,响应下下拉菜单里的更 ...

- CozyRSS开发记录20-CanResizeWithGrip

CozyRSS开发记录20-CanResizeWithGrip 1.窗口样式 首先,WindowStyle有四种: 然后,对于窗口缩放的ResizeMode,也有四种,CanResize和CanRes ...

- CozyRSS开发记录19-窗口标题栏交互

CozyRSS开发记录19-窗口标题栏交互 1.谈谈对mvvm解耦的看法 在使用mvvm时,如何操作窗口,这是一个问题.这个问题的关键点是:mvvm是把view和viewmodel解耦了的,很多写法一 ...

- CozyRSS开发记录18-番外之Atom1.0的支持

CozyRSS开发记录18-番外之Atom1.0的支持 1.对CozyRSS.Syndication批判一番 由于我工作的主要开发语言是c++,所以会看到我的c#代码写得非常朴素,很多语法糖都没有用上 ...

- CozyRSS开发记录17-Html2Xaml

CozyRSS开发记录17-Html2Xaml 1.RssContentView还需要优化 上回做了RssContentView的显示,但是对于rss返回的描述(摘要),连换行的没有,更别说里面还有h ...

- CozyRSS开发记录16-RssContentView显示

CozyRSS开发记录16-RssContentView显示 1.RssContentView的布局和绑定 继续参照原型图来写xaml: 然后在RSSContentFrameViewModel里提供绑 ...

随机推荐

- OC 结构体

void test() { // 这个机构只能在函数内部使用 // 定义一个名为Student的结构体类型 struct Student { int age; // 年龄 char *name; // ...

- 设计模式——外观模式(FacadePattern)

外观模式:为子系统中的一组接口提供一个一致的界面,次模式定义了一个高层接口,这个接口使得这一子系统更加容易使用. UML图: 外观类: package com.cnblog.clarck; /** * ...

- MySQL:数据库入门篇5

1.存储引擎 innodb与MyIASM存储引擎的区别: 1.innodb 是mysql5.5版本以后的默认存储引擎, 而MyISAM是5.5版本以前的默认存储引擎. 2.innodb 支持事物,而M ...

- [USACO15OPEN]haybales Trappe…

嘟嘟嘟 刚开始我以为如果这头牛撞开一个干草堆的话,获得的冲刺距离只有新增的部分,但实际上是加上原来的部分的. 暴力很好写,区间排完序后一次判断每一个区间是否能逃脱,复杂度O(n2). 优化想起来也不难 ...

- 简单实现CombineFileInputFormat

import java.io.DataOutput; import java.io.IOException; import org.apache.hadoop.conf.Configuration; ...

- 手机移动端 web整合

meta基础知识 <!DOCTYPE html> <html> <head> <meta charset="utf-8"> < ...

- LeetCode13.罗马数字转整数 JavaScript

罗马数字包含以下七种字符: I, V, X, L,C,D 和 M. 字符 数值 I 1 V 5 X 10 L 50 C 100 D 500 M 1000 例如, 罗马数字 2 写做 II ,即为两个并 ...

- IOS异步获取数据并刷新界面dispatch_async的使用方法

在ios的开发和学习中多线程编程是必须会遇到并用到的.在java中以及Android开发中,大量的后台运行,异步消息队列,基本都是运用了多线程来实现. 同样在,在ios移动开发和Android基本是很 ...

- 获取APP地图权限

获取APP地图权限 NSLocationWhenUseUsageDescription,在info里面设置为空

- 开发一个c#的数据库连接池

c#操作数据库是一个经典,用习惯了以后真感觉不错,很简单的.现在很多关系数据库都支持c#.c#的ADO.NET规范都遵守. 对于一般的设置,ADO.NET都放在数据库连接字符串上.比如池化,连接超时等 ...