常用IP核

前言

记录自己用到的模块,随时补充。

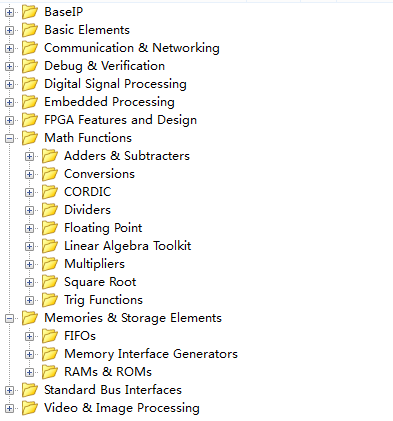

主要分类:

一、常用模块

1-FIFO

- FIFO分为两种,一是输入输出时钟相同(Common clock)的 fifo ;二是输入输出时钟不相同(Independent clocks)

- FIFO常用于:跨时钟域操作和数据位宽转换。例如:两个独立的时钟域,独立的数据位宽,可以利用一个FIFO进行连接

比如FIFO的一端时AD数据采集,另一端时计算机的PCI总线,假设其AD采集的速率为16位 100K SPI,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

- fifo 没有地址,通过 full 和 empty 信号来判断是否可写/读

用 full 和 empty 来判断 fifo 中存储的状态有些极端,可以通过 read_count 和 write_count 来判断存储的状态,write_count: fifo 中存储的余量。

- 进行写复位后,要延迟3个时钟周期才能进行写操作。写复位以后,可通过count引入了3个时钟的延迟

FIFO的一些参数——

FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出(overflow)。

空标志:FIFO已空或将要空时由FIFO的状态电路送出的一个信号,以阻止FIFO的读操作继续从FIFO中读出数据而造成无效数据的读出(underflow)。

FIFO设计的难点在于怎样判断FIFO的空/满状态。为了保证数据正确的写入或读出,而不发生溢出或读空的状态出现,必须保证FIFO在满的情况下,不能进行写操作。在空的状态下不能进行读操作。怎样判断FIFO的满/空就成了FIFO设计的核心问题(特别是Independent clocks的情形)。

常用IP核的更多相关文章

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 从Xilinx FFT IP核到OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109.关于 ...

- 如何用ModelsimSE仿真IP核-以PLL为例

我们之前介绍了如何使用Modelsim SE进行仿真和利用do文件的仿真方法,但是其中待仿真的模块是我们自己编写的Verilog模块,但是在实际工作中,我们的设计中会经常用到FPGA厂商给我们提供的现 ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- Quartus设计FIR滤波器的系数文件格式(适用于FIR II的IP核)

对常用的FIR,我们使用MATLAB的fdatool(或者filterDesigner) 设计滤波器,给定指标,生成系数.为了方便,我们将系数保存到文件,其保存格式比较简介,在此进行说明. 1.FIR ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

随机推荐

- [转] SSH免密码登陆以及穿越跳板机

原文链接:http://www.cnblogs.com/lucantang/p/3315329.html SSH免密码登陆以及穿越跳板机 1. 免密码直连 [user@hostA ~] $ssh ...

- [Backbone]6. Collections.

Define a collection: var AppointmentList = Backbone.Collection.extend({model: Appointment}); RESET t ...

- USACO humble

用set构造,优先队列和堆也能够 /* ID:kevin_s1 PROG:humble LANG:C++ */ #include <iostream> #include <cstdi ...

- ZH奶酪:Ubuntu启动/重启/停止apache服务

Start Apache 2 Server /启动apache服务 # /etc/init.d/apache2 start or $ sudo /etc/init.d/apache2 start Re ...

- ifconf和ifreq

http://blog.csdn.net/jasenwan88/article/details/7763689 用ioctl获得本地ip地址时要用到两个结构体ifconf和ifreq,它们对于大多数人 ...

- 自定义UITableViewCell 的delete按钮

自定义UITableViewCell上的delete按钮 滑动列表行(UITableViewCell)出现删除按钮时,默认是英文“delete”,这份代码片段能够将“delete”变成中文”删除“,甚 ...

- acm2024

/** * C语言合法标识符 */ import java.util.*; public class acm2024 { public static void main(String[] args ...

- Js判断出生年月填写的 是否正确

var r = /^(?:(?!0000)[0-9]{4}-(?:(?:0[1-9]|1[0-2])-(?:0[1-9]|1[0-9]|2[0-8])|(?:0[13-9]|1[0-2])-(?:29 ...

- 解决Unable to load component class org.sonar.scanner.report.ActiveRulesPublisher/Unable to load component interface org.sonar.api.batch.rule.ActiveRules: NullPointerException

解决办法 Delete the directory data/es in your SonarQube installation. Restart SonarQube.

- 【BIRT】使用rptlibrary设置统一数据源

在使用birt开发报表的过程中我们通常会发现,如果直接在报表中写死数据源的话,那么之后如果数据库服务器发生变更,那么所有的报表都得一一去修改数据源 这是一个相当耗时间的过程. 1.首先新建librar ...