常用IP核

前言

记录自己用到的模块,随时补充。

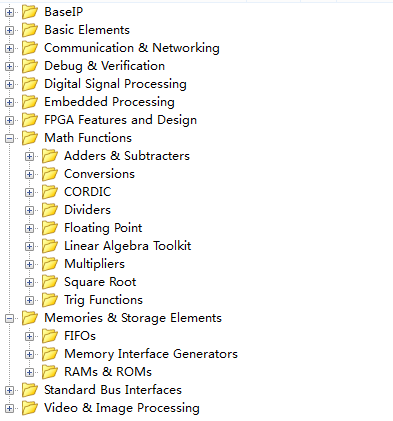

主要分类:

一、常用模块

1-FIFO

- FIFO分为两种,一是输入输出时钟相同(Common clock)的 fifo ;二是输入输出时钟不相同(Independent clocks)

- FIFO常用于:跨时钟域操作和数据位宽转换。例如:两个独立的时钟域,独立的数据位宽,可以利用一个FIFO进行连接

比如FIFO的一端时AD数据采集,另一端时计算机的PCI总线,假设其AD采集的速率为16位 100K SPI,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

- fifo 没有地址,通过 full 和 empty 信号来判断是否可写/读

用 full 和 empty 来判断 fifo 中存储的状态有些极端,可以通过 read_count 和 write_count 来判断存储的状态,write_count: fifo 中存储的余量。

- 进行写复位后,要延迟3个时钟周期才能进行写操作。写复位以后,可通过count引入了3个时钟的延迟

FIFO的一些参数——

FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,以阻止FIFO的写操作继续向FIFO中写数据而造成溢出(overflow)。

空标志:FIFO已空或将要空时由FIFO的状态电路送出的一个信号,以阻止FIFO的读操作继续从FIFO中读出数据而造成无效数据的读出(underflow)。

FIFO设计的难点在于怎样判断FIFO的空/满状态。为了保证数据正确的写入或读出,而不发生溢出或读空的状态出现,必须保证FIFO在满的情况下,不能进行写操作。在空的状态下不能进行读操作。怎样判断FIFO的满/空就成了FIFO设计的核心问题(特别是Independent clocks的情形)。

常用IP核的更多相关文章

- IP核之初——FIFO添加以太网MAC头部

本文设计思路源自明德扬至简设计法.在之前的几篇博文中,由于设计比较简单,所有的功能都是用verilogHDL代码编写实现的.我们要学会站在巨人的肩膀上,这时候就该IP核登场了! 说白了,IP核就是别人 ...

- 从Xilinx FFT IP核到OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109.关于 ...

- 如何用ModelsimSE仿真IP核-以PLL为例

我们之前介绍了如何使用Modelsim SE进行仿真和利用do文件的仿真方法,但是其中待仿真的模块是我们自己编写的Verilog模块,但是在实际工作中,我们的设计中会经常用到FPGA厂商给我们提供的现 ...

- FIFO IP核

转载: 说白了,IP核就是别人做好了的硬件模块,提供完整的用户接口和说明文档,更复杂的还有示例工程,你只要能用好这个IP核,设计已经完成一半了.说起来容易,从冗长的英文文档和网上各个非标准教程中汲取所 ...

- Quartus设计FIR滤波器的系数文件格式(适用于FIR II的IP核)

对常用的FIR,我们使用MATLAB的fdatool(或者filterDesigner) 设计滤波器,给定指标,生成系数.为了方便,我们将系数保存到文件,其保存格式比较简介,在此进行说明. 1.FIR ...

- 调用altera IP核的仿真流程—下

调用altera IP核的仿真流程—下 编译 在 WorkSpace 窗口的 counter_tst.v上点击右键,如果选择Compile selected 则编译选中的文件,Compile All是 ...

- 调用altera IP核的仿真流程—上

调用altera IP核的仿真流程—上 在学习本节内容之后,请详细阅读<基于modelsim-SE的简单仿真流程>,因为本节是基于<基于modelsim-SE的简单仿真流程>的 ...

- (转)modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核)

原地址modelsim10.0C编译ISE14.7的xilinx库(xilinx ip核) 1.打开D:\Xilinx\14.7\ISE_DS\ISE\bin\nt64\compxlibgui.e ...

- Lattice 的 DDR IP核使用调试笔记之DDR 的 仿真

—— 远航路上ing 整理于 博客园.转载请标明出处. 在上节建立完工程之后,要想明确DDR IP的使用细节,最好是做仿真.然后参考仿真来控制IP 核. 仿真的建立: 1.在IP核内的以下路径找到以下 ...

随机推荐

- 1-2Html与CSS的关系

Html和CSS的关系 基于微信的后台开发须要掌握的基础知识包括有:HTML.CSS.JavaScript语言. 以下我们就来了解下这三门技术都是用来实现什么的: 1. HTML是网页内容的载体.内容 ...

- 【Javascript Demo】根据Email地址跳转到相应的邮箱登录页面

我的初步想法是通过指定的邮箱地址自动查找到对应的邮箱登录页面,但是用数据库.js什么的都有局限性,因为各种各样的邮箱太多了,不能都包含的到,网上找了半天都没有找到满意的答案,自己又想不出方法,只能暂时 ...

- Android 视频缩放/放大

1. 原理 不直接改变Codec输出的视频宽高比,而是改变视频播放器窗体的大小. 2. 设置Window 须要将Window设置未能够超出屏幕尺寸 mWindow.setFlags(WindowMan ...

- Python中的乱码

我把写好的Python脚本导入到ArcGIS中的ToolBox中,在本机测试是没有问题的.为了把工具分享给其他人,即在其他电脑上使用,我必须将脚本文件(*.py)导入到工具箱文件(*.tbx) ...

- 机器学习Python实现 SVD 分解

这篇文章主要是结合机器学习实战将推荐算法和SVD进行对应的结合 不论什么一个矩阵都能够分解为SVD的形式 事实上SVD意义就是利用特征空间的转换进行数据的映射,后面将专门介绍SVD的基础概念.先给出p ...

- iOS正則表達式(一)

什么是正則表達式? 正則表達式是对字符串操作的一种逻辑公式. 作用? 在iOS开发中我们通常使用正則表達式来匹配给定的字符串是否符合我们的业务逻辑,比方说用户注冊帐号仅仅能是手机号或者邮箱等.我们还能 ...

- java面试第十四天

包名.类名和属性可以被序列化,方法和构造器不会被序列化的. 静态属性不会被序列化的. 属性会被递归序列化的,也就是一个类中有引用类型的属性,如果这个属性对应的类实现了Serializable接口,在对 ...

- maven org.apache.tomcat.util.bcel.classfile.ClassFormatException: Invalid byte tag in constant pool: 60

maven org.apache.tomcat.util.bcel.classfile.ClassFormatException: Invalid byte tag in constant poo ...

- java随机函数使用方法Random

import java.util.Random; public class RandomNumber{ public static void main(String[] args) { // 使用ja ...

- js 动态增加行删除行

<body> <table id="tableID" border="1" align="center" width=&q ...