Xilinx Altera FPGA中的逻辑资源(Slices VS LE)比较

前言

经常有朋友会问我,“我这个方案是用A家的FPGA还是X家的FPGA呢?他们的容量够不够呢?他们的容量怎么比较呢?”当然,在大部分时候,我在给客户做设计的时候,直接会用到最高容量的产品,因为我们的产品对成本不敏感。不过,在此还是比较一下两家的产品,简单写写一些自己的想法,供大家参考,如有不对的地方,还请指正!

进入正题

要比较Xilinx和Altera的FPGA,就要清楚两个大厂FPGA的结构,由于各自设计的不同,两家的FPGA结构各不相同,参数也各不相同,但可以统一到LUT(Look-Up-Table)查找表上。

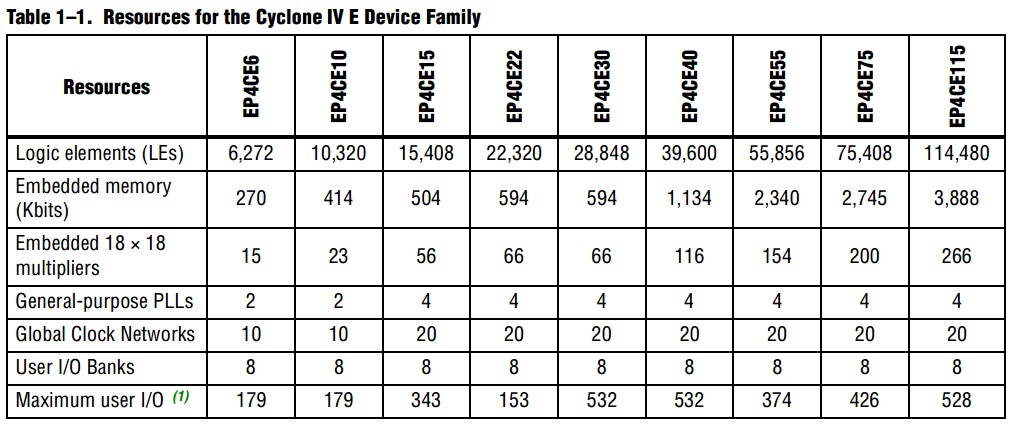

下图就是A家的Cyclone IV系列片子的参数:

可以看到,A家的片子,用的是LE这个术语。

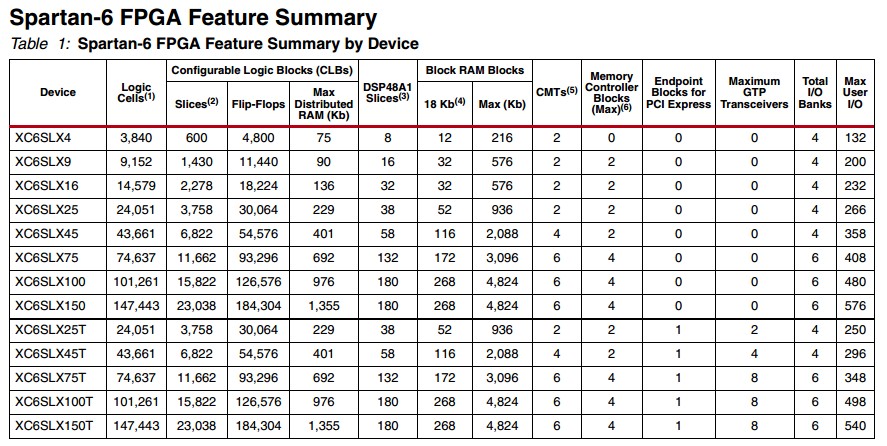

而下图是X家的Spartan-6 片子资料:

X家用的是CLB这个术语作为基本单元。

再看看两家的基本单元有何不同:

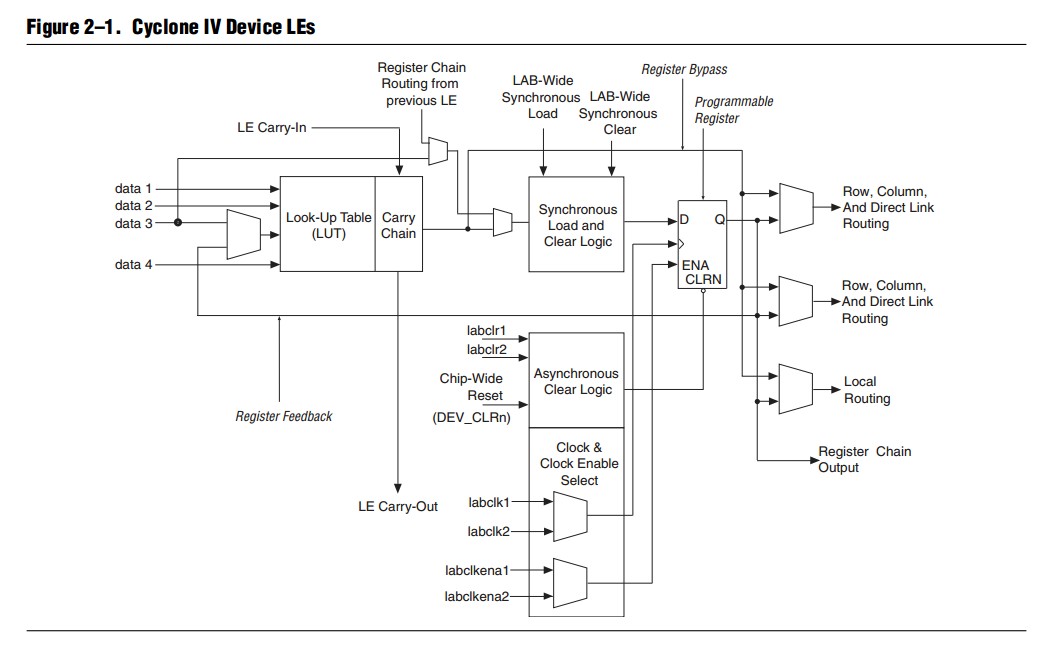

A家的LE如下图:

就是一个4输入LUT+FF构成

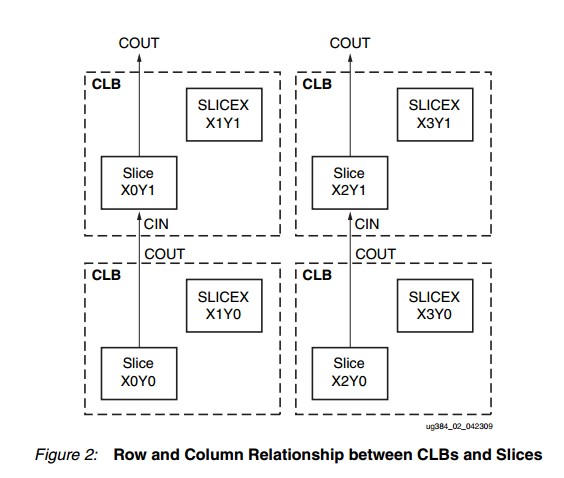

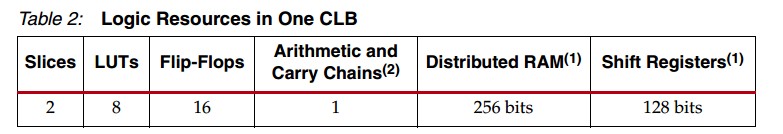

而X家的CLB如下:

一个CLB由2个SLICE构成,一个SLICE含有4个6输入LUT,所以LUT=8*CLB。

这样的话,可以较比一下。EP4CE6基本就和XC6SLX9一个级别。。。。当然A家的片子是4输入LUT远比不上X家的6输入LUT。而X家的S-6片子,一个Slice内部有4个lut,8个FF。简而言之,一个Slice=四个LE。要注意的是A家C5以下的片子是4输入LUT而X家的是6输入LUT,差别也较大。如果不考虑FF,那么一个X家的slice=4个A家的LE。例如XC6SLX16含有2278个slices=EP4CE10(9000LE)的样子。当然,S-6的FF多一倍,达到了18224个。

在Virtex-5中(我们的设计大部分是Virtex,V5V6V7),一个Slice包含了4个LUT和4个FF。所以单纯从逻辑资源来看,S-6一个Slice比V-5的Slice强。当然V5的GTPGTX等等还有IO数量是S-6赶不上的。当然,A家的Cyclone V系列的片子,内部和前几代完全不同,采用了从高端的Stratix系列下放的技术,在新设计时,值得推荐~!

Xilinx Altera FPGA中的逻辑资源(Slices VS LE)比较的更多相关文章

- Altera FPGA中的pin进一步说明

最近END china上的大神阿昏豆发表了博文 <FPGA研发之道(25)-管脚>,刚好今天拿到了新书<深入理解Altera FPGA应用设计>第一章开篇就讲pin.这里就两者 ...

- 1. FPGA内部的逻辑资源

CLB(包括LUT.加法器.寄存器.MUX(多路选择器)) 时钟网络资源(全局时钟网络,区域时钟网络,IO时钟网络),理解时钟网络的本质和意义 时钟处理单元(PLL,DCM),理解时钟网络资源和时钟处 ...

- Altera FPGA中的pin简介

第一步要看的肯定是pin planner ,这个是黑金四代EP4CE15F17C8的视图 先就是发现他们pin有不同的颜色区域,分别对应不同的bank,应该是有的设计里面要求pin在同一个bank吧( ...

- FPGA 设计怎样进行面积优化(逻辑资源占用量优化)

FPGA面积优化 1 对于速度要求不是非常高的情况下,我们能够把流水线设计成迭代的形式,从而反复利用FPGA功能同样的资源. 2 对于控制逻辑小于共享逻辑时,控制逻辑资源能够用来复用,比如FIR滤波器 ...

- 巧用FPGA中资源

随着FPGA的广泛应用,所含的资源也越来越丰富,从基本的逻辑单元.DSP资源和RAM块,甚至CPU硬核都能集成在一块芯片中.在做FPGA设计时,如果针对FPGA中资源进行HDL代码编写,对设计的资源利 ...

- 7.FPGA中的同步复位与异步复位

1.异步复位 always @ ( posedge sclk or negedge s_rst_n ) if ( !s_rst_n ) d_out <= 1'b0; else d_out < ...

- 三叔学FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- FPGA系列之一:Cyclone V中的时钟资源

之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来得及系统地学习,最近在做算法到电路的实现,正好系统学习 ...

- 在FPGA中使用for循环一定浪费资源吗?

渐渐地,发现自己已经习惯于发现细节,喜欢打破常规,真的非常喜欢这种feel. 相信很多人在书上或者博文上都有提出“在FPGA中使用for语句是很占用资源的”的观点,特权同学也不例外.那么,这种观点正确 ...

随机推荐

- PAT 甲级 1064 Complete Binary Search Tree

https://pintia.cn/problem-sets/994805342720868352/problems/994805407749357568 A Binary Search Tree ( ...

- HBase 架构与工作原理3 - HBase 读写与删除原理

本文系转载,如有侵权,请联系我:likui0913@gmail.com 一.前言 在 HBase 中,Region 是有效性和分布的基本单位,这通常也是我们在维护时能直接操作的最小单位.比如当一个集群 ...

- JS贪吃蛇小游戏

效果图展示: 具体实现代码如下: (1)html部分 !DOCTYPE html> <html> <head> <meta charset="utf-8& ...

- VBA笔记(一)——基础配置

开启VBA编程环境——VBE 方法一:按<Alt+F11>组合建 方法二:查看代码 宏设置 当然启用宏的设置方式不同,宏的启动方式也不一样. 首先打开“office 按钮”,选择“exce ...

- 第211天:git和github的区别和使用详解

一.git 1.什么是git 它是一个源代码管理工具,在一个项目中,凡是由开发人员编写的都算是源代码,源代码有必要管理起来,让源代码可以被追溯,主要记录每次变更了什么,谁主导这次变化.人为的维护比较麻 ...

- python自动化之读写

############################################################################# #############在Windows上 ...

- BZOJ5101 POI2018Powódź(并查集)

如果某个格子的积水量超过了该格子的某个挡板高度,那么挡板另一端的积水量就会与其相同.看起来是一个不断合并的过程,考虑并查集.枚举深度,维护每个连通块内的方案数,深度超过某挡板高度时,将两端的连通块合并 ...

- Stack Overflow上关于Java Collections的几个常见问题

下面列出Stack Overflow上最常见的几个关于Java Collections的问题并给出答案. 1. 什么时候用LinkedList,什么时候用ArrayList? ArrayList是使用 ...

- 如何让自己的广播只让指定的 app 接收?

1.自己的应用(假设名称为应用 A)在发送广播的时候给自己发送的广播添加自定义权限,假设权限名为:com.itheima.android.permission , 然后需要在应用 A 的 Androi ...

- 实现运行在独立线程池的调度功能,基于Spring和Annotation

使用Spring的注解(@Scheduled)声明多个调度的时候,由于其默认实现机制,将导致多个调度方法之间相互干扰(简单理解就是调度不按配置的时间点执行). 为了解决该问题尝试了修改线程池大小,但是 ...