[Xilinx]Modelsim独立仿真Vivado生成的PLL核

EDA Tools:

1、Vivado 2015.1(64-bit)

2、Modelsim SE-64 10.1c

Time:

2016.05.26

-----------------------------------------------------------------------------------

喜欢使用Modelsim工具独立进行代码的仿真。也不是Vivado自带的不好(至少目前的小代码没啥影响)

只是在一个vivado工程进行仿真时,添加文件的功能没用太明白,好烦!

--

大前提:和Altera一样,也是需要先将底层的模块编译为库。这个步骤其实是一劳永逸。编译一次,以后

仿真用到时,只需添加使用到的编译库的目录即可,节省时间成本。

当然,如若乐意,你也可自行添加底层模块的源码到Modelsim当前工程。

--

Vivado更为便捷的是直接提供GUI按钮来一键编译Modelsim仿真所需的库(当然,并非所有都编译)。

-----------------------------------------------------------------------------------

tb代码:

`timescale 1ns/1ns module tb; reg clk_in1 = ;

reg reset = ; always # clk_in1 = !clk_in1; initial begin

#;

repeat() @(posedge clk_in1);

reset <= ;

end //全局复位

glbl glbl(); pll_OSC_27M_system pll_OSC_27M_system_inst

(

// Clock in ports

.clk_in1(clk_in1), // input clk_in1

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

.clk_out4(clk_out4), // output clk_out4

// Status and control signals

.reset(reset), // input reset

.locked(locked)// output locked

); initial begin

#;

repeat() @(posedge clk_in1);

$stop;

end endmodule

试验过程:

1、最开始tb里面是没有第18行的。

然后,源码添加tb.v、pll_name.v和pll_name_clk_wiz.v这三个模块。

这时,会提示pll_name_clk_wiz模块里面例化到的一些底层模块找不到。

具体是:

Instantiation of 'PLLE2_ADV' failed.

Instantiation of 'BUFG' failed.

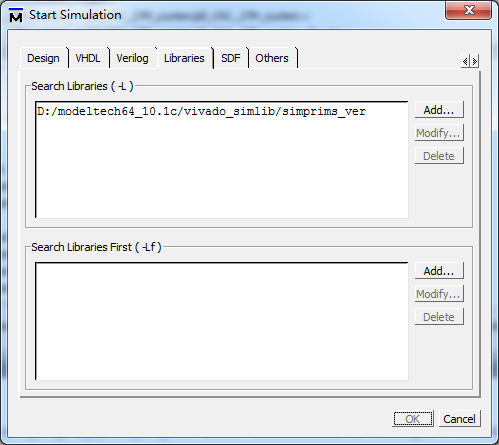

2、根据经验,这就是需要添加搜索库的路径。

具体GUI操作就是:Simulate -->Start Simulation

默认是Design标签处于激活,先切换到Libraries标签,

在Search Libraries(-L)添加需要使用到的库(这里仅需要simprims_ver)的路径。

比如我的情况是:

接着,再切换到Design标签,展开work,选择tb(最顶层模块),然后选择ok。

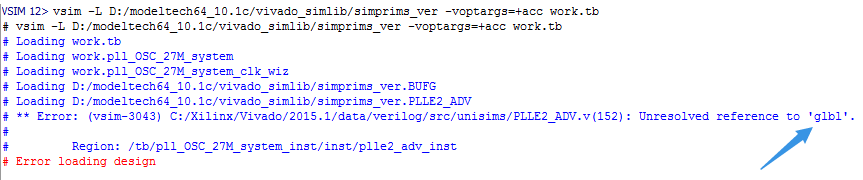

3、但发现还是有问题!截图如下:

网络搜索下,了解这是xilinx全局复位的模块。

该模块在C:\Xilinx\Vivado\2015.1\data\verilog\src

路径其实在上面Error提示的一部分。

4、于是,自己copy一份glbl.v到当前工程,进行编译。

但还是弹出相同的错误提示。

只好打开PLLE2_ADV.v模块的代码,搜索glbl关键字。

发现代码有2处用到glbl,具体分别是:

第152行:

tri0 GSR = glbl.GSR;

第1645行:

assign (weak1, strong0) glbl.PLL_LOCKG = (glock == ) ? : p_up;

----

注意到上面都是层次调用。

换言之,我们需要tb例化glbl,且例化名只能取glbl。

这便有了前面pose的tb代码的第18行!

-----------------------------------------------------------------------------------

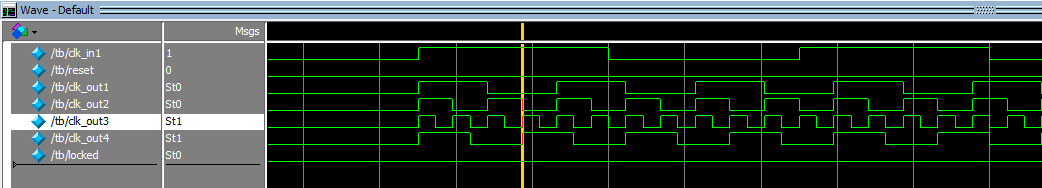

仿真波形:

这是全局视图。可见locked信号还是一样,高电平表示时钟锁住,呈稳定状态。

这是局部视图1。此时刚开始产生输出时钟波形,但locked尚未有效!

注意到PLL设置的同相对应的是各个输出时钟的上升沿。

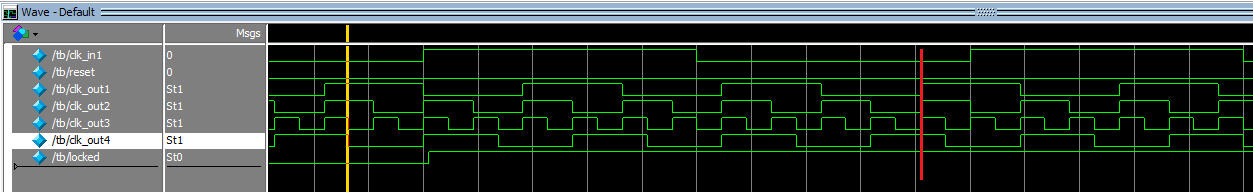

这是局部视图2。此时locked正要拉高。

----------------------------------

OVER!

[Xilinx]Modelsim独立仿真Vivado生成的PLL核的更多相关文章

- modelsim 独立仿真vivado的IP核及仿真脚本

Modelsim独立仿真vivado的IP 最近一直在做local dimming项目的FPGA硬件实现,算法的其中一步就是直方图统计,即数字图像的某一灰度级的像素数,这个直方图的源码找了半天才搞到, ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- Vivado&ISE&Quartus II调用Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- Viavdo&ISE&Quartus II级联Modelsim级联仿真

博主一直致力寻找高效的工作方式,所以一直喜欢折腾软件,从刚开始只用软件IDE自带的编辑器,到Notepad++,再到后来的Vim,从用ISE14.7自带的Isim仿真,到发现更好的Modelsim,再 ...

- ddr3调试经验分享(一)——modelsim实现对vivado中的MIG ddr3的仿真

Vivado中的MIG已经集成了modelsim仿真环境,是不是所有IP 都有这个福利呢,不知道哦,没空去验证. 第一步:使用vivado中的MIG IP生成一堆东西 ,这个过程自己百度.或者是ug5 ...

- Xilinx与modelsim的仿真联调

关于Xilinx与modelsim的仿真联调,尤其是仿真环境的搭建,网上的信息都比较零散,我当初在联调的时候遇到比较多的问题,也是折腾了两天才弄好,下面的步骤我总结得非常详细,可以帮助大家少走弯路. ...

- Modelsim se仿真Xilinx IPcore

Modelsim se仿真Xilinx IPcore 方法:先写好do文件常规框架,根据modelsim报错再添加ise IP核库仿真文件.注:记得添加并仿真glbl.v全局控制仿真文件到sim/is ...

- Vivado 与 Modelsim 联合仿真

1 编译库 用命令行 用vivado工具 vivado 有很多 IP核的接口 已经与 ISE的核 不太一样了,比如fir ,接口就是这样的: fir_lp fir_lp_ip( .aclk ( ...

- 搭建Modelsim SE仿真环境-使用do文件仿真

本章我们介绍仿真环境搭建是基于Modelsim SE的.Modelsim有很多版本,比如说Modelsim-Altera,但是笔者还是建议大家使用Modelsim-SE,Modelsim-Altera ...

随机推荐

- EMC起步:华为交换机拆解

[作者:byeyear Email:east3@163.com 转载请保留此行] 1. 静电抗扰 理想情况下,我们的系统是一个中空且密闭的金属盒子,根据电磁场理论,外界的任何静电源都不可能 ...

- canvas ---个性时钟

<!DOCTYPE html> <html> <head> <meta charset="utf-8"> <meta name ...

- NPOIHelper

public class NPOIHelper { public static void WriteDataToExceel(string fileName, DataSet ds) { if (Fi ...

- 深入理解Session与Cookie

Session与cookie的作用都是为了保持访问用户与后端服务器的交互状态. cookie通过把所有要保存的数据通过HTTP协议的头部从客户端传递到服务端,又从服务端再传回到客户端,所有的数据都存储 ...

- Python mysql 操作小类,供大家用用

import binascii import os import linecache import time #add pyDes path #sys.path.append("/data1 ...

- [C#对sql操作]C#对sql server 2008数据库操作

using System.Data; using System.Data.SqlClient SqlConnection conn = new SqlConnection(System.Configu ...

- 《所用到的AJAX技术基础》

来自百度网页,w3cshool网页:AJAX = Asychronous JavaScript and XML,翻译成中文为:异步的JavaScript XML. 异步的意思就是不重新加载整个页面,后 ...

- Java多线程之并发协作生产者消费者设计模式

两个线程一个生产者个一个消费者 需求情景 两个线程,一个负责生产,一个负责消费,生产者生产一个,消费者消费一个 涉及问题 同步问题:如何保证同一资源被多个线程并发访问时的完整性.常用的同步方法是采用标 ...

- 两种流行Spring定时器配置:Java的Timer类和OpenSymphony的Quartz

1.Java Timer定时 首先继承java.util.TimerTask类实现run方法 import java.util.TimerTask; public class EmailReportT ...

- Zip文件压缩(加密||非加密||压缩指定目录||压缩目录下的单个文件||根据路径压缩||根据流压缩)

1.写入Excel,并加密压缩.不保存文件 String dcxh = String.format("%03d", keyValue); String folderFileName ...