S3C2440时钟体系

注:以下内容学习于韦东山老师arm裸机第一期视频教程

一. 2440时钟简介

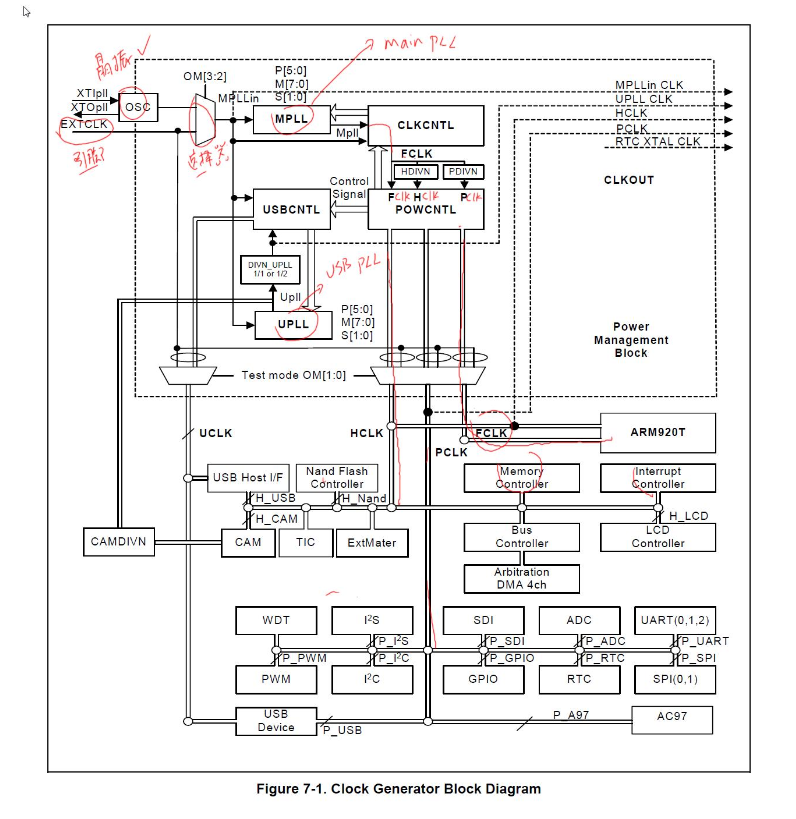

1.1 2440是一个SOC(system on chip)系统,不仅有很多CPU,还有很多外设,在2440芯片手册有系统框架图如下:

2440框架图中,不仅有CPU,而且有很多外设,其中外设分为两部分,一部分是AHB总线,一部分是APB总线

1.2 AHB总线

1.2.1 LCD控制器

1.2.2 USB控制器

1.2.3 NAND控制器

1.2.4 内存控制器

1.2.5 摄像头接口

1.2.6 中断控制器

1.2.7 电源管理等等

1.3 APB总线

1.3.1 UART

1.3.2 USB device

1.3.3 I2C

1.3.4 GPIO

1.3.5 RTC

1.3.6 ADC

1.3.7 定时器等等

1.4 因此引入了三个时钟,FLCK,HCLK,PCLK

cpu工作与FCLK,最大工作频率400MHZ

AHB总线工作于HCLK,最大工作频率136MHZ

APB总线工作与PCLK,最大工作频率68MHZ

二.时钟的获取

2.1 2440时钟体系框图如下

2.2 时钟源的选择

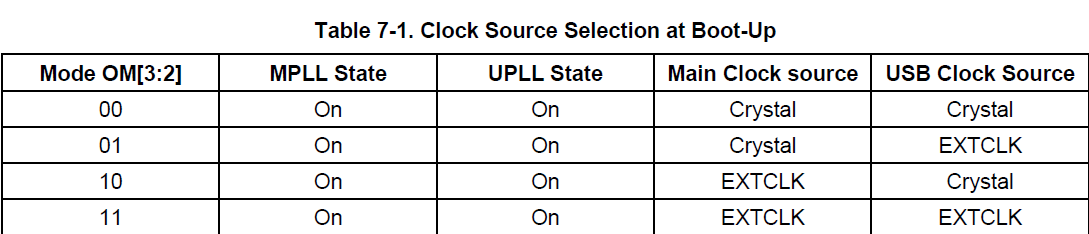

从图中看出,时钟源有两个分别是外部晶振和引脚,通过OM[3:2]来选择,模式选择如下图

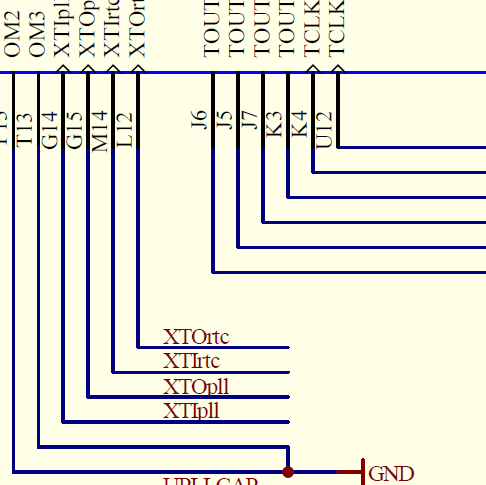

在2440的原理图上,可以看到OM3,OM2都接到了GND上,因此会选择使用外部晶振作为输入

2.3 时钟体系流程

12MHZ晶振通过MPLL锁相环得到FLCK,CPU直接使用FCLK,FCLK通过PDIV分频得到PCLK提供给APB总线上的设备使用,

FCLK通过HDIV分频得到HCLK提供给AHB总线上使用

12MHZ晶振也会经过UPLL锁相环提供给USB使用

三.程序的编写

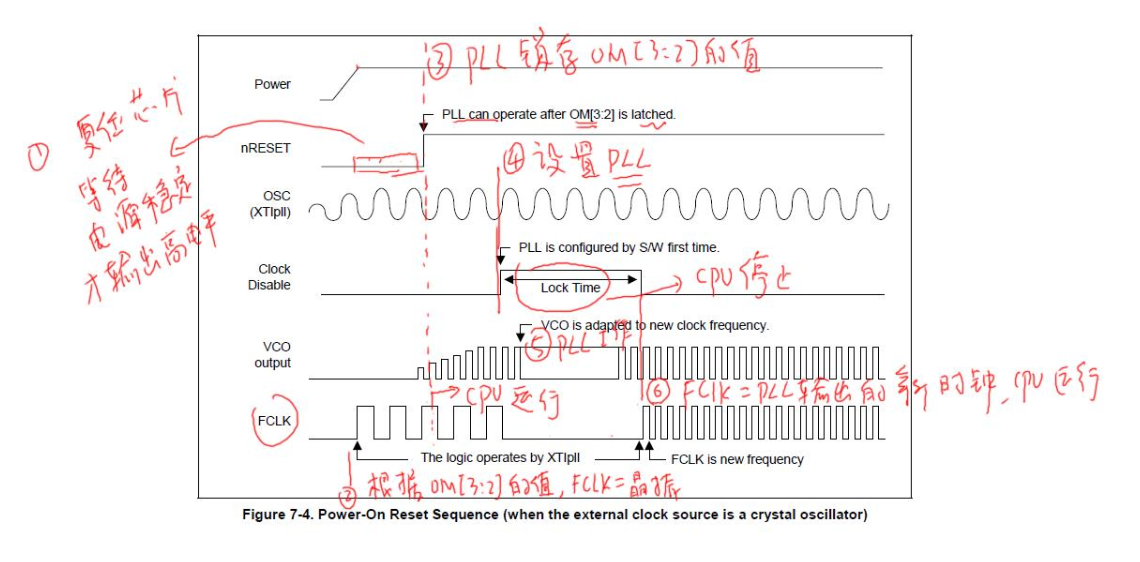

3.1 时序图如下:

注:一旦设置PLL,就会锁定LOCK TIME 直到PLL输出稳定,然后CPU开始工作于新的频率FCLK

3.2 流程分析

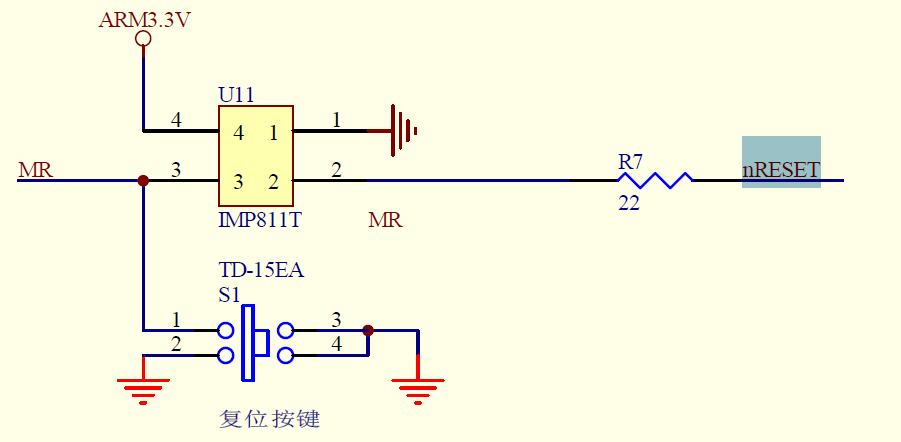

3.2.1 一上电,复位引脚会维持一段时间(等待电源稳定),通过复位芯片来维持,如下:

3.2.2 根据OM[3:2]的值FCLK等于晶振的12M

3.2.3 PLL锁存OM[3:2]的值,同时CPU开始运行(复位引脚被拉高)

3.2.4 设置PLL

3.2.5 在CPU停止运行一段时间设置PLL

3.2.6 设置完成后FLCK等于PLL输出的新的频率

3.3 寄存器的设置(目的FCLK=400MZH, HCLK=100MZH, PCLK=50MHZ)

3.3.1 设置LOCKTIME寄存器,决定MPLL和UPLL的LOCKTIME

设置为默认值即可

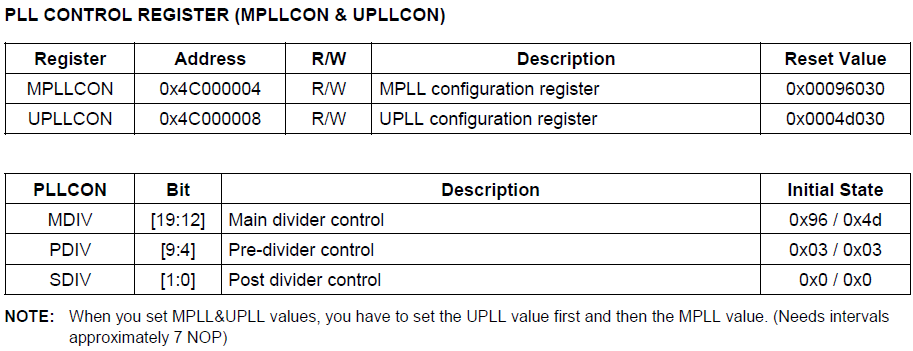

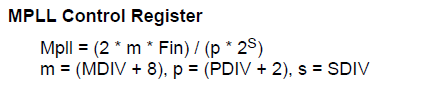

3.3.2 设置MPLLCON/UPLLCON寄存器,决定FCLKi,如下图

其中公式如下图:

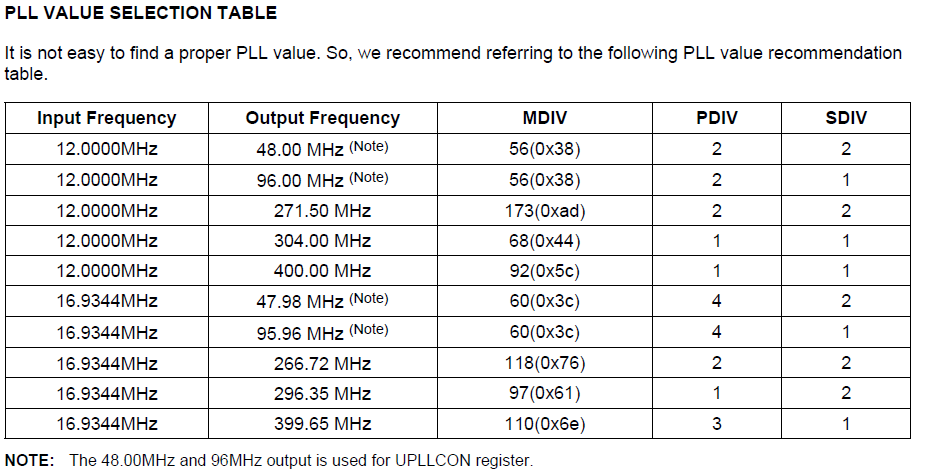

参考设置值如下,我们选择MDIV=92, PDIV = 1, SDIV=1即可设置FCLK = 400MHZ:

MPLLCON = (92 << 12) | (1 << 4) | (1 << 0);

3.3.3 设置CLKCON寄存器(关掉用不到的设备)

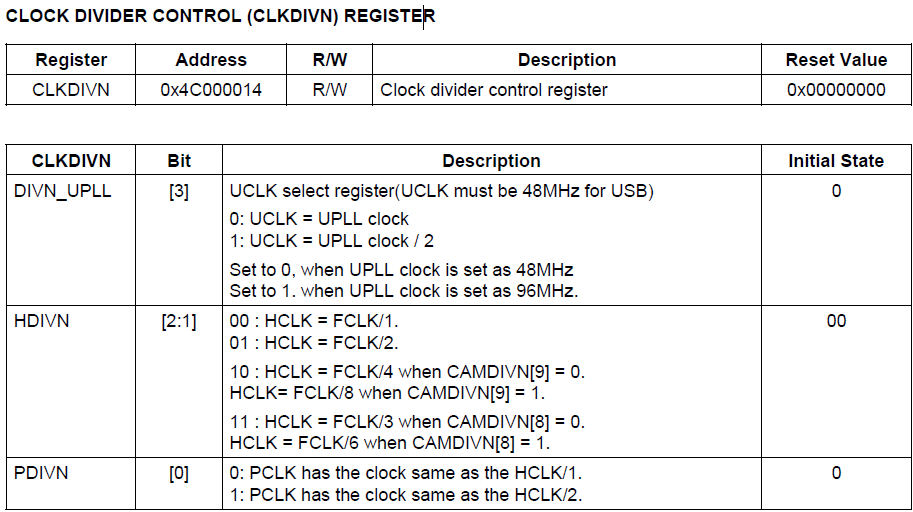

3.3.4 设置CLKDIVN寄存器,决定HCLK,PCLK,如下图:

首先要设置bit[2:1]为10,这时HCLK=FCLK/4=100MHZ,但是需要CAMDIVN[9]=0(默认值就是0)

设置bit[0]为1,这时PCLK=HCLK/2=50MHZ

bit[3]取默认值

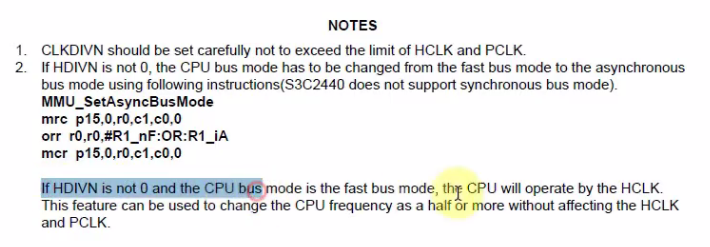

3.3.5 如果HDIVN不等于0,CPU必须设置为异步模式,CPU会工作于HCLK,如下图

对于此处的汇编命令 orr r0,r0,#R1_nF:OR:R1_iA ,查阅相关资料大概了解了一下:【它扯到了协处理器P15的C1寄存器】可以参考以下地址了解协处理器P15(https://www.cnblogs.com/lifexy/p/7203786.html)

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000;R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

3.3.6 提高系统时钟代码如下(FCLK=400MHZ,HCLK=100MHZ,PCLK=50MHZ):

.text

.global _start

_start:

/* 1.关闭看门狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 2.设置时钟 */

/* 2.1 设置LOCKTIME(0x4C000000)=0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* 2.2 设置CLKDIVN(0x4C000014) = 0x5 FCLK : HCLK : PCLK = 400m : 100m : 50m*/

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 2.3 设置CPU处于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 /* #R1_nF:OR:R1_iA */

mcr p15,0,r0,c1,c0,0

/* 2.4 设置MPLLCON(0x4C000004)=(92<<12) | (1 << 4) | (1 << 0)

* m = MDIV + 8 = 100

* p = PDIV + 2 = 3

* s = SDIV = 1

* Mpll = (2 * m * Fin) / (p * 2 ^ s)= (2 * 100 * 12) / (3 * 2 ^ 1) = 400MHZ

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12) | (1 << 4) | (1 << 0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 然后CPU工作于新的频率FCLK

*/

/* 3.设置栈

* 自动分辨NOR启动或者NAND启动

* 向0地址写入0,在读出来,如果写入则是NAND,否则是NOR

*/

ldr r0, =0

ldr r1, [r0] /* 读出原来的值备份 */

str r0, [r0] /* 向0地址写入0 */

ldr r2, [r0] /* 再次读出来 */

cmp r1, r2

ldr sp, =0x40000000 + 4096 /* nor启动 */

moveq sp, #4096 /* nand启动 */

streq r1, [r0] /* 恢复原来的值 */

bl main

halt:

b halt

S3C2440时钟体系的更多相关文章

- s3c2440裸机-时钟编程(一、2440时钟体系介绍)

1.总线框架 下图是2440的总线框架,其中有AHB(Advanced High performance Bus)高速总线,APB(Advanced Peripheral Bus)外围总线. 不同总线 ...

- 第010课_掌握ARM芯片时钟体系

from:第010课_掌握ARM芯片时钟体系 第001节_S3C2440时钟体系结构 S3C2440是System On Chip(SOC),在芯片省不仅仅有CPU,还有一堆外设. 至于有哪些外设,可 ...

- S5PV210 时钟体系分析

S5PV210 时钟体系 如下面时钟结构图所示,S5PV210 中包含 3 大类时钟域, 分别是主系统时钟域(简称 MSYS).显示相关的时钟域(简称 DSYS). 外围设备的时钟域(简称 PSYS) ...

- 第九篇:S3C2400时钟体系

S3C2400时钟体系 S3C2400时钟配置流程 该学习板使用了外部晶振12Mhz 晶振--->经过MPLL(锁相环) --->(倍频得到)FCLK--->(对FCLK分频得到)H ...

- S3C2440时钟配置

参考: http://blog.csdn.net/mr_raptor/article/details/6555734 http://blog.csdn.net/mjx91282041/article/ ...

- S3C2440时钟系统详解

在讲述系统时钟之前,因为这些设备都是挂靠在系统时钟上的,所以必须先说系统时钟,S3C2440的时钟系统如下 外部时钟源分两种,晶振或者外部频率,由om3-2选择,时钟电路根据两种选择也有两种 我们来分 ...

- S3C2440 时钟设置分析(FCLK, HCLK, PCLK)

时钟对于一个系统的重要性不言而喻,时钟决定了系统发送数据的快慢,高性能的芯片往往能支持更快速度的时钟,从而提供更好的体验. S3C2440的输入时钟频率是12MHZ,对于这款芯片,显然速度是不够的,所 ...

- S3C2440时钟体系结构

任意一款单板,我们了解其时钟都是通过时钟树来的. 这里没有全部截完,只是讲解时钟来源,OSC代表晶振,这说明我们的时钟可以来至晶振OSC也可以来至外部输入EXTCLK,这是通过OM选择器来完成的. 2 ...

- ARM S3C2440 时钟初始化流程

1.设置lock time 2.设置分频系数 3.设置CPU到异步工作模式 4.设置 FCLK 了解 芯片的时钟原理图,以及寄存器的作用 了解芯片的晶振频率,锁相环,分频系数,以及有哪些时钟

随机推荐

- Open Flash Chart 简介

http://www.ibm.com/developerworks/cn/opensource/os-cn-ecl-ofc/ Open Flash Chart(OFC)是一个开源的 Flash 图表绘 ...

- 违章查询免费api接口代码

能够依据城市+车牌号+发动机号查询违章信息列表. 违章实体类 package org.wx.xhelper.model; /** * 违章实体类 * @author wangxw * @version ...

- Rsync命令的使用

Rsync的命令格式能够为下面六种: rsync [OPTION]- SRC DEST rsync [OPTION]- SRC [USER@]HOST:DEST rsync [OPTION]- [US ...

- 【翻译自mos文章】注意: ASMB process exiting due to lack of ASM file activity

注意: ASMB process exiting due to lack of ASM file activity 參考原文: NOTE: ASMB process exiting due to la ...

- [LeetCode][Java] 4Sum

题目: Given an array S of n integers, are there elements a, b, c, and d in S such that a + b + c + d = ...

- hdu 1248 寒冰王座(暴力)

寒冰王座 Time Limit: 2000/1000 MS (Java/Others) Memory Limit: 65536/32768 K (Java/Others) Total Submi ...

- C++ 函数模板与类模板(使用 Qt 开发编译环境)

注意:本文中代码均使用 Qt 开发编译环境,如有疑问和建议欢迎随时留言. 模板是 C++ 支持参数化程序设计的工具,通过它可以实现参数多态性.所谓参数多态性,就是将程序所处理的对象的类型参数化,使得一 ...

- codeforce1070 2018-2019 ICPC, NEERC, Southern Subregional Contest (Online Mirror, ACM-ICPC Rules, Teams Preferred) 题解

秉承ACM团队合作的思想懒,这篇blog只有部分题解,剩余的请前往星感大神Star_Feel的blog食用(表示男神汉克斯更懒不屑于写我们分别代写了下...) C. Cloud Computing 扫 ...

- Hadoop之父Doug Cutting:Lucene到Hadoop的开源之路

Hadoop之父Doug Cutting:Lucene到Hadoop的开源之路 Doug Cutting,凭借自己对工作的热情和脚踏实地的态度,开创了Lucene和Nutch两个成功的开源搜索引擎项目 ...

- bzoj3907 网格 & bzoj2822 [AHOI2012]树屋阶梯——卡特兰数+高精度

题目:bzoj3907:https://www.lydsy.com/JudgeOnline/problem.php?id=3907 bzoj2822:https://www.lydsy.com/Jud ...