FPGA-信号边缘检测

在FPGA逻辑电路中,输入信号的边缘检测是一个常用的操作,这算是FPGA的基本功之一。

信号边缘检测应用十分广泛,例如:通信协议的时序操作,按键的检测等,都应用到按键的检测。按键的检测分为上升沿和下降沿两种,基本的检测思想是一致的。本博客的思想是先介绍阻塞和非阻塞两种赋值,在理解这个的基础上然后去分析边缘检测。这里,首先分析一下Verilog语言中阻塞赋值(=)和非阻塞赋值(<=)的区别,给出相应的案例来帮助理解:

module prj1(in,b,c,d,clk,rst_n); input in;

input clk;

input rst_n;

output b,c,d;

reg b,c,d; always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

b <=;

c <=;

d <=;

end

else begin

b <=in;

c <=b;

d <=c;

end

end

endmodule

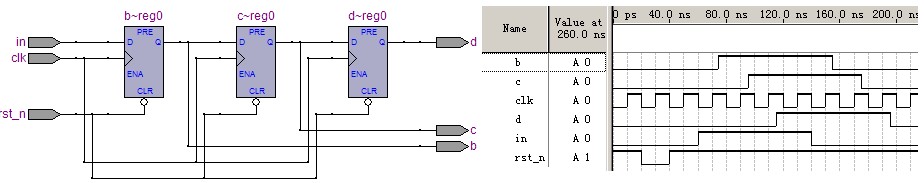

这个目的是为了展示非阻塞赋值过程中的时序变化,对应的RTL电路图和仿真波形如下图:

从仿真图可以看书,b,c,d是在每个时钟后依次传递的,如果采用阻塞赋值,如果in改变,那么b,c,d立刻改变,这个就在这里不给出仿真。

阻塞赋值和非阻塞赋值的另外一个区别在于综合的时候,如果输出只有d,bc作为中间变量,阻塞赋值在综合的过程中会自动省略掉中间过程。给出如下仿真,理解更为清楚

module prj1(in,b,c,clk,rst_n); input in;

input clk;

input rst_n;

output b,c;

reg b,c, e,f, m,n;

/* <= */

always @(posedge clk or negedge rst_n) begin

if(!rst_n) b <=;

else begin

e <=in;

f <=e;

b <=f;

end

end

/* = */

always @(posedge clk or negedge rst_n) begin

if(!rst_n) c=;

else begin

m = in;

n = m;

c = n;

end

end

endmodule

综合后结果如图,可以看出,采用阻塞赋值,综合后的逻辑单元只有一个,中间变量m,n直接省去了。

信号边缘检测:

回归主题,现在谈谈边缘检测思想。我们姑且这么叫:b<=in; status<=b 称为 in到status的一次延迟赋值(延迟时间为一个时钟),in到status的n次延迟就以此类推。

输入 in: 1 1 1 1 1 0 0 0 0 0 0 0 1 1 1

一次延迟 delay1: x 1 1 1 1 1 0 0 0 0 0 0 0 1 1 1

输入取反 ~in: 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0

一次延迟取反 ~delay1:x 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0

上升沿检测:(~delay1)&in --in bit13

下降沿检测:(~in)&delay1 --in bit6

说明:针对边缘毛刺多的地方,比如按键的消除抖动,这里面的延迟需要设定够大(比较好的按键消抖时间20ms左右),通过对时钟的分频进行一次延迟赋值,这样子就能够消除延迟中的抖动,并且能够很好的检测出来按键的边缘。

给出一个简单的边缘检测程序:

module prj1(clk,rst_n,in,pos_edge,neg_edge); input clk,rst_n,in;

output pos_edge,neg_edge; reg delay1;

reg pos_edge,neg_edge; always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

delay1<=;

pos_edge<=;

neg_edge<=;

end

else begin

delay1<=in;

pos_edge <=(~delay1)∈

neg_edge <=(~in)&delay1;

end

end endmodule

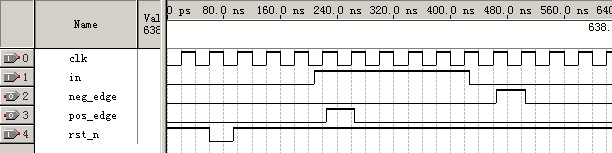

仿真结果如图:

FPGA-信号边缘检测的更多相关文章

- FPGA中的时序分析(一)

谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获.笔者 ...

- 【黑金原创教程】【TimeQuest】【第五章】网表质量与外部模型

声明:本文为黑金动力社区(http://www.heijin.org)原创教程,如需转载请注明出处,谢谢! 黑金动力社区2013年原创教程连载计划: http://www.cnblogs.com/al ...

- STM32之中断

在STM32(Cortex-M3)中没有显示的代码拷贝,只有启动代码进行了向量的初始化,一直以为是编译器在程序影像中自己完成了相关向量的拷贝,即,拷贝到固定的NVIC区,事实上并不是这样,cortex ...

- TIMEQUEST学习之黑金动力(四)

现在知道时序约束主要是FPGA to ic,或者ic to FPGA. 上图可以表示FPGA to IC, IC to FPGA. fpga2ic:fpga2ext 是 fpga 致 ic 信号的走线 ...

- 使用ChipScope Pro调试硬件

chipscope_icon提供与其他ChipScope内核的通信 chipscope_opb_iba促进传统片上外设总线(OPB)事务的监控 chipscope_plb_iba便于监控处理器本地总线 ...

- 基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- 基于 FPGA 的图像边缘检测

本文主要内容是实现图像的边缘检测功能 目录 mif文件的制作 调用 ip 核生成rom以及在 questasim 仿真注意问题 灰度处理 均值滤波:重点是3*3 像素阵列的生成 sobel边缘检测 图 ...

- 【转】基于FPGA的Sobel边缘检测的实现

前面我们实现了使用PC端上位机串口发送图像数据到VGA显示,通过MATLAB处理的图像数据直接是灰度图像,后面我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测.中值滤波.Can ...

- 关于 FPGA 内部信号扇入扇出

扇入.扇出系数 扇入系数是指门电路允许的输入端数目.一般门电路的扇入系数为1—5,最多不超过8.扇出系数是指一个门的输出端所驱动同类型门的个数,或称负载能力.一般门电路的扇出系数为8,驱动器的扇出系数 ...

随机推荐

- virtualbox 复制虚拟机提示uuid is exists

C:\Program Files\Oracle\VirtualBox>VBoxManage.exe internalcommands sethduuid D:毛毛草\virtual\ubuntu ...

- SPOJ:Dandiya Night and Violence(Bitset优化)

It is Dandiya Night! A certain way how dandiya is played is described: There are N pairs of people p ...

- RadioGroup和RadioButton

Activity_main.xml <LinearLayout xmlns:android="http://schemas.android.com/apk/res/android&qu ...

- Eclipse中删除导入的jar包,总是报错?已解决!

参考百度经验 http://jingyan.baidu.com/article/851fbc37c7512e3e1f15abec.html

- VS2008 视图资源.rc无法加载的问题及解决方法

VS2008 视图资源.rc无法加载 1.首先先把vs关闭,然后执行 开始>>所有程序>>Mircosoft visual studio 2008>>visual ...

- List集合与Array数组之间的互相转换

1.数组转换成List集合 采用java中集合自带的asList()方法就可以完成转换了 String[] array = new String[] {"zhu", "w ...

- B - Mike and Fun

Time Limit:2000MS Memory Limit:262144KB 64bit IO Format:%I64d & %I64u Description Mike a ...

- Dockerfile-HEALTHCHECK指令

Dockerfile中使用HEALTHCHECK的形式有两种: 1.HEALTHCHECK [options] CMD command 2.HEALTHCHECK NODE 意思是禁止从父镜像继承的H ...

- PaaS服务之路漫谈(二)

此文已由作者尧飘海授权网易云社区发布. 欢迎访问网易云社区,了解更多网易技术产品运营经验. 天下大势,分久必合,合久必分,社会历史的发展方向总有着惊人的相似.把这种规律应用到软件应用架构的发展方向上, ...

- 机器学习(2):简单线性回归 | 一元回归 | 损失计算 | MSE

前文再续书接上一回,机器学习的主要目的,是根据特征进行预测.预测到的信息,叫标签. 从特征映射出标签的诸多算法中,有一个简单的算法,叫简单线性回归.本文介绍简单线性回归的概念. (1)什么是简单线性回 ...