fpga vga 显示

VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。不支持热插拔,不支持音频传输。

VGA接口

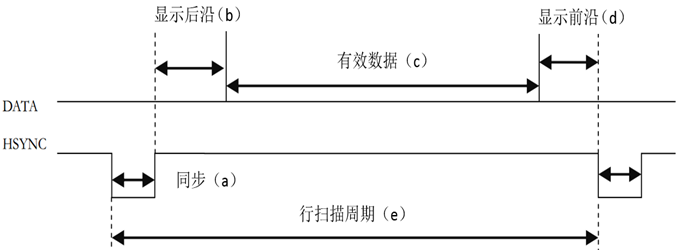

行同步时序

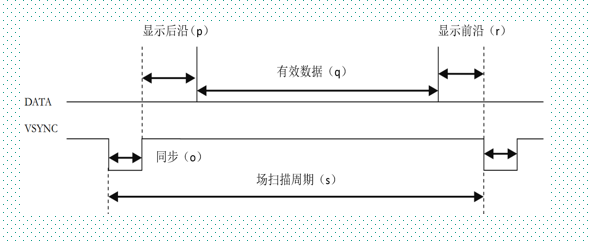

场同步时序

分辨率

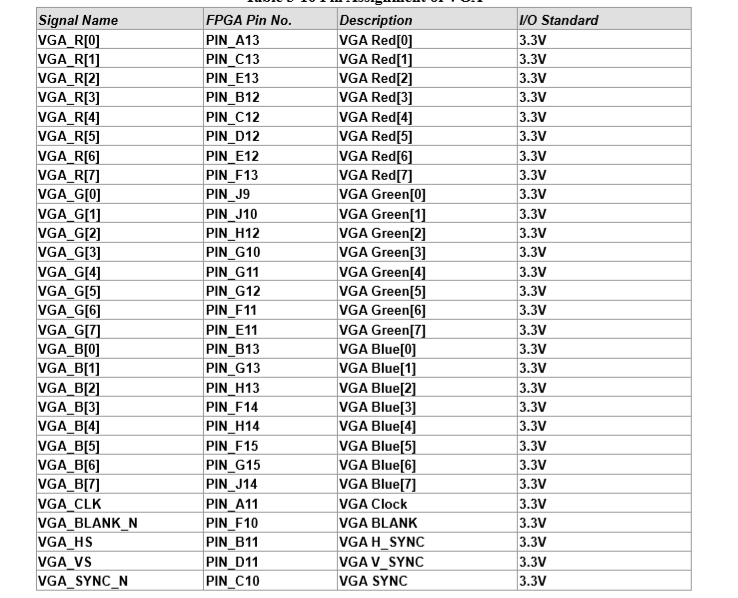

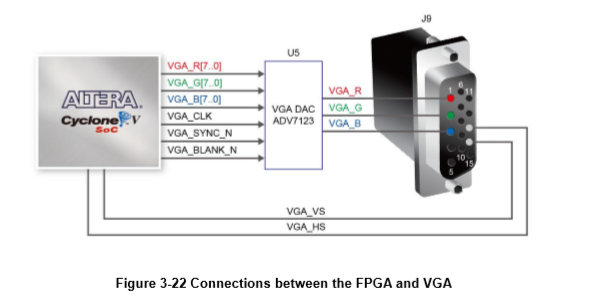

硬件简介

module vga(

output [7:0] VGA_B,

output VGA_BLANK_N,

output VGA_CLK,

output [7:0] VGA_G,

output VGA_HS,

output [7:0] VGA_R,

output VGA_SYNC_N,

output VGA_VS,

input CLOCK_50,

input KEY ); wire[8:0] q;

rom2 rom_inst (

.address( address ),

.clock( CLOCK_50 ),

.rden( ~rdn ),

.q ( q )

); assign VGA_BLANK_N=~rdn;

wire[23:0]datain={q[8:6],5'd0,q[5:3],5'd0,q[2:0],5'd0};

wire[18:0]rd_a;

wire[18:0]address=(rd_a[18:10]*640)+rd_a[9:0];

wire rdn;

wire vga_clk;

assign VGA_CLK=vga_clk;

vga_c u0(

.clk(CLOCK_50),//50MHZ

.clrn(KEY),

.datain(datain),

.h_count(),

.v_count(),

.vga_clk(vga_clk),

.rdn(rdn), //read enable"0"active

.rd_a(rd_a),//read_address={row(9),col(10bit)}

.hs(VGA_HS),

.vs(VGA_VS),

.r(VGA_R),

.g(VGA_G),

.b(VGA_B));

endmodule

`timescale 1ns/1ns

module vga_c(

input clk, // 系统时钟50MHZ

input clrn, //复位信号

input [:]datain, //输入R,G,B数据24bit

output rdn, //读使能信号,低电平有效。

output [:]rd_a, //读地址,read_address={row(9),col(10bit)}

output reg[:]h_count='d0, //列计数器 0-799

output reg[:]v_count='d0, //行计数器 0-524

output reg vga_clk='b0, //vga时钟 25MHZ

//VGA接口信号

output hs, //行扫描信号

output vs, //场扫描信号

output [:]r,g,b //R,G,B输出信号

); //refreshrate=25*10^6/((96+48+640+16)*(480+2+33+10))=59.5=60 //1.VGA时钟生成,vga_clk:25MHZ

always @( negedge clrn or posedge clk )

vga_clk<=(!clrn)?'b0: ~vga_clk; //2.计数器v_count(0-524) and h_count(0-799)

always @( negedge clrn or posedge vga_clk )

if(!clrn) begin v_count<='d0;

h_count<='d0;

end

else if(v_count=='d524)

v_count<='d0;

else

begin

if(h_count=='d799)

begin h_count<='d0;

v_count<=v_count+'b1;

end

else

h_count<=h_count+'b1;

end // 3.锁存输入数据data_in,rdn=0时,外部有存储器有40ns的时间提供datain数据

reg video_out='b0;

reg [:]data_reg='d0; always @(negedge clrn or posedge vga_clk)

if(!clrn)

begin video_out<='b0;

data_reg<='d0;

end

else

begin video_out<=~rdn;

data_reg<=datain;

end //4.接口信号生成

assign hs=(h_count>=); //HS波形输出

assign vs=(v_count>=); //VS波形输出

wire [:]rol=v_count-'d35; //计算行地址

wire [:]col =h_count-'d143; //计算列地址

assign rd_a={rol[:],col[:]}; //行列地址拼接成一个rd_a

assign rdn=~(((h_count>='d143)&&(h_count<10'd783))&&((v_count>='d35)&&(v_count<10'd515))); //只有在有效的数据位rdn才置0

assign r=(video_out)?data_reg[:]:'d0;

assign g=(video_out)?data_reg[:]:'d0;

assign b=(video_out)?data_reg[:]:'d0; endmodule

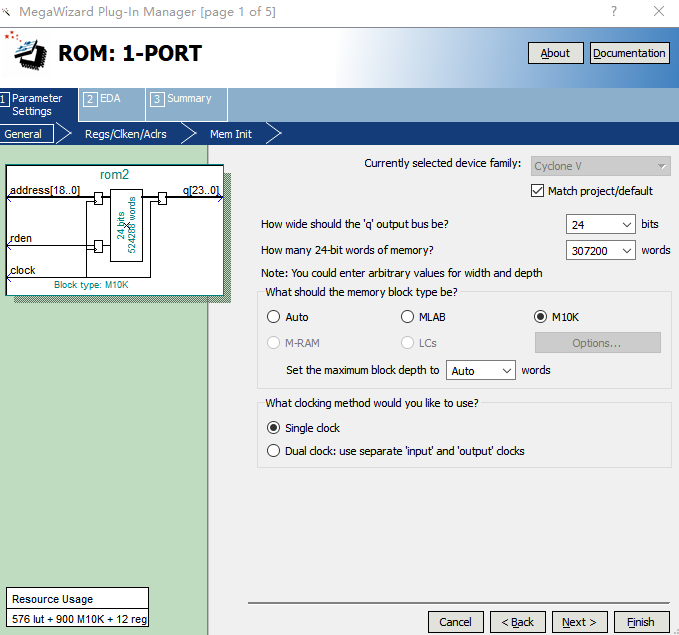

rom ip设置

图片数据mif文件生成:可以使用工具或MATLAB

fpga vga 显示的更多相关文章

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的Uart接收图像数据至VGA显示

系统框图 前面我们设计了基于FPGA的静态图片显示,接下来我们来做做基于FPGA的动态图片显示,本实验内容为:由PC端上位机软件通过串口发送一幅图像数据至FPGA,FPGA内部将图像数据存储,最后扫描 ...

- 纠错:基于FPGA串口发送彩色图片数据至VGA显示

今天这篇文章是要修改之前的一个错误,前面我写过一篇基于FPGA的串口发送图片数据至VGA显示的文章,最后是显示成功了,但是显示的效果图,看起来确实灰度图,当时我默认我使用的MATLAB代码将图片数据转 ...

- FPGA驱动VGA显示静态图片

一 .前言 本文设计思想采用明德扬至简设计法.VGA是最常见的视频显示接口,时序也较为简单.本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采 ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

- 从FPGA搞定OV7670 VGA显示 移植到 STM32F10x TFT显示 总结及疑问(高手请进)

OV7670不愧是最便宜的摄像头了最大显示像素:640*480(在VGA显示器上显示效果还不赖,用usb模块采集显示依然显著) 第一步:VGA显示 视频图像(实时)FPGA+SDRAM+OV7670= ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

随机推荐

- Python 函数 初学者笔记

定义函数 def greet_user(username):#定义一个名为greet_user的函数,username时个形参 print("Hello!" + usernam ...

- java遍历统计一个文件夹中所有文件单词出现次数

思路就是通过递归进行文件遍历,把所有文件夹中的非目录文件都遍历一遍,并判断其中读取到的字符串是不是单词,并对单词进行记录和计数,并在最后进行排序输出,下面是代码: package word; impo ...

- day5 字典 dict

数据类型划分:可变数据类型,不可变数据类型不可变数据类型:元组,数字,布尔,str, == 可哈希可变数据类型:list , dict, set == 不可哈希dict的 key 必须是不可变数据类型 ...

- 关于eclipse 项目导入不了 maven依赖的解决办法

1.首先确定你的项目是maven 项目 ,如果不是:项目右键Configure -->Convert to maven project. 2.在SVN导出的Maven项目,或以前不是用Maven ...

- react-native构建基本页面3---路由配置

安装路由 运行yarn add react-native-router-flux 路由官网 路由相关配置 路由简单的DEMO // Main 才是项目的根组件 import React, { Comp ...

- cmdb实现三种方式

为什么要做CMDB? 1.实现运维自动化,CMDB是实现运维自动化的基石 2.之前做资产统计的时候,使用execl来统计,为了年底资产审计方便 3.运维日常工作繁琐, 4.运行环境不统一 Agent方 ...

- 在IIS中配置申请的SSL证书

第一步,右键服务器证书=>打开功能 第二步,右侧选择导入,将申请到的证书按窗体内容导入即可 第三步,右键需要加载证书的网站,选择编辑绑定=>类型选择https=>选择刚才导入的数字证 ...

- Java后端知识体系及路线【最新秘籍】

第一层(基本语法) 第一层心法,主要都是基本语法,程序设计入门,悟性高者十天半月可成,差一点的 3 到 6 个月也说不准.如果有其他开发语言的功底相助,并且有张无忌的悟性与运气,相信第一层只在片刻 ...

- C语言 删除排序链表中的重复元素

给定一个排序链表,删除所有重复的元素,使得每个元素只出现一次. 示例 1: 输入: 1->1->2输出: 1->2示例 2: 输入: 1->1->2->3-> ...

- JUC之CountDownLatch和CyclicBarrier的区别 (转)

CountDownLatch和CyclicBarrier的功能看起来很相似,不易区分,有一种谜之的神秘.本文将通过通俗的例子并结合代码讲解两者的使用方法和区别. CountDownLatch和Cycl ...