可参数化的带优先级的数据选择器的FPGA实现方式探讨

在FPGA设计中,大部分情况下我们都得使用到数据选择器。并且为了设计参数化,可调,通常情况下我们需要一个参数可调的数据选择器,比如M选1,M是可调的参数。

如果,数据选择器是不带优先级的,我们可以使用 verilog VHDL中的二维数组进行设计 例如,这样综合编译器也是可以正确生成对应的电路。

reg [:] din [:]; assign dout = din[sel];

当我们,需要设计一个参数化的数据选择器时呢?我们该如何设计呢?

一、当然我们可以通过嵌套if来实现,假设我们的多路选择器,在某些情况下最多位M路,那么我们可以嵌套M个if,这样,我们就设计出了参数可调 2~M的多路选择器。

always@(*)begin

if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else if(sel[])//

dout = din[*DATA_SIZE+:DATA_SIZE];

else//

dout = ;

en

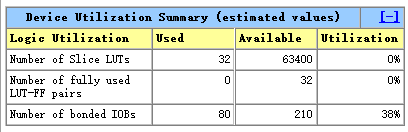

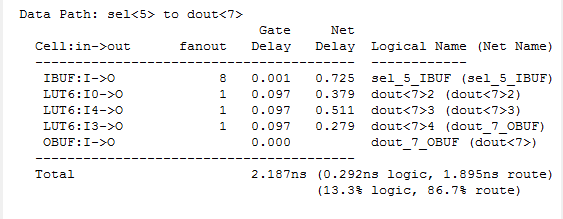

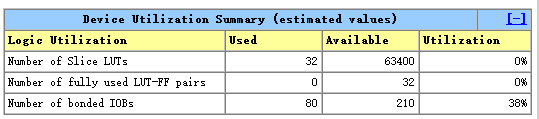

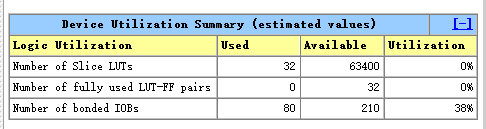

这是对应的资源消耗与Timing,RTL试图

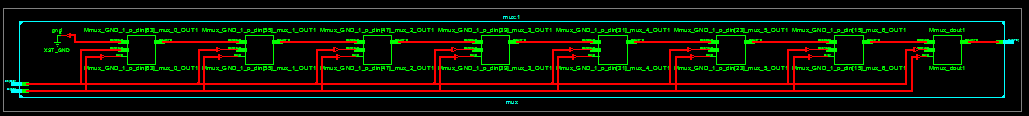

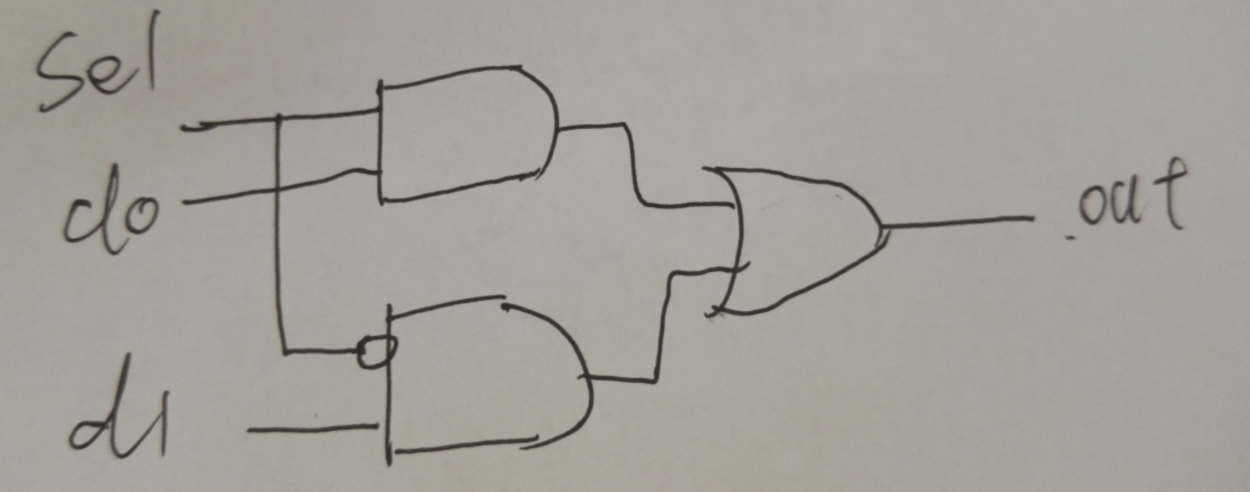

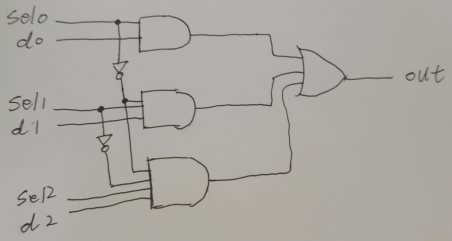

二、当然,我们也知道数据选择器,其实是可以通过与门或门搭建起来的。

比如一个二选一的数据选择器应该,这样一个结构。

一个三选一,带优先级的电路结构

也就是说,我们可以通过代码,描述出这样一个电路结构,通过逻辑复制的语句完成参数化的设计。

具体思路是这样的,先把地址信号sel 变成只是优先级高的那位为1,其他信号为0。例如,低位高优先级,sel=1100,变换后sel_prio=0100。然后,将sel_prio与上对应的数据,可以看出来只有1的那个数据才会被选通,其他为0。代码如下,可以看出来代码里用了很多function,很多书都说function综合成电路可能有问题,我的理解是,如果你对电路由足够的理解,并且综合后都去看一下综合器是否综合出你想要的电路。使用function是可以简化代码的。

module mux

#(

parameter DATA_SIZE = ,

parameter NUM =

)

(

input [NUM*DATA_SIZE-:] din,

input [NUM-:] sel, output [DATA_SIZE-:] dout ); assign dout = mux_prio(din,sel); function [DATA_SIZE-:] mux_prio ; input [NUM*DATA_SIZE-:] din;

input [NUM-:] sel; reg [NUM-:] dat;

integer i,j;

begin

for(i=;i<DATA_SIZE;i=i+)begin

for(j=;j<NUM;j=j+)begin

dat[j] = din[j*DATA_SIZE+i];

end

mux_prio[i] = mux_prio_bit(dat,sel_prio(sel));

end

end

endfunction function [NUM-:] sel_prio ;

input [NUM-:] sel;

reg temp;

integer i,j;

begin

sel_prio[] = sel[];

for(i=;i<NUM;i=i+)

begin

temp = ;

for(j=;j<i;j=j+)

begin

temp = temp | sel[j];

end

sel_prio[i] = sel[i] && !temp;

end

end

endfunction function mux_prio_bit ; input [NUM-:] din;

input [NUM-:] sel;

integer i;

begin

mux_prio_bit = din[]&&sel[];

for(i=;i<NUM;i=i+)

mux_prio_bit = mux_prio_bit | (din[i]&sel[i]);

end

endfunction endmodule

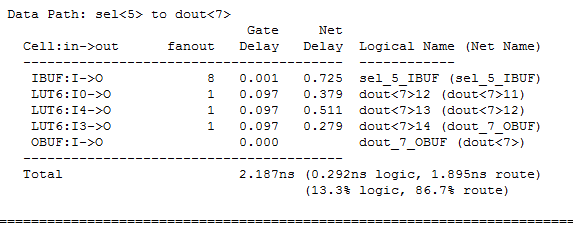

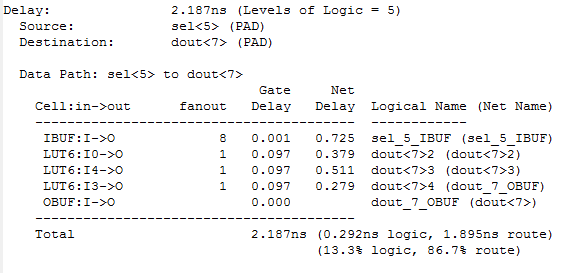

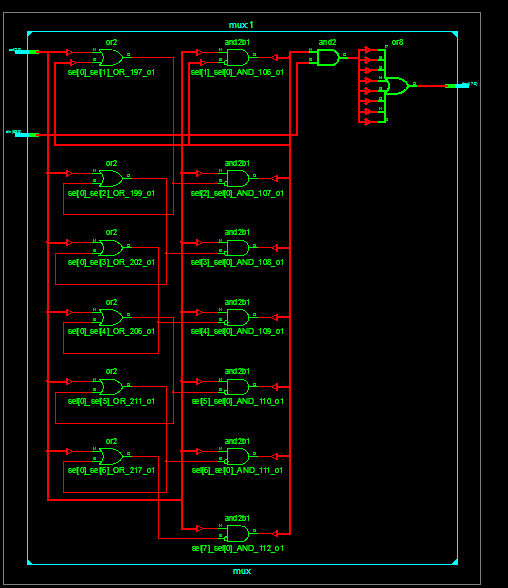

同样的,我们观察一下,生成的电路与综合报告

可以看出来,在这样的综合设置下,生成出来的电路就是我们需要的电路,并且和我们所想的是一样的。并且看起来就是一的电路。

三、在前面的设计中我们是根据数据选择器的电路结构,用硬件语言描述出了这样的电路,那么我们能不能只描述其功能,然后让编译器帮我们理解呢?

贴代码

module mux

#(

parameter DATA_SIZE = ,

parameter NUM =

)

(

input [NUM*DATA_SIZE-:] din,

input [NUM-:] sel, output [DATA_SIZE-:] dout ); assign dout = mux_prio_a(din,sel);

//基于功能,行为级的描述

function [DATA_SIZE-:] mux_prio_a ;

input [NUM*DATA_SIZE-:] din;

input [NUM-:] sel;

reg temp;

integer i;

begin

temp = ;

mux_prio_a = ;

for(i=;i<NUM;i=i+)begin

if(temp && sel[i])begin

temp = ;

mux_prio_a = din[i*DATA_SIZE+:DATA_SIZE];

end

end

end

endfunction endmodule

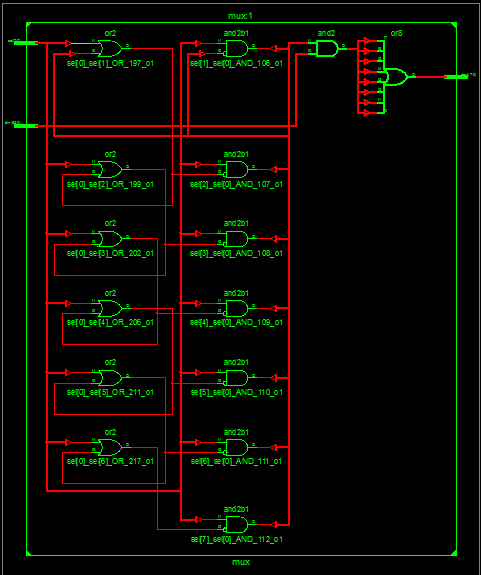

看综合结果:可以看出来这样的代码,编译器也是可以正确理解这样的设计的。综合出了我们所需要的电路。

总结:

1、首先,这里提供了了三种描述参数可配的带优先级的多路选择器的描述方法。第一种是常规的描述方法,第二种是根据电路结构使用HDL描述,第三种是使用代码描述了其功能。

2、第三种方法从功能描述,看起来描述简单,好理解,不过这样的描述方式是看综合软件的“智能化程度”的,因为FPGA是基于查找表LUT结构的,这样的描述方式在描述比较简单的电路功能,综合器是可以正确理解的。如果比较复杂的电路,不推荐用这样的描述方式。

3、值得注意的是,FPGA设计最重要的是理解低层的电路结构,实现过程最好是 功能--》电路--》HDL描述该电路,这才是最好的设计。使用类似第三种描述方式最好还是掌握理解底层电路结构,然后看综合出来的是不是你需要的电路。

可参数化的带优先级的数据选择器的FPGA实现方式探讨的更多相关文章

- FPGA中带优先级的if else if与不带优先级的case的探讨

我们知道在书本上都说让我们尽量使用不带优先级的的数据选择器,今天我们就来探讨一下二者的区别. 例子1:带优先级的的数据选择器,综合成功,且没有任何警告. module detection_prio # ...

- C#+HtmlAgilityPack+XPath带你采集数据(以采集天气数据为例子)

第一次接触HtmlAgilityPack是在5年前,一些意外,让我从技术部门临时调到销售部门,负责建立一些流程和寻找潜在客户,最后在阿里巴巴找到了很多客户信息,非常全面,刚开始是手动复制到Excel, ...

- jmeter随笔(3)-从csv中获取带引号的数据详情

最近在工作中,对jmeter实践的点滴的记录这里分享,不一定正确,仅供参考和讨论,有想法的欢迎留言.谈论. 1技巧1:从csv中获取带引号的数据详情 背景:我们从csv中获取数据,在jmeter中使用 ...

- echo json数据给ajax后, 需要加上exit,防止往下执行,带上其他数据,到时ajax失败

01返回json数据给ajax后需要加上exit.返回json数据前不能有其他输出 function apply(){ if(IS_POST){$info['status'] = 1; echo js ...

- jmeter csv中获取带引号的数据详情

最近在工作中,对jmeter实践的点滴的记录这里分享,不一定正确,仅供参考和讨论,有想法的欢迎留言.谈论. 1技巧1:从csv中获取带引号的数据详情 背景:我们从csv中获取数据,在jmeter中使用 ...

- jmeter csv中获取带引号的数据详情(转)

最近在工作中,对jmeter实践的点滴的记录这里分享,不一定正确,仅供参考和讨论,有想法的欢迎留言.谈论. 1技巧1:从csv中获取带引号的数据详情 背景:我们从csv中获取数据,在jmeter中使用 ...

- 模块:(日期选择)jquery、bootstrap实现日期下拉选择+bootstrap jquery UI自带动画的日期选择器

一:jquery.bootstrap实现日期下拉选择 点击文本框弹出窗口 弹窗显示日期时间选择下拉 年份取当前年份的前后各5年 天数随年份和月份的变化而变化 点击保存,文本框中显示选中的日期 代码部分 ...

- 有关css的选择器优先级以及父子选择器

css,又称样式重叠表,如今的网页的样式基本是div+css写出来的,功能十分强大,要想在html文件中引入css文件需要在<head></head>标签内输入一行:<l ...

- golang中通过bufio和os包读取终端中输入的一行带空格的数据

1. 如果读取不带空格的数据可以使用fmt.Scan或fmt.Scanln读取一个或多个值,但是不能读取带空格的数据,可以使用bufio和os两个包结合 package main import ( & ...

随机推荐

- 转载:IIS 之 连接数、并发连接数、最大并发工作线程数、队列长度、最大工作进程数

一.IIS连接数 一般购买过虚拟主机的朋友都熟悉购买时,会限制IIS连接数,顾名思义即为IIS服务器可以同时容纳客户请求的最高连接数,准确的说应该叫“IIS限制连接数”. 客户请求的连接内容包括: [ ...

- java_29打印流

1打印流 PrintStream 和PrintWriter 不负责数据源 只负责数据目的 2.方法 public class Demo { public static void main(St ...

- win10操作系统上,wireshark抓取https。

今天试了下使用wireshark抓https的包 一.记录如下: 配置一个环境变量SSLKEYLOGFILE为D:\Temp\sslog.log(这个文件需要自己去创建). 去下载一个chrome浏览 ...

- mysql中文查询问题

alter table t_foo change `str` `str` varchar(100) character set utf8 not null ;

- kubernetes + istio进行流量管理

实验目的: 本文介绍如何通过istio实现域名访问k8s部署的nginx服务 前提: 已经安装了kubernetes的服务器 了解 kubernetes 基本命令如何使用 (kubectl creat ...

- ldd源码编译出现的问题

1.Fix it to use EXTRA_CFLAGS. Stop 1). # make KBUILD_NOPEDANTIC=12). Relace all CFLAGS with EXTRA_C ...

- Java在ServletContextListener、过滤器、拦截器解决对象无法注入问题

1.通用方法: // 数据库日志操作对象 private LogInfoServiceIFC logInfoServiceProxy; @Override public void contextIni ...

- centos7 防火墙相关命令

启动:systemctl start firewalld禁用:systemctl stop firewalld重新载入规则:firewall-cmd --reload查看所有打开的端口:firewal ...

- Concept Drift(概念漂移)

Introdution concept drift在机器学习.时间序列以及模式识别领域的一种现象.如果是在机器学习领域中,这个概念指的就是一个模型要去预测的一个目标变量,概念漂移就是这个目标变量随着时 ...

- 现网环境业务不影响,但是tomcat启动一直有error日志,ERROR org.apache.catalina.startup.ContextConfig- Unable to process Jar entry [module-info.class] from Jar [jar:file:/home/iufs/apache-tomcat/webapps/iufs/WEB-INF/lib/asm

完整的错误日志信息: 2019-03-19 15:30:42,021 [main] INFO org.apache.catalina.core.StandardEngine- Starting Ser ...