FPGA中的时序分析(三)

验证公式正确性

前两篇博客提及了关于时序的建立余量和保持余量的计算。结合实际情况,验证公式的运算正确性。结合之前博客提及的LED实验,看一下建立余量和保持余量是否都合格。

建立余量

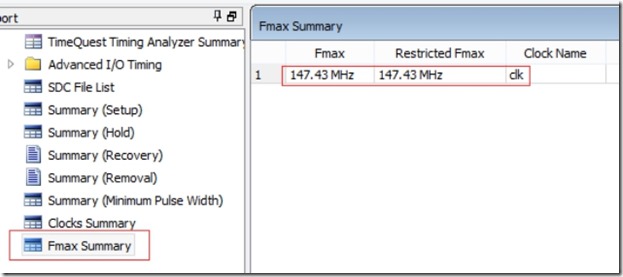

图1是最大时钟频率,可以看到完全满足时钟频率要求,高于主时钟运行频率。

图1 最大时钟频率

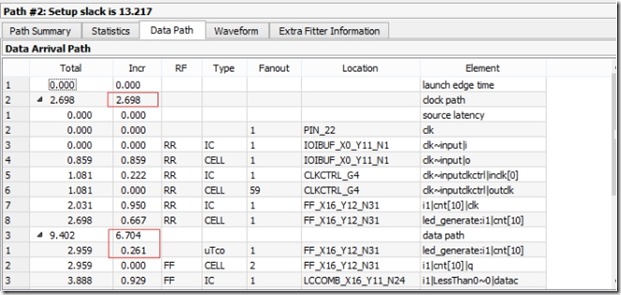

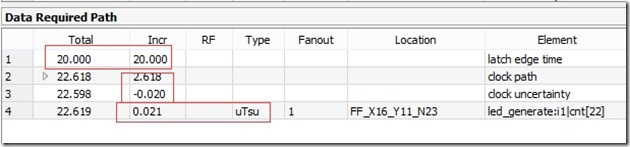

图2所示建立余量的是时序图,首先看到建立余量是13.217,大于0,完全满足数据信号和时钟信号之间的建立时间关系。其中上升沿时间(launch edge time)为0ns,源时钟达到寄存器(Tclk1)的时间为2.698ns,Tco = 0.261ns,Tdata = (6.704 - 0.261) ns,所以数据到达时间 T_A_T = 0 + 2.698 + 0.261 + (6.704 - 0.261) =9.402ns ;对于数据要求时间 T_R_T = 20 +(2.618-0.020) - (-0.021) = 22.619ns,其中数据要求时间各参数可以参看图3所示,所以建立余量 = T_R_T - T_A_T = 13.217ns.

图 2 数据到达时间

图3 数据要求时间

保持余量

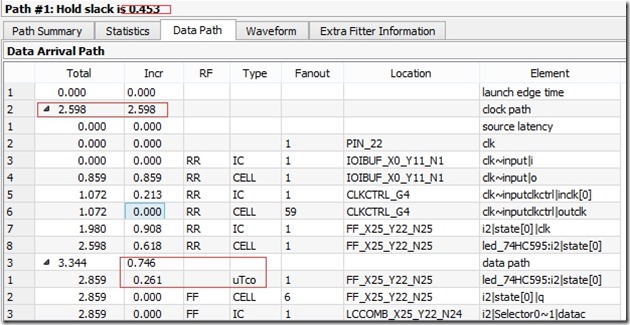

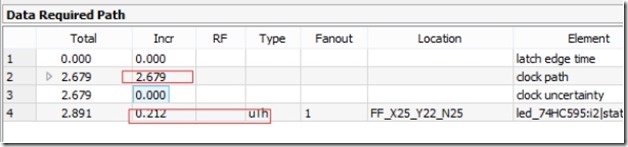

如图4所示,是保持余量相关的数据,可以看到保持余量是0.453,也是正值满足时序要求。从图中可以看到,其中上升沿时间(launch edge time)为0ns,源时钟达到寄存器(Tclk1)的时间为2.598ns,Tco = 0.261ns,Tdata = (0.746 - 0.261) ns,所以数据到达时间 T_A_T = 0 + 2.598 + 0.261 + (0.746 - 0.261) = 3.344ns;对于数据要求时间 T_R_T = 0+ 2.679+0.212 = 2.891ns,其中数据要求时间各参数可以参看图5所示,所以保持余量 = T_A_T - T_R_T = 0.453ns.

图4 数据到达时间

图5 数据要求时间

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================

FPGA中的时序分析(三)的更多相关文章

- FPGA中的时序分析(一)

谈及此部分,多多少少有一定的难度,笔者写下这篇文章,差不多是在学习FPGA一年之后的成果,尽管当时也是看过类似的文章,但是都没有引起笔者注意,笔者现在再对此知识进行梳理,也发现了有很多不少的收获.笔者 ...

- FPGA中的时序分析(四)

常用约束语句说明 关于Fmax 上述是实现Fmax的计算公式,clock skew delay的计算如下图, 就是两个时钟的差值.到头来,影响Fmax的值的大小就是组合逻辑,而Fmax是针对 ...

- FPGA中的时序分析(五)

时序约束实例详解 本篇博客结合之前的内容,然后实打实的做一个约束实例,通过本实例读者应该会实用timequest去分析相关的实例.本实例以VGA实验为基础,介绍如何去做时序约束. 首先VGA这种情况属 ...

- FPGA中的时序分析(二)

使用Timequest 笔者对Altera较熟悉,这里以quartus ii中的timequest作为讲解. Timequest分析时序的核心,也就是在于延迟因数的计算.那么建立约束文件,去告诉tim ...

- fpga中的存储器

fpga中的存储器三种:RAM,ROM,FIFO. RAM和ROM已经比较熟悉了,记录一下FIFO. FIFO:first in first out ,顺序存取,先入先出.是一种数据缓存器,用来作不同 ...

- 【转】关于FPGA中建立时间和保持时间的探讨

时钟是整个电路最重要.最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错:因而明确FPGA设计中决定系统时钟的因素,尽 ...

- 【转载】FPGA 中的latch 锁存器

以下这篇文章讲述了锁存器的一些概念和注意事项.原文标题及链接: FPGA 中的latch 锁存器 - 快乐至永远上的博客 - 与非博客 - 与网 http://www.eefocus.com/liuy ...

- FPGA中的INOUT接口和高阻态

除了输入输出端口,FPGA中还有另一种端口叫做inout端口.如果需要进行全双工通信,是需要两条信道的,也就是说需要使用两个FPGA管脚和外部器件连接.但是,有时候半双工通信就能满足我们的要求,理论上 ...

- FPGA中的除法运算及初识AXI总线

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会.硬件逻辑实现的除法运算会占用较多的资源,电路结构复杂,且通常无法在一个时钟周期内完成.因此FPGA实现除法运算并不是一个&qu ...

随机推荐

- 【Unity】10.2 通用动画的导入和设置

分类:Unity.C#.VS2015 创建日期:2016-05-02 一.简介 使用类人动画时,Mecanim 的强大之处最明显.但是,尽管没有 Avatar 系统和其他功能,非类人动画也仍然受Mec ...

- Webservice超时问题

Winform客户端调用Webservice 120秒超时.对此问题,针对服务器与客户端分别作了超时设置为300S. 1. 服务器端设置超时 在 web.config 的 system.web 里添加 ...

- Fluent UDF【5】:第一个UDF

这里以一个简单的初始化案例来描述UDF的使用过程. 0 Fluent中的Patch Fluent中提供了全域初始化以及局部Patch功能.对于整体区域的全局初始化可以采用starndard及hybri ...

- C++11 explicit的使用

C++中的explicit关键字只能用于修饰只有一个参数的类构造函数 , 它的作用是表明该构造函数是显示的, 而非隐式的,跟它相对应的另一个关键字是implicit, 意思是隐藏的,类构造函数默认情况 ...

- 每日英语:China to Move Slowly on One-Child Law Reform

BEIJING—China's family-planning agency is projecting a slow rollout for an easing of its one-child p ...

- hive入门

hive 当前用到的就这些,以后用到的再补充. 参考自官方文档 大小写不敏感 创建/删除数据库 CREATE/DROP DATABASE|SCHEMA [IF NOT EXISTS] <data ...

- django 中多字段主键(复合、联合主键)

django中不支持双主键.多主键. 要实现类似功能可以: classMeta: unique_together=(("driver","restaurant" ...

- java 多线程 30: 多线程组件之 CyclicBarrier

CyclicBarrier 接着讲多线程下的其他组件,第一个要讲的就是CyclicBarrier.CyclicBarrier从字面理解是指循环屏障,它可以协同多个线程,让多个线程在这个屏障前等待,直到 ...

- MyBatisBatchItemWriter Cannot change the ExecutorType when there is an existing transaction

但凡使用mybatis,同时与spring集成使用时,接下来要说的这个问题是躲不了的.众所周知,mybatis的SqlSessionFactory在获取一个SqlSession时使用默认Executo ...

- 园子里的一个Dal类

public class DALHelper { public static List<T> Search<T>() where T : SH_SetBase { using ...