AMBA总线介绍-01

AMBA总线介绍

- AMBA总线概述

- AHB

- APB

- 不同IP之间的互连

1.系统总线简介

- 系统芯片中各个模块之间需要有接口连接,使用总线作为子系统之间共享的通信链路

- 优点:成本低,方便易用(通用协议,不用协议之间的转换模块)

- 缺点:容易造成性能瓶颈(Bus上挂载很多模块,会有冲突,需要仲裁,造成性能瓶颈)

1.1 AMBA2.0

总线是有协议的,也有版本

- Advanced Microcontroller Bus Architecture

- AHB(Advanced High-performance Bus)

- ASB(Advanced System Bus)

- APB(Advanced Peripheral Bus)

1.2 总线发展历史

- AMBA 1.0

ASB和APB - AMBA 2.0

AHB\ASB\APB - AMBA 3.0

AMBA Advanced extensible interface(AXI) - AMBA 4.0

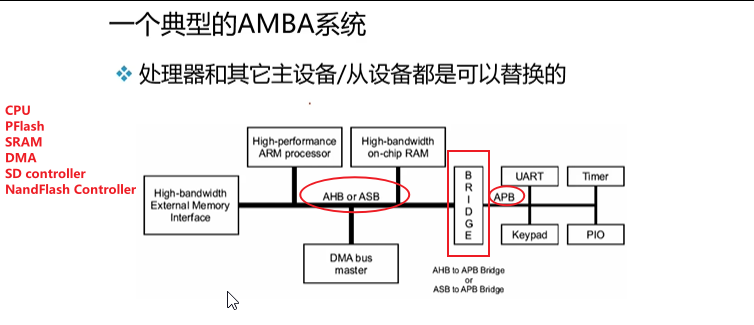

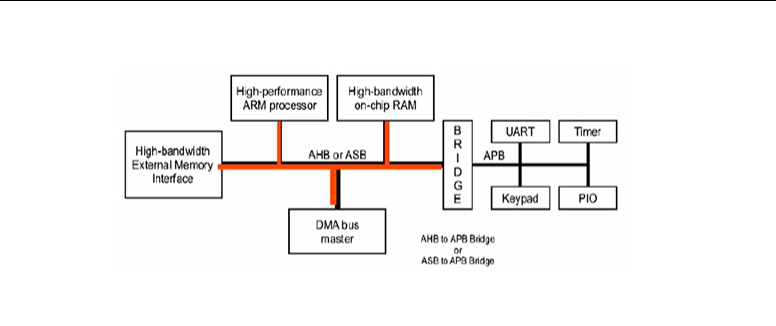

1.3 典型的AMBA系统

- 对于AHB总线上,Master(主设备)可以有多个,Slave(从设备)也可以有多个。

- 对于APB总线上,Master只有Bridge,主设备(Bridge)会将AHB的请求转换为APB的请求

- Master(主设备):可以主动的发起读写请求

- Slave(从设备):不能主动发起一些请求,但是可以接受主设备的发来的请求,并给予一些响应。

1.4 AHB特点

- 高速总线

- 2级流水线操作

- 支持多个总线主设备(最多16个)

- 支持burst传输

- 总线带宽:8、16、32、64、128bits(根据不同的功能可以进行自定义)

- 上升沿触发操作

- 对于一个新设计建议使用AHB

1.5 ASB特点

- 高速总线

- 流水线操作

- 支持多个总线主设备

- 支持burst传输

- 总线带宽:8、16、32bits

- 三态、双向总线(不适用于DFT)

- 下降沿或者上升沿触发

1.6 APB特点

- 低速总线、低功耗

- 接口简单(外设UART\I2C\SPI,本身的逻辑就会很简单)

- 在Bridge中锁存地址信号和控制信号(APB中的唯一主设备,可以锁存总线的读写请求)

- 适用于多种外设

- 上升沿触发

2.AHB组成部分

AHB主设备(master)

可以作为请求发起端访问从设备

初始化一次读或写操作

某一时刻只允许一个主设备使用总线

CPU\DMA\DSP\LCDCAHB从设备(slave)

响应一次读写操作

通过地址映射来选择使用哪一个从设备

Bridge从AHB端是从设备,在APB端是主设备

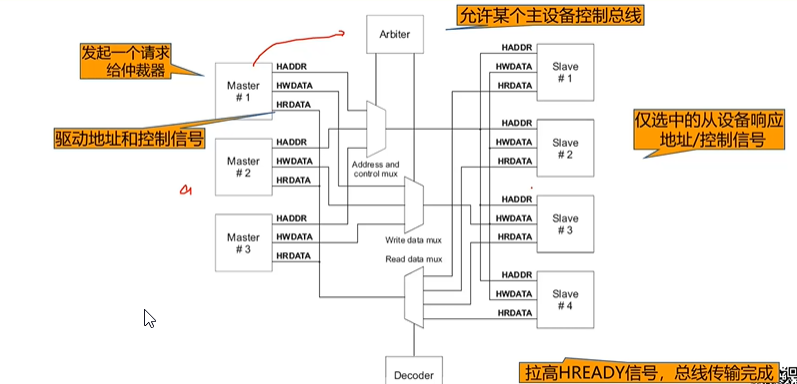

存储器的控制器(响应读写请求)AHB仲裁器(arbiter)

允许某一个主设备控制总线

在AMBA协议中没有定义仲裁算法AHB译码器(decoder)

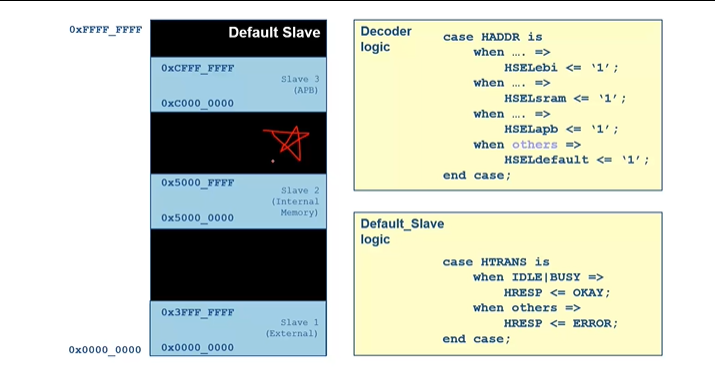

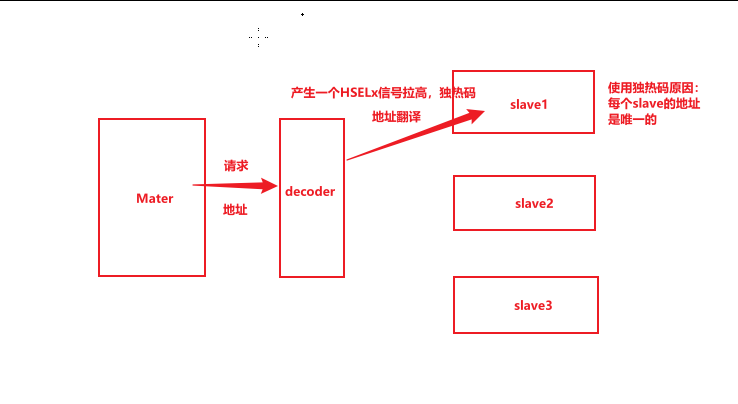

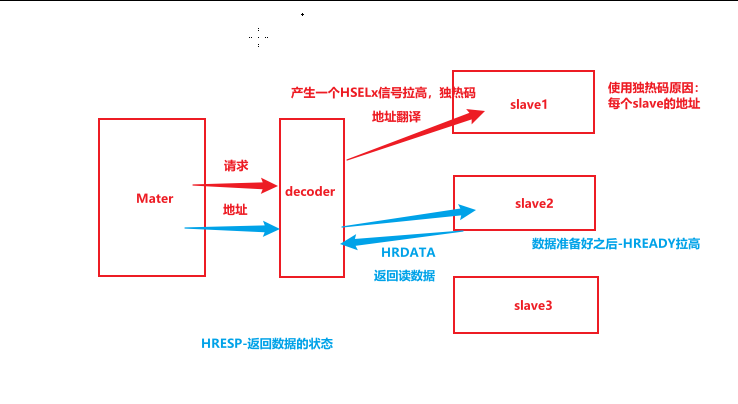

通过地址译码来决定选择哪一个从设备

3.APB组成

- AHB2APB Bridge

可以锁存所有的地址、数据和信号

进行二级译码来产生APB从设备选择信号

AHB2APB Bridge是AHB上的一个slave,有很大的地址空间,通过二级译码,选择APB上挂载的模块信号 - APB总线上所有的其他模块都是APB从设备(slave)

4.AMBA协议有关问题

- 与工艺无关

- 没有定义电气特性

- 仅在时钟周期级定义时序

提取时序参数依赖于所采用的工艺和工作频率

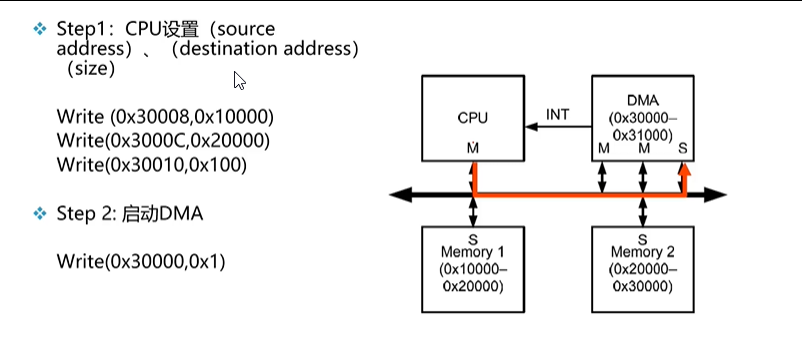

5.DMA实例

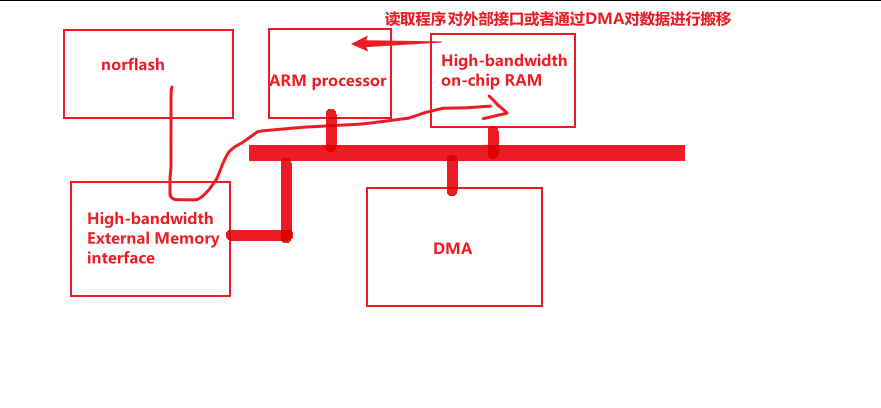

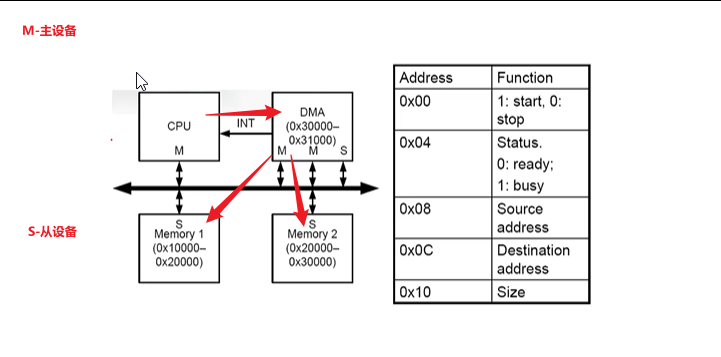

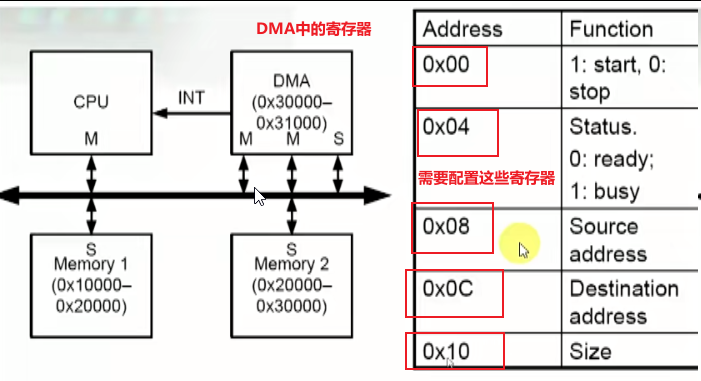

DMA既是主设备又是从设备,DMA本身是不知道自己做什么的,CPU通过DMA的slave端口,对DMA的寄存器进行配置,然后激活DMA,DMA此时就可以控制总线(DMA控制总线的优先级高于CPU)。CPU需要对DMA的slave接口进行配置,DMA接受(源地址,目标地址,数据长度)等信息,之后进行操作存储器进行数据传输

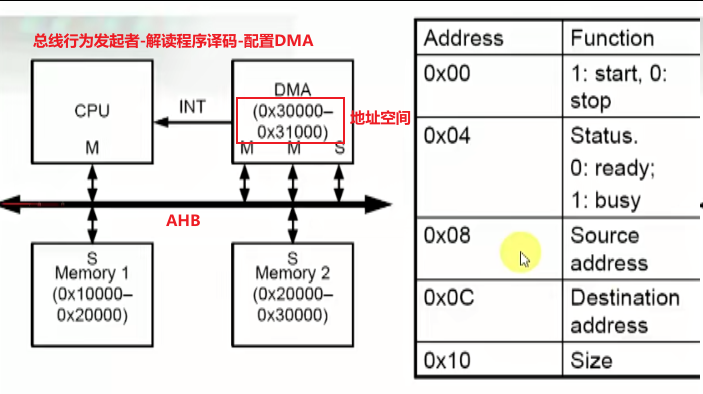

- CPU是所有总线行为的源头或发起者,真正的源头是程序,比如C code编译为二进制码,通过各种方式存储到SRAM中,CPU可以从SRAM中读出程序译码,解读程序,去配置每个模块,比如DMA。

- CPU如要选择配置DMA模块,会发送地址,这个地址在DMA的地址空间内就表明选择了DMA,如果不在就表示没有选择DMA;如果CPU在发送地址的时候,选择了没有配置任何模块的地址空间,那么就表示CPU选择了一个默认的slave,不会对Bus产生任何影响

- CPU发送一个地址,AHB中的decoder模块,通过地址译码之后产生Hsel信号,选择模块

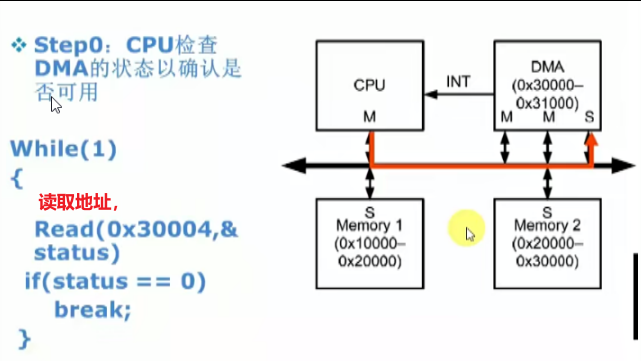

5.1 DMA工作过程

C code执行过程

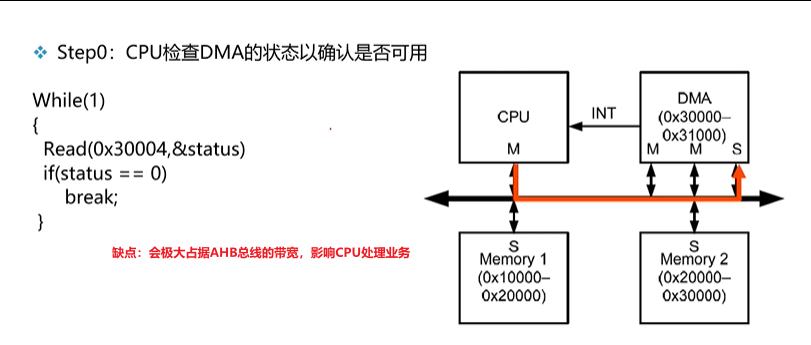

启动DMA操作,首先,CPU需要检查DMA状态是否可以用,C代码中read(0x3004...),存储到SRAM中,CPU读到这段代码之后,CPU就会去触发读取请求,AHB通过HRDATA读取到slave的状态

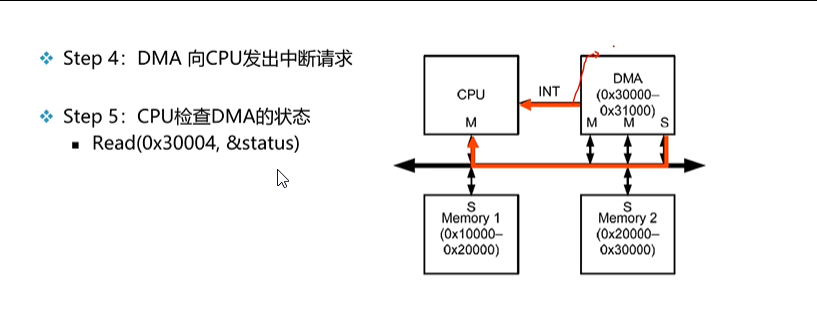

CPU向AHB总线发起一个读请求,查看DMA的状态。通常DMA在处理完数据之后,会发送一个中断给CPU,CPU接收到中断之后会进行中断处理,重新发起一个任务。

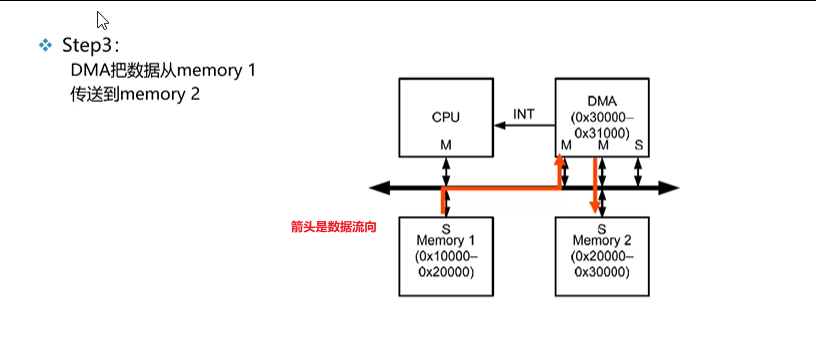

DMA可以快速的从源地址到目标地址进行数据搬运,因为CPU的功能由很多,不仅仅能够处理搬运数据的指令,所以CPU在进行处理其他任务的时候,就不能进行搬运数据,效率没有DMA搬运数据高

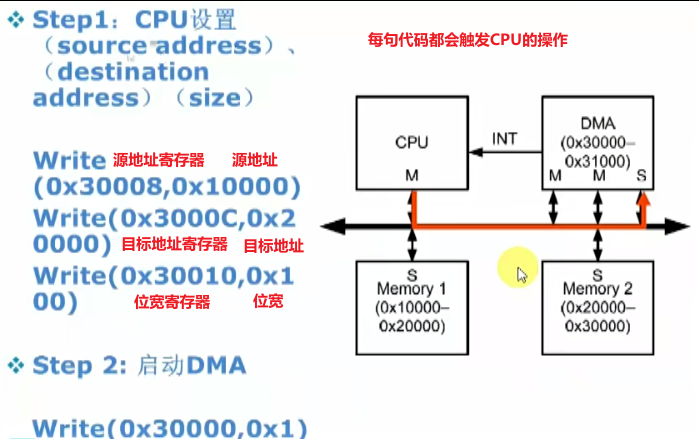

- CPU在发现DMA状态可用的时候,会将DMA的描述符配置到DMA中,起始地址,结束地址,数据位宽;然后启动DMA

- mem1将数据传递mem2,DMA先从mem1读取数据,通过burst传输,批量的读取数据和传输数据。如果通过CPU进行传输数据,效率比较低,因为CPU执行顺序不是连续的,中间会有IDLE状态。DMA传输数据比较快是因为DMA中有内置的FF。

- DMA完成数据执行之后,DMA向CPU发出中断,表示DMA传输数据完成;CPU再次检查DMA的状态

6.AHB总线

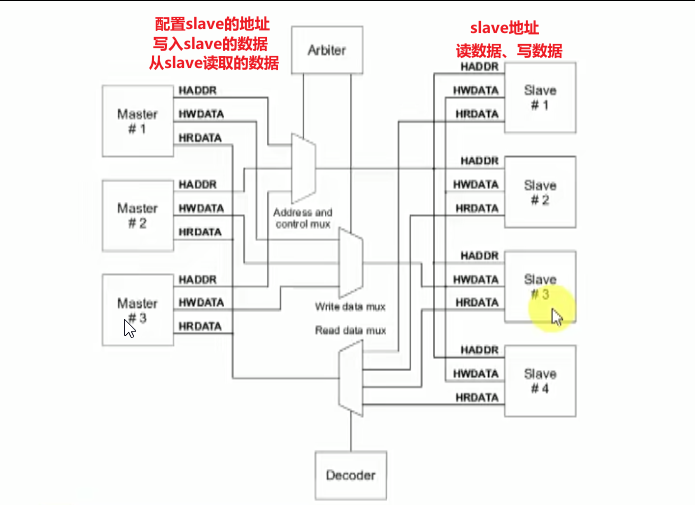

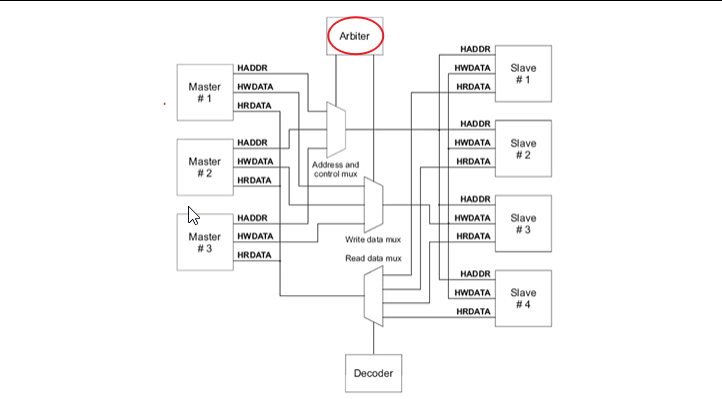

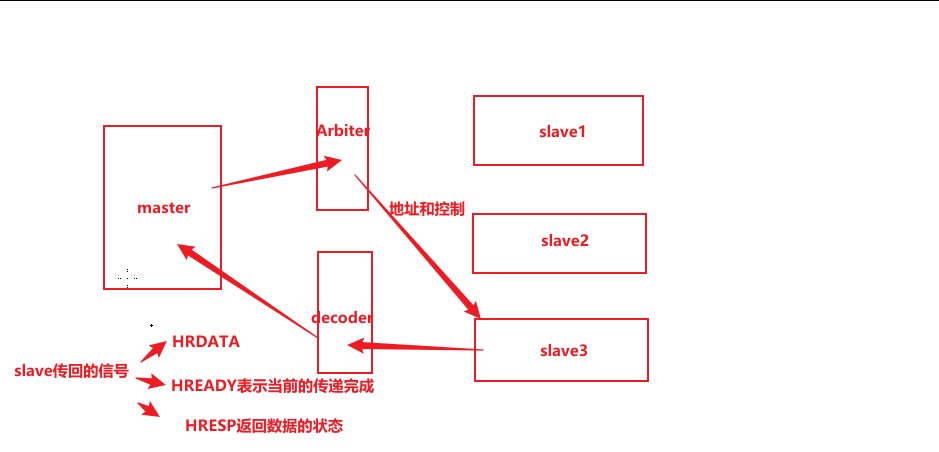

6.1 AHB总线互连

- AHB上会有很多Master,会发送HADDR,HWDATA,HRDATA

主设备可以发起请求,主要发送的是地址,数据和控制信号。每个Master都会发送给Arbiter,Arbiter决定哪个Master控制总线,比如Arbiter选择Master2,address control mux就会将Master2选通,通过HSEL信号选择slave,将信息传递给从设备,slave进行返回数据,decoder会选择哪个slave返回数据。

Arbiter控制Write data mux,比如要选择Maste2的HWDATA,通过HSEL信号选择slave,slave被激活之后会返回数据

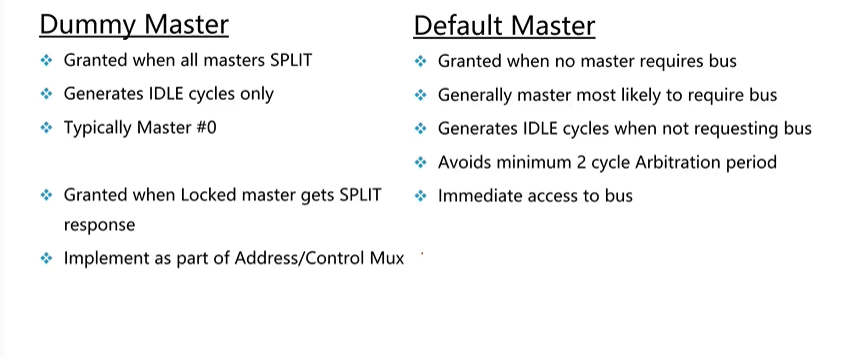

6.2 Dummy/Default Master

- 如果没有Master发送请求,Arbiter会将总线控制权给Dummy Master,只会产生一种请求IDLE,表示当前Arbiter空闲,没有发起任何读写操作。(Dummy Master不是一个实体,相当于一个虚拟的Dummy Master,隐藏在Arbiter或者是decoder中)。

- Default Master会将系统中的一个Master(使用频率最多的)作为一个Default Master,如果总线上没有任何一个Master进行请求的时候,Arbiter会将总线控制权给Default Master。

- 如果使用Dummy Master,在申请总线的过程中也需要耗费时钟周期,仲裁过程一般耗费两个时钟周期,使用Default Master就会节省两个时钟周期。

6.3 Default slave

假设一个32位(4G)的地址空间,每一个slave地址占据地址空间中的一部分,如果CPU访问的地址是没有定义的地址,就认为是访问的是default slave,根据传输模式,返回响应。写入到这些地址的数据,都会被丢掉,不会对系统产生影响。

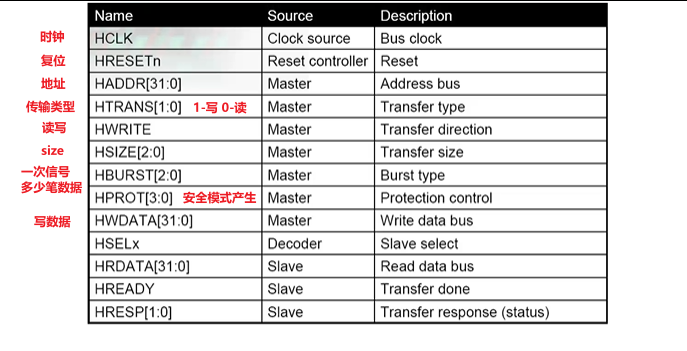

6.4 AHB信号

总线包含的是一组信号,有总线的请求端、控制端、地址端、数据端信号。所有遵循AMBA2.0协议的AHB总线的IP都要实现这些信号。

- 同步上升沿触发的BUS,HCLK,HRESTn时钟复位信号

- HRESTn表示低电平有效复位信号,n表示低电平有效

- HADDR[31:0]-表示32位的地址总线Bus,AHB可以支持64 128位的总线Bus

- HWDATA[31:0]写数据总线,从主设备写到从设备

- HRDATA[31:0]读数据总线,从从设备读到主设备

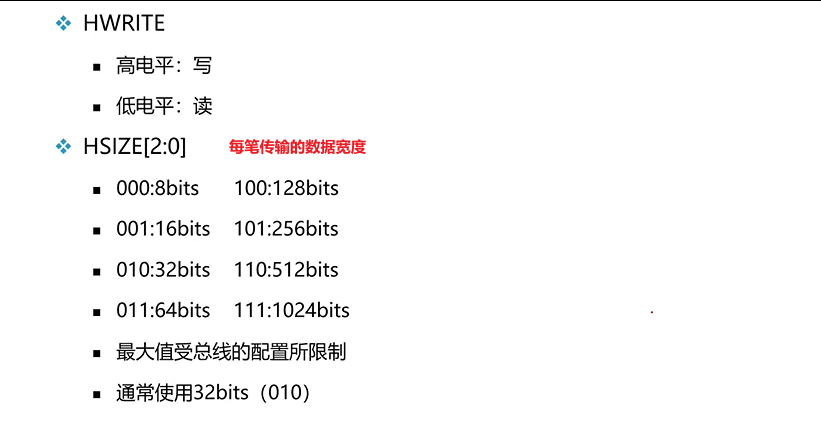

- HWRITE拉高表示写请求,HWRITE拉低表示读请求

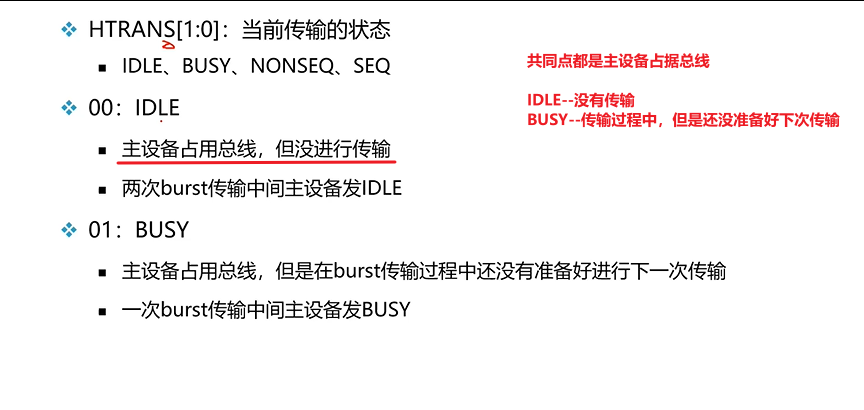

- HTRANS表示当前传输的状态

- HWRITE信号拉高之后,需要把HWDATA驱动

- HRESP从设备发给主设备的总线传输状态(OKAY,ERROR,RETRY,SPLIT)

- HREADY-高电平表示从设备指出传输结束,低电平表示从设备需要延长传输周期(有些设备传输比较慢)

- 上图中的decoder(应该换为Arbiter和decoder,入下图所示),从Master发出经过Arbiter仲裁,选择Master,传输地址和控制信号,HREADY信号拉高表示传输完成

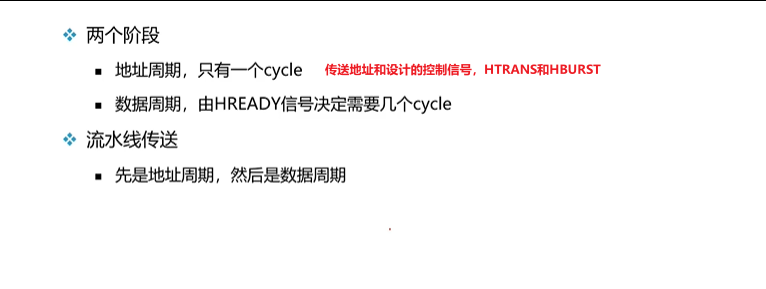

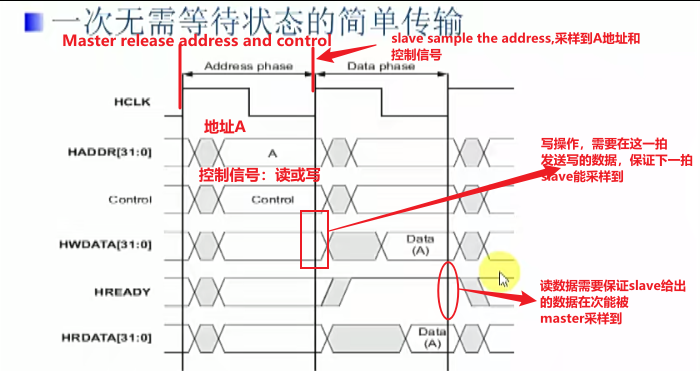

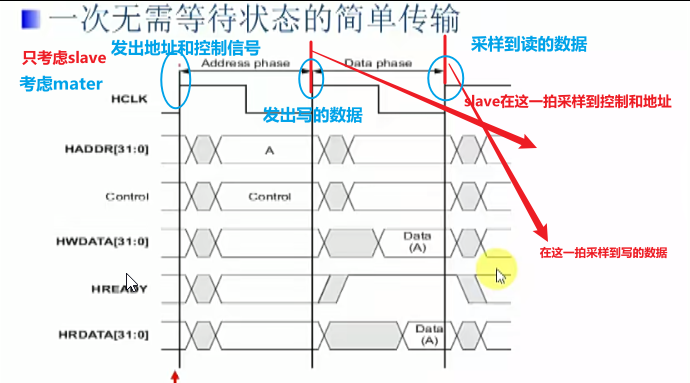

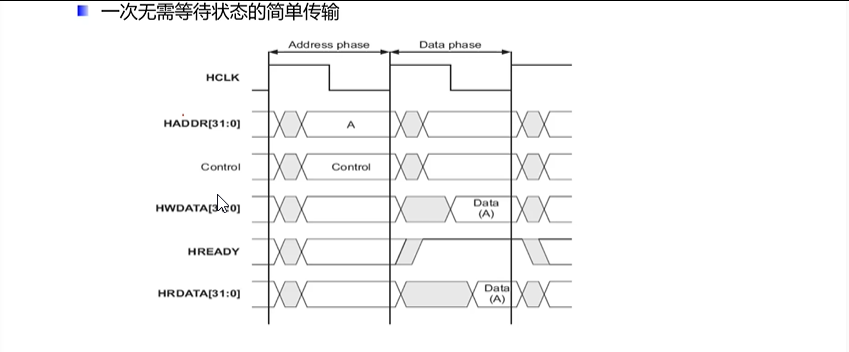

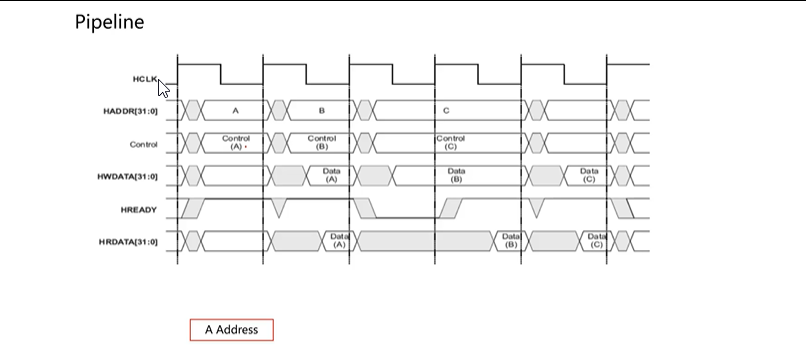

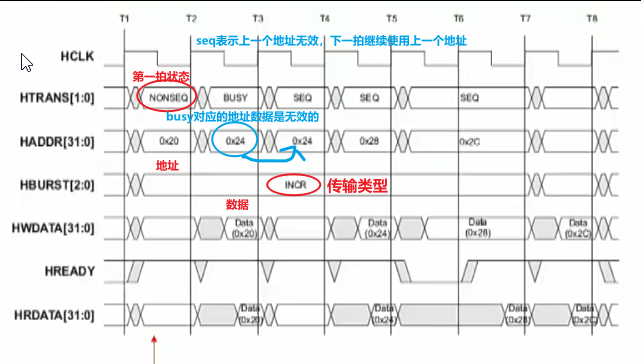

6.5 AHB时序

拿到任何一个协议,要了解协议中包含的所有信号和信号的时序关系

Address phaze第一个周期上升沿Master会把地址和控制信号(地址数据)驱动到总线上(HTRANS,HSIZE,HBURST,HPROT)

下一个周期上升沿,如果是写数据,Master会把写数据HWDATA驱动到总线上;如果是读数据,在上升沿,会由slave将HRDATA驱动到总线上,保证在下一个上升沿的时候,Master能够采样到HRDATA

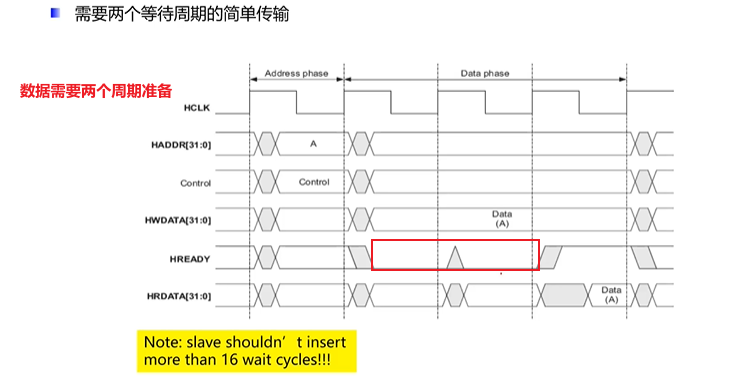

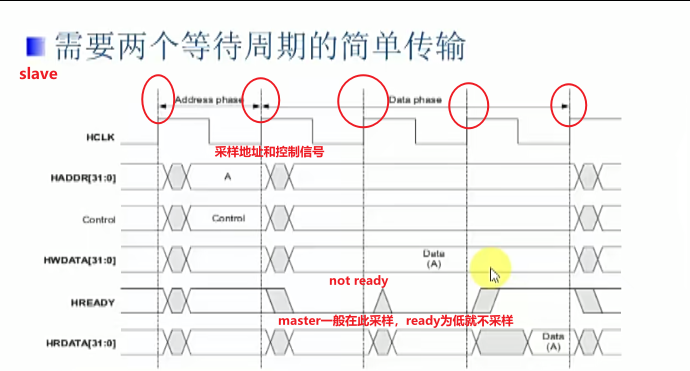

这里是无等待的响应,HREADY在Data phaze上升沿是拉高的,所以数据在下一个周期就驱动过来了;如果HREADY需要几个周期,那么数据可能会经过几个周期之后才会驱动到总线上;如果是写操作,主机必须保持数据信号保持不变;如果是读操作,则从机不需要将有效数据输出到总线上。

slave和master行为

- 如果slave没有ready,就会拉低HREADY

- 总线拉低周期越多,那么会对总线产生的负面影响越大,导致总线性能的下降。AHB等待周期不能超过16个,超过之后需要重新执行任务。

- 数据周期可以通过从机拉低HREADY信号来延迟。从机拉高HREADY代表此次传输已经成功完成。

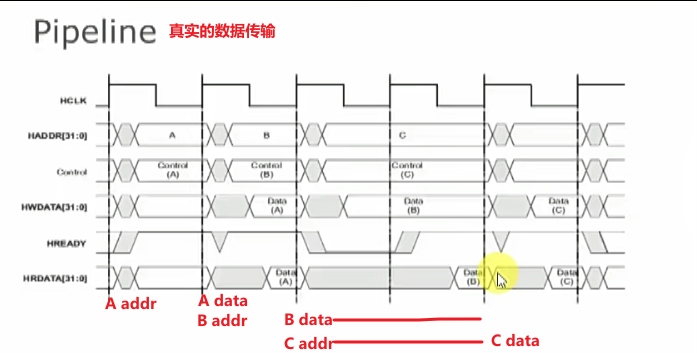

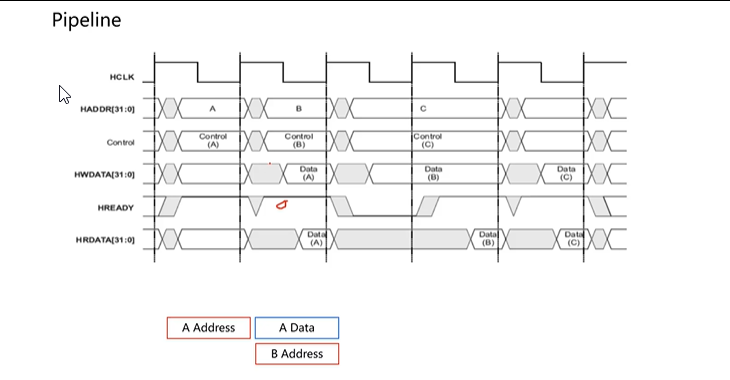

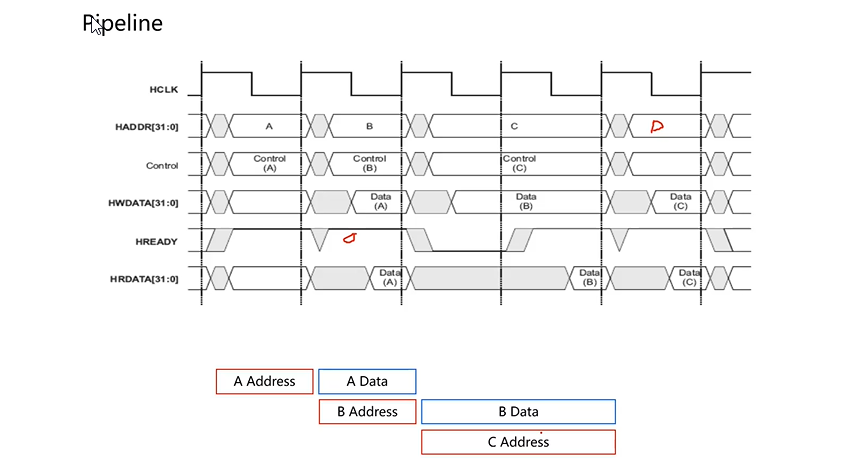

6.6 多笔传输数据

首先在时钟上升沿将地址A驱动到总线上,下一个周期上升沿驱动A地址的数据和地址B,要写数据需要两拍,如果需要读数据,需要四拍到5拍的时间

如果数据需要延迟两个周期才能ready,那么地址D能不能接着地址C驱动到总线上?

不能,因为地址C的数据还没有回来,如果此时驱动地址D,会造成总线数据的丢失,HREADY进行延迟的时候,地址D就需要进行相同的延迟,下一个地址驱动到总线的时候,一定是上一个地址数据HREADY的时候

6.7 AHB控制信号

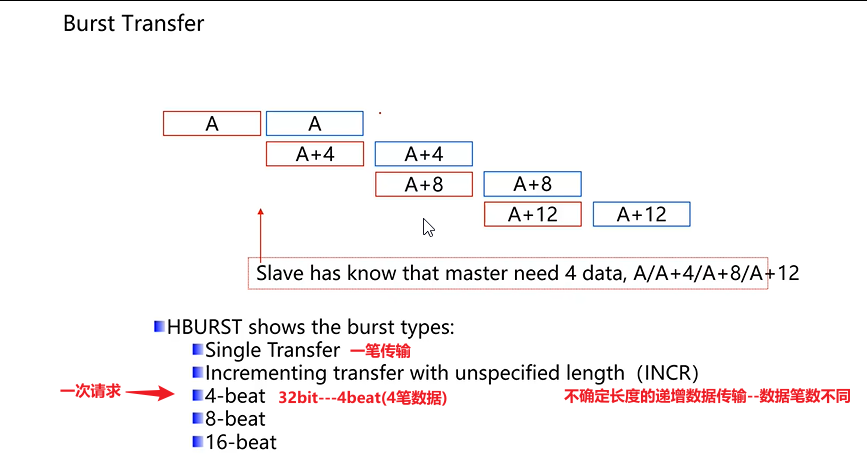

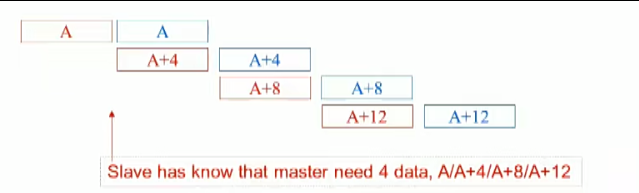

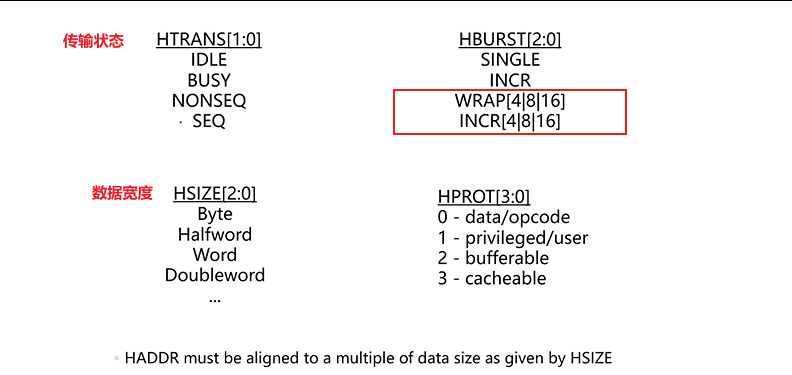

6.7.1 Burst Transfer

一次请求里面有多笔数据传输

- single transter - 一次传输一个地址数据

- Increment Transfer with unspecified length(INCR),依次根据地址递增传输,比如第一次传输A地址数据,第二次传递A+4地址,第三次传递A+8......

- 4 beat - 4拍

- 8 beat - 8拍

slave收到burst传输信号之后,slave就知道要提前准备一些数据,有机会降低等待时间

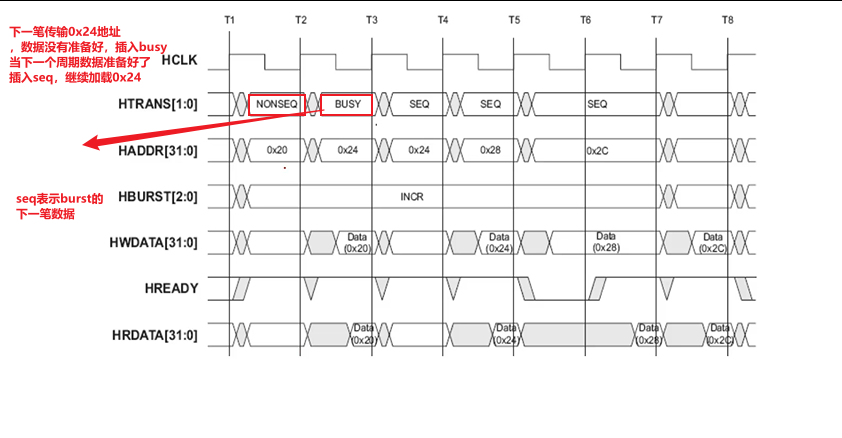

在进行传输的时候,slave等待的时候,将HREADY拉低为0,如果在burst传输的时候,master is not ready,应该怎么做?

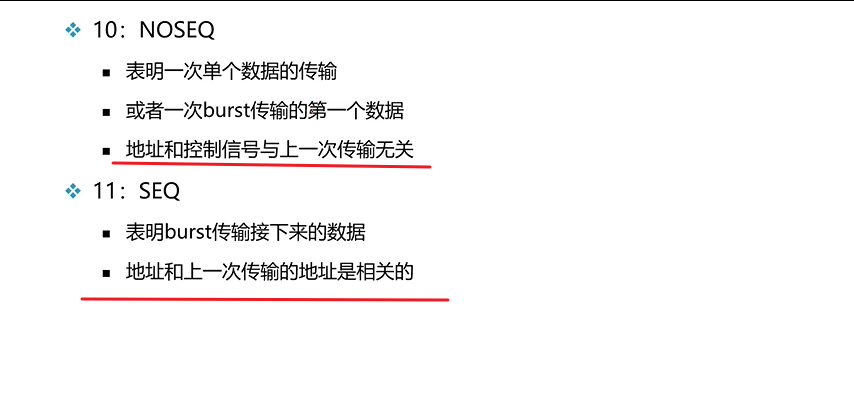

6.7.2 HTRANS

- 如果是第一笔数据传输一定是NOSEQ

- 如果当前传输数据是burst传输,传输到第四笔,SEQ传输

6.7.3 HWRITE & HSIZE

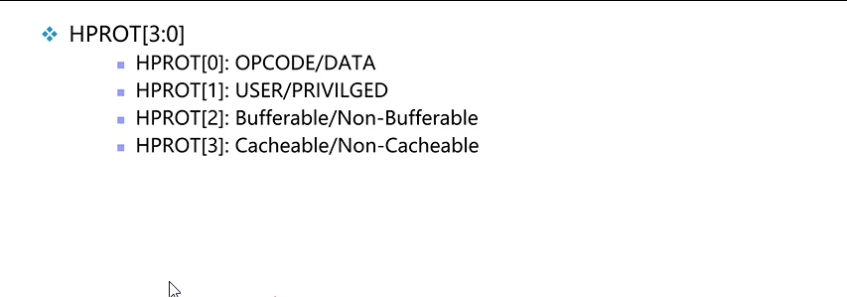

6.7.4 HPROT

6.7.5 控制信号小结

- 每个slave最小的空间就是1k,burst一次只能访问一个slave,一次访问不会跨越两个slave

AMBA总线介绍-01的更多相关文章

- AMBA总线介绍

The Advanced Microcontroller Bus Architecture (AMBA) specification defines an on- chip communication ...

- AMBA总线协议AHB、APB

一.什么是AMBA总线 AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus).ASB (Advanced ...

- AMBA总线协议AHB、APB、AXI对比分析【转】

转自:https://blog.csdn.net/ivy_reny/article/details/56274412 一.AMBA概述 AMBA (Advanced Microcontrolle ...

- AMBA总线基础知识简介

AMBA:Advanced Microcontroller Bus Architecture,是ARMA公司的片内互联总线协议. 1995 - AMBA1.0 APB外设总线及ASB系统总线发布. 1 ...

- vue项目搭建介绍01

目录 vue项目搭建介绍01 vue 项目框架环境搭建: 创建项目: vue 项目创建流程: vue项目搭建介绍01 vue 项目框架环境搭建: vue 项目框架: vue django(类似)(vu ...

- 082 01 Android 零基础入门 02 Java面向对象 01 Java面向对象基础 02 构造方法介绍 01 构造方法-无参构造方法

082 01 Android 零基础入门 02 Java面向对象 01 Java面向对象基础 02 构造方法介绍 01 构造方法-无参构造方法 本文知识点:构造方法-无参构造方法 说明:因为时间紧张, ...

- day01-SpringMVC基本介绍-01

SpringMVC介绍-01 1.离线文档 解压 spring-5.3.8-dist.zip文件. 位置:spring-framework-5.3.8/docs/reference/html/web. ...

- AXI总线介绍

原帖地址:https://wenku.baidu.com/view/7c424c17e3bd960590c69ec3d5bbfd0a7956d5b9.html 1.AXI简介 AXI(Advanc ...

- SPI总线介绍

1. 简介 SPI, Serial Peripheral Interface, 串行外设接口, 是一种高速的.全双工.同步的通信总线SPI在芯片的管脚上只占用四根线 SPI接口主要用于MCU与各种外围 ...

- 干货|Spring Cloud Bus 消息总线介绍

继上一篇 干货|Spring Cloud Stream 体系及原理介绍 之后,本期我们来了解下 Spring Cloud 体系中的另外一个组件 Spring Cloud Bus (建议先熟悉 Spri ...

随机推荐

- springboot产生非法状态异常+空指针

springboot产生非法状态异常+空指针 描述:异常描述为在响应提交后不能执行senderror方法 解决方案: 不是,哥们,你不会真觉得有什么合适的解决方案吧,网上几波前辈大佬各说各的,和我的情 ...

- Android学习--ListView和Tab

产生一个ListView 其中包含很多items,第一个item启动另一个实现了Tab的Activity. 关于tab的使用方式,参见下面blog http://oldshark.blog.163.c ...

- 26、Flutter中命名路由

Flutter 中的命名路由 main.dart中配置路由 void main() { runApp(MaterialApp( theme: ThemeData( appBarTheme: const ...

- 一文详解kube-apiserver认证鉴权能力

本文分享自华为云社区<kube-apiserver认证鉴权能力>,作者: 可以交个朋友. HTTPS为什么要进行身份验证 首先不管是kubectl还是API调用都是通过HTTPS访问kub ...

- 云图说丨初识华为云DDoS防护AAD——DDoS攻击防护平台

DDoS攻击是指分布式拒绝服务,是一种网络攻击手法. 本文分享自华为云社区<[云图说]第297期 初识华为云DDoS防护AAD--DDoS攻击防护平台>,作者:阅识风云. DDoS攻击是指 ...

- 拥抱Serverless释放生产力,探索华为云Serverless车联网最佳实践

华为云Serverless车联网场景解决方案,以FunctionGraph为核心的Serverless化组合方案,使用FunctionGraph.OBS.DIS等技术,可以实现架构的灵活扩展,在出行高 ...

- 科技抗疫,少年可期,为这群有AI的天使开发者疯狂打call

摘要:2020年初新冠突发,在这场抗疫的战斗中,让我们深刻体会到,疫情与每一个人息息相关.有这样一群来自华中科技大学的师生项目团队,他们利用AI技术,助力全球抗疫,他们是怎么做的呢?让我们一起来看看吧 ...

- 震惊!火爆全网的ChatGPT背后使用的数据库居然是……

摘要:ChatGPT承认了自己背后使用的数据库是Cassandra. OpenAI最近发布的AI驱动的智能聊天机器人ChatGPT在互联网上掀起了一阵风暴,热衷于尝试这一新AI成果的网民不在少数.Ch ...

- DevSecOps软件安全开发实践

摘要:DevSecOps 的理念是将安全防护流程有机地融入传统的 DevOps 流程中,为研发安全提供强有力保证,安全工具支撑研发阶段安全要求落地. 本文分享自华为云社区<DevSecOps软件 ...

- 用火山引擎DataTester,这家企业开始了“数据驱动增长”

年末购物季已至,近些年来,预售抵扣.平台满减.品类专享券.大额补贴--动辄四五种计算方法叠加的大促活动,让不少消费者"懵"感十足.同一样商品,到底谁家卖的最便宜?比价平台应声发展而 ...