FPGA功能仿真,门级仿真,后仿真的区别

前言

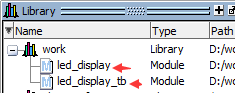

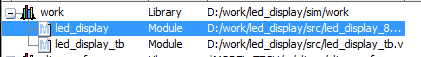

分清楚各种仿真间的关系,工具采用quartus prime16.0,仿真工具采用modelsim10 ae版;项目:led_display;

流程

1.RTL行为级仿真:也叫功能仿真,这个阶段的仿真可以用来检查代码中的语法错误以及代码行为的正确性,其中不包括延时信息。如果没有实例化一些与器件相关的特殊底层元件的话,这个阶段的仿真也可以做到与器件无关。

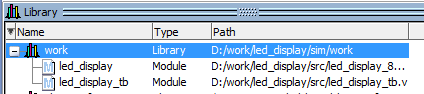

需要的文件:编写的verilog源文件以及tb文件。如果用到了pll等ip核,需要挂载器件库文件。

#set the sim home dir ;

set sim_home D:/work/led_display/sim

#set the src code home dir;

set src_home D:/work/led_display/src

vlib ${sim_home}/work

vmap work ${sim_home}/work

vlog ${src_home}/*.v

vsim -novopt -t 1ns -L altera_ver -L altera_mf_ver -L cycloneive_ver -L sgate_ver -L lpm_ver work.led_display_tb

view wave

add wave *

run @600ns

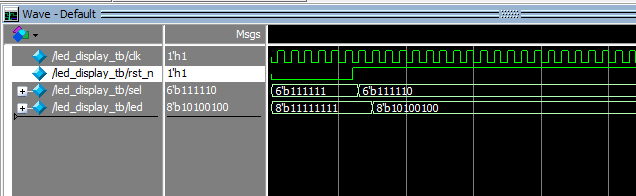

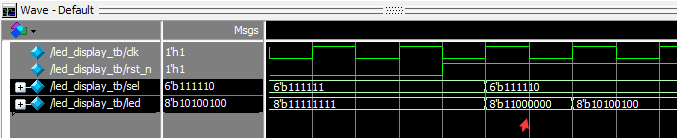

可以看到波形无延时;

2.门级仿真:也叫综合后仿真,综合后生成的网表文件(.vo)加tb仿真;网表是与器件有关的,所以要挂载好相关器件库文件。

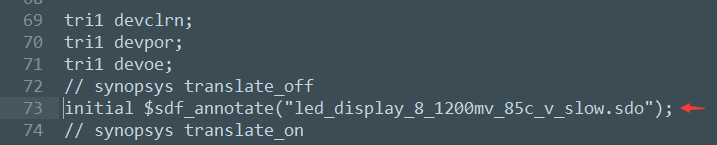

对于quartus生成的vo文件,首先要注释掉其中的挂载sdo文件语句,否则仿真是时序仿真,因为添加了sdo延时文件:

需要的文件:vo网表文件以及tb文件。需要挂载器件库文件。

#set the sim home dir ;

set sim_home D:/work/led_display/sim

#set the src code home dir;

set src_home D:/work/led_display/src

vlib ${sim_home}/work

vmap work ${sim_home}/work

vlog ${src_home}/led_display_8_1200mv_85c_slow.vo ${src_home}/led_display_tb.v

vsim -novopt -t 1ns -L altera_ver -L altera_mf_ver -L cycloneive_ver -L sgate_ver -L lpm_ver work.led_display_tb

view wave

add wave *

run @600ns

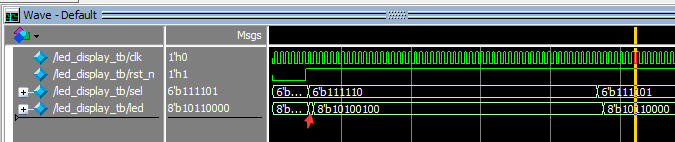

对于本栗子,可以看到门级仿真引入了中间态。

忽略不计。

3.时序仿真:也叫后仿真。网表文件加延时,仿真中会包含延时信息。

需要的文件:vo网表文件以及tb文件以及延时文件sdo(采用脚本挂载)。需要挂载器件库文件。

#set the sim home dir ;

set sim_home D:/work/led_display/sim

#set the src code home dir;

set src_home D:/work/led_display/src

vlib ${sim_home}/work

vmap work ${sim_home}/work

vlog ${src_home}/led_display_8_1200mv_85c_slow.vo ${src_home}/led_display_tb.v

vsim -novopt -t ns -L altera_ver -L altera_mf_ver -L cycloneive_ver -L sgate_ver -L lpm_ver -sdftyp /led_display_tb/u=${src_home}/led_display_8_1200mv_85c_v_slow.sdo work.led_display_tb

view wave

add wave *

run @600ns

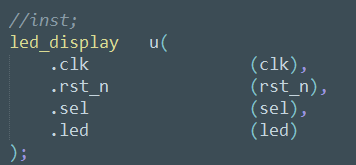

/led_display_tb/u 的意义:前面是tb名,后边是实例化led_display的名字。

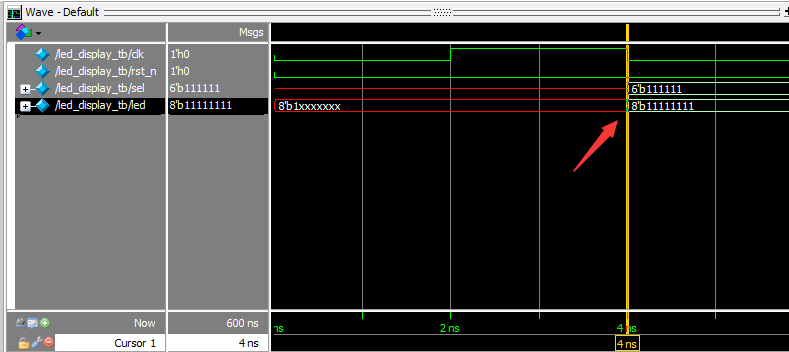

如上图所示,可以看到器件延时大约4ns,包含了延时信息。

以上。

FPGA功能仿真,门级仿真,后仿真的区别的更多相关文章

- Gate level Simulation(门级仿真)

1 什么是后仿真? 后仿真也成为时序仿真,门级仿真,在芯片布局布线后将时序文件SDF反标到网标文件上,针对带有时序信息的网标仿真称为后仿真. 2 后仿真是用来干嘛的? 检查电路中的timing vio ...

- ISE联合modelsim功能仿真和综合后仿真1

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- ISE联合modelsim功能仿真和综合后仿真

1.代码输入 (1).新建一个ISE工程,名字为count4. (2).新建一个verilog文件 (3).选择verilog module 输入file name为count4,单击next默认知道 ...

- 关于fpga的后仿真重要性

也许你天天做些fpga,写完代码就直接编译成功,锁定引脚后,马上使用signaltaII软件. 也许你一天,你发现signaltapII看信号的痛苦,一个源代码文件修改一点,要花个20分钟编译一次. ...

- FPGA前仿真后仿真

前仿真 后仿真 时序(综合后)仿真 时序仿真将时延考虑进去,包括综合后产生的(与.或.非)门时延,还有布局布线产生的时延. 综合(Synthesize),就是将HDL语言设计输入翻译成由与.或.非门和 ...

- [原创]Modelsim后仿真

因调试需要,进行后仿真,ISE生成的sim文件和sdf文件 `timescale ns/ ps module lut_dly ( clkout, fpga_clk, config_in ); outp ...

- Arduino UNO仿真开发环境设置和仿真运行

一. Proteus仿真平台简介 Proteus软件是英国Labcenter electronics公司出版的EDA工具软件(该软件中国总代理为广州风标电子技术有限公司).它不仅具有其它EDA工具软件 ...

- 工艺成型及仿真、铸造工艺及仿真ProCAST软件入门认识介绍

视频源:技术邻 关键词:ProCAST.工艺成型及仿真.铸造工艺及仿真 简介:ProCAST 软件是由美国 USE 公司开发的铸造过程的模拟软件采用基于有限元(FEM)的数值计算和综合求解的方法,对铸 ...

- (数字IC)低功耗设计入门(七)——门级电路低功耗设计优化(续)

前面讲解了门级功耗的优化方法,包括静动态和总体的功耗.现在来记录一下门级层次(有点书也说是在系统级)常用的一种低功耗方法--电源门控. ①电源门控概述与原理 电源门控是指芯片中某个区域的供电电源被关掉 ...

随机推荐

- Ubuntu+OpenCV2.4.11+ CodeBlocks 配置

1.OpenCV 与 CodeBlocks 的安装都比较简单,好多教程. 参考http://www.cnblogs.com/lyutian/p/4425956.html 安装opencv. Codeb ...

- 用php+mysql+ajax实现淘宝客服或阿里旺旺聊天功能 之 前台页面

首先来看一下我已经实现的效果图: 消费者页面:(本篇随笔) (1)会显示店主的头像 (2)当前用户发送信息显示在右侧,接受的信息,显示在左侧 店主或客服页面:(下一篇随笔) (1)在左侧有一个列表 , ...

- 详解ASP.NET MVC 控制器

1 概述 在阅读本篇博文时,建议结合上篇博文:详解ASP.NET MVC 路由 一起阅读,效果可能会更好些. Controller(控制器)在ASP.NET MVC中负责控制所有客户端与服务端的 ...

- java语言中的匿名类与lambda表达式介绍与总结 (Anonymous Classes and Lambda Expressions)

2017/6/30 转载写明出处:http://www.cnblogs.com/daren-lin/p/anonymous-classes-and-lambda-expressions-in-java ...

- 面向对象15.3String类-常见功能-转换

public static void main(String[] args) { //2.1// String s="张三,李四,王五";// String [] arr=s.sp ...

- Tkinter开发第一个桌面程序HelloWorld

在Python3中是tkinter,Python2中是Tkinter Tkinter是Python 官方承认的标准 GUI 方案(de-facto standard),因为是Python自带安装,决定 ...

- Luogu 1559 运动员最佳匹配问题(带权二分图最大匹配)

Luogu 1559 运动员最佳匹配问题(带权二分图最大匹配) Description 羽毛球队有男女运动员各n人.给定2 个n×n矩阵P和Q.P[i][j]是男运动员i和女运动员j配对组成混合双打的 ...

- STL—内存的配置与释放

上一篇我们介绍了STL对象的构造与析构,这篇介绍STL内存的配置与释放. STL有两级空间配置器,默认是使用第二级.第二级空间配置器会在某些情况下去调用第一级空间配置器.空间配置器都是在allocat ...

- Java虚拟机:如何判定哪些对象可回收?

版权声明:本文为博主原创文章,转载请注明出处,欢迎交流学习! 在堆内存中存放着Java程序中几乎所有的对象实例,堆内存的容量是有限的,Java虚拟机会对堆内存进行管理,回收已经"死去&quo ...

- 一个move_uploaded_file()引起的PHP异常与错误的深入理解

背景:我在公司开发一个产品Excel导入到数据库的功能,写起来挺快的,用phpexcel几下就写好了,本地测试挺顺的,git push上去,项目负责人部署到测试环境,就出现问题了.具体问题一句话不好说 ...