004:ZYNQ_AXI总线学习笔记(1)

1. WHAT IS AXI?

AXI是一种高级可扩展接口,是ARM AMBA的一部分。

2. WHAT IS AMBA?

AMBA是高级微控制器总线架构,开放的片内互联总线标准。

3.AXI分类

AXI4/AXI4_ITE/AXI4_STREAM

Memory_mapped 存储器映射 就是读写数据时需要目标地址。

AXI4(AXI4_FULL):用于高性能存储映射。例如:AXI4读写DDR3。

AXI4_LITE:简单的,低吞吐率。比如说一些控制寄存器和状态寄存器。

AXI4_STREAM(ST):高速的流数据通信。

AXI4(AXI4_FULL)和AXI4_LITE需要主机指定读写的地址。AXI4_STREAM(ST)属于流数据,不需要存储器映射不需要地址。

4.存储器映射(Memory_mapped)

主机在对从机进行读写操作时,要先指定一个目标地址(target address),在这个地址对应系统存储空间的地址,表示对该空间进行读写操作。

Memory-Mapped Protocols: In memory-mapped protocols (AXI3, AXI4, and

AXI4-Lite), all transactions involve the concept of transferring a target

address within a

system memory space and data.

AXI_Stream不属于存储器映射。

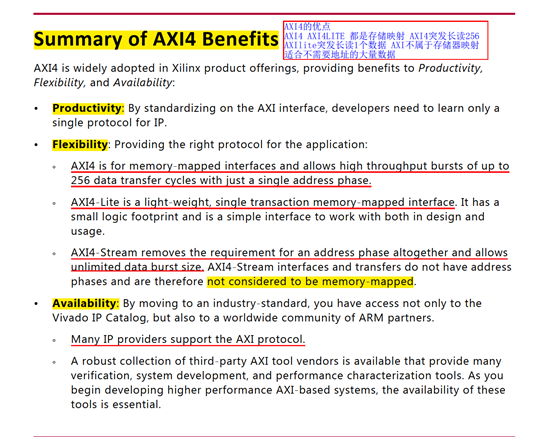

5.AXI4的优势

AXI的优势

生产力:

灵活性:AXI4(支持突发256)和AXI4_lite(不支持突发,1个数据)都属于存储器映射。AXI_ST不属于存储器映射,突发长度不受限制。

可获得性:

6.what is 互联?

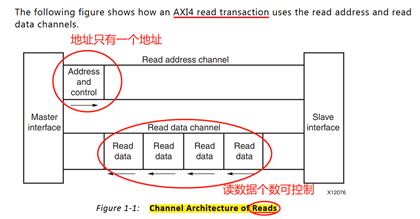

7. five different channels

Both AXI4 and AXI4-Lite interfaces consist of five different channels:

• Read Address Channel

• Write Address Channel

• Read Data Channel

• Write Data Channel

• Write Response Channel

主机发送读地址,从机返回读数据

Data can move in both directions between

the master and slave simultaneously, and data

transfer sizes can vary. The limit in AXI4 is a burst

transaction of up to 256 data transfers.

AXI4-Lite allows only one data transfer per

transaction.

读操作:主机通过读地址通道向从机发出地址和控制,从机通过读数据通道发送读数据。根据突发长度大小返回不同个数的数据。

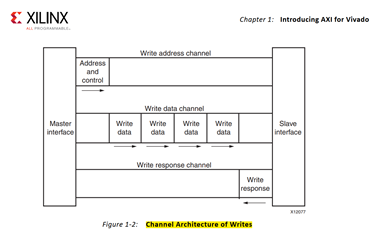

写操作:主机先通过写地址通道发出地址和控制信号。然后通过写数据通道发出数据,等从机接收到数据会发送response信号。

AXI4:

读写地址分离,支持同时读写。

需要一个单一地址然后进行256个数据突发。

As shown in the preceding figures, AXI4:

• Provides separate data and address connections for

reads and writes, which allows

simultaneous, bidirectional data transfer.

• Requires a single address and then bursts up to 256

words of data.

AXI4_LITE:

单次一个数据,不支持突发传输。

AXI4-Lite is similar to AXI4 with some

exceptions: The most notable exception is that

bursting is not supported.

AXI4-Stream:

单通道传输数据类似AXI4的写数据通道,且写数据大小没有突发限制。

The AXI4-Stream protocol defines a single channel for

transmission of streaming data. The AXI4-Stream channel models the write data channel of AXI4.

Unlike AXI4, AXI4-Stream

interfaces can burst an unlimited amount of data.

只关心数据流,不需要地址。

AXI4-Stream

Protocol: Use the AXI4-Stream protocol for applications that typically

focus on a data-centric and data-flow paradigm where the concept of an address

is not

present or not required. Each AXI4-Stream acts as a single unidirectional

channel with a

handshaking data flow.

Infrastructure

IP: An infrastructure IP is a building block used to help assemble

systems. Infrastructure IP tends to be a generic IP that moves or transforms

data

around the system using general-purpose AXI4 interfaces and does not interpret

data.

Examples of infrastructure IP are:

° AXI Register slices (for pipelining)

° AXI FIFOs (for buffering/clock conversion)

° AXI Interconnect IP and AXI SmartConnect IP (for

connecting memory-mapped IP

together)

° AXI Direct Memory Access (DMA) engines (for memory-mapped

to stream

conversion)

° AXI Performance Monitors and Protocol Checkers

(for analysis and debug)

° AXI Verification IP (for simulation-based

verification and performance analysis)

These IP are useful for connecting IP together into a system, but are not

generally

endpoints for data.

DMA常用于存储器映射和stream数据流的转换。

比如说ddr中存储了你的有效数据需要做fft

fft IP的接口时stream流 ddr的数据是存储器映射,做操作需要DMA做数据转换。

A common

approach is to build systems that combine AXI4-Stream and AXI

memory-mapped IP together. Often a DMA engine can be used to move streams in

and out

of memory.

注意AXI Data width

converter 和 AXI Direct Memory

Access支持的AXI接口协议。

8.AXI SmartConnect IP and AXI

Interconnect IP

两者都用于一些主从设备的互联(存储器映射类型)。在一些情况下, AXI

SmartConnect IP可以提供高带宽的链接以及低延迟。

The Xilinx

LogiCORE IP AXI Interconnect and LogiCORE IP AXI SmartConnect cores both connect

one or more AXI memory-mapped master devices to one or more memory-mapped slave

devices; however, the SmartConnect is more tightly integrated into the Vivado

design environment to automatically configure and adapt to connected AXI master

and slave IP with minimal user intervention. The AXI Interconnect can be used in

all memory-mapped designs. There are certain cases for high bandwidth

application where using a SmartConnect provides better optimization. The AXI

SmartConnect IP delivers the maximum system throughput at low latency by

synthesizing a low area custom interconnect that is optimized for important

interfaces.The AXI Interconnect core IP (axi_interconnect)

connects one or more AXI memory-mapped master devices to one or more

memory-mapped slave devices。

今天先到这里。

参考资料:

IHI0022D

UG1037

正点原子ZYNQ嵌入式教程

004:ZYNQ_AXI总线学习笔记(1)的更多相关文章

- openrisc 之 Wishbone总线学习笔记——接口信号定义

这部分内容就是copy下来的,网上到处都有.先看看接口啥样子,在详细说明 接口定义copy http://blog.csdn.net/ce123/article/details/6929897.百度文 ...

- openrisc 之 Wishbone总线学习笔记——总线互联

一,总线命名规范 1,wishbone总线接口信号都是高电平有限 2,wishbone接口信号都是以 _i ,或者是 _o 结束.i表示输入, o表示输出. ()表示该信号为总线信号,总线位宽可以大于 ...

- openrisc 之 Wishbone总线学习笔记——总线特性

特性: 一,互联方式: 支持点到点.共享总线.十字交叉(Crossbar)和基于交换结构(Switch fabric)的互联. 二,数据操作方式:单次读/写操作.块读/写操作,读改写(RMW,Read ...

- PCI 总线学习笔记

转载请注明出处:http://blog.csdn.net/lg2lh/article/details/8042008 PCI的基本协议这里就不介绍了,由于一般的芯片协议都是集成好的,我仅仅须要大体了解 ...

- CAN总线学习笔记

1.CAN总线信息包的格式 问题: 1.CAN总线的初始化要初始化哪些东西? 2.处理器如何与CAN总线之间进行连接? 硬件连接 关于CC2底盘CAN通信的协议格式 备注: 设备地址为01 功能码

- 基于I2C总线的MPU6050学习笔记

MPU6050学习笔记 1. 简述 一直想自己做个四轴飞行器,却无从下手,终于狠下决心,拿出尘封已久的MPU6050模块,开始摸索着数据手册分析,一步一步地实现了MPU6050模块的功能,从MPU60 ...

- IRP IO_STACK_LOCATION 《寒江独钓》内核学习笔记(1)

在学习内核过滤驱动的过程中,遇到了大量的涉及IRP操作的代码,这里有必要对IRP的数据结构和与之相关的API函数做一下笔记. 1. 相关阅读资料 <深入解析 windows 操作系统(第4版,中 ...

- C语言学习笔记之成员数组和指针

成员数组和指针是我们c语言中一个非常重要的知识点,记得以前在大学时老师一直要我们做这类的练习了,但是最的还是忘记了,今天来恶补一下. 单看这文章的标题,你可能会觉得好像没什么意思.你先别下这个 ...

- Web前端学习笔记(001)

....编号 ........类别 ............条目 ................明细....................时间 一.Web前端学习笔记 ...

随机推荐

- 面试有关TCP常问的几个问题

在面试中网络问题是一定会考察的,而TCP协议则是考察网络知识的重点.经常会被问道的问题如下: 请讲一下TCP协议建立连接的过程 请介绍TCP协议中的三次握手和四次挥手是怎么样的 为什么TCP协议要三次 ...

- JS 中一些高效的魔法运算符

这两天有同事说我挺久没更新文章了,不过最近一段时间确实有点忙,一直在忙着两个活动中心的改版,没什么时间来更新文章.今天终于抽空可以写一写. JavaScript 现在每年都会发一个新版本,里面也会新增 ...

- 1019 General Palindromic Number

A number that will be the same when it is written forwards or backwards is known as a Palindromic Nu ...

- .Net之静态资源

介绍 静态文件都存储在Core Web根目录中.默认目录是<content_root>/wwwroot,但可通过 UseWebRoot方法更改访问目录.而content_root是指web ...

- ZOJ 3781 最短路(想法好题目)

题意: 给你一个n*m的矩阵,上面只有两种字符,X或者O,每次可以同时改变相同颜色的一个连通块,上下左右连通才算连通,用最小的步数把这个图弄成全是X或者全是O,题意要是没看懂看下面的样例. ...

- 修改Android手机内核,绕过反调试

本文博客链接:http://blog.csdn.net/qq1084283172/article/details/57086486 0x1.手机设备环境 Model number: Nexus 5 O ...

- Social engineering tookit 钓鱼网站

目录 Set 钓鱼攻击 网站克隆 Set Set(Social engineering tookit)是一款社会工程学工具,该工具用的最多的就是用来制作钓鱼网站. Kali中自带了该工具. 钓鱼攻击 ...

- POJ1611基础带权并查集

题意: 有一个人生病了,和他一个社团或者间接和他有联系的人都会生病,问一共有多少人生病了. 思路: 比较简单和基础的题,带权并查集中的一种,就是记录更新集合元素个数,这个题目我 ...

- UVA11462年龄排序

题意: 给你200w个人的年龄,年龄的范围是1-100,然后让你从小到大排序输出所有人的年龄,题目还特意强调输入文件限制25MB,题目内存限制2MB. 思路: 比较经典又简单的一 ...

- Andrew Ng机器学习算法入门(四):阶梯下降算法

梯度降级算法简介 之前如果需要求出最佳的线性回归模型,就需要求出代价函数的最小值.在上一篇文章中,求解的问题比较简单,只有一个简单的参数.梯度降级算法就可以用来求出代价函数最小值. 梯度降级算法的在维 ...