s3c6410时钟初始化

今天自己写bootloader做时钟初始化时遇到的问题,特记录下来。为了方便理解,我大部分都有截图, 在此我先说明下,图均来自数据手冊。也希望看了本篇文章的同志多多參看数据手冊才干理解的更加透彻,才干真正的锻炼自己的能力。以下程序部分我也拆分成了5个部分分别解释,最后也给出了整个程序。本文假设有什么错误的地方。欢迎各位批评指正。不甚感激。

6410有3个内部PLL(Phase Locked Loop:为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。 很多电子设备要正常工作,通常须要外部的输入信号与内部的振荡信号同步。利 用锁相环路就能够实现这个目的。

)各自是:APLL、MPLL、EPLL。他们被以下7个寄存器控制:

watermark/2/text/aHR0cDovL2Jsb2cuY3Nkbi5uZXQveHVhbl9o/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70/gravity/SouthEast" width="800" height="140" alt="" />

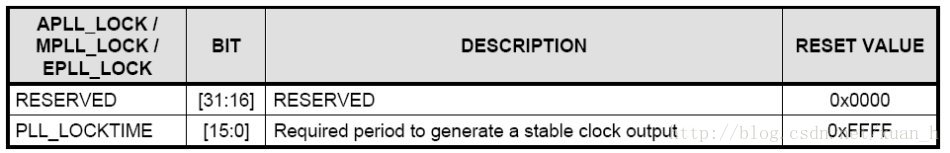

1、 当中前3个寄存器见下图:

所以相应的初始化代码为:

//set the clock time

ldr r0, =0x7e00f000 //APLL_CLOCK

ldr r1, =0xffff

str r1, [r0]

str r1, [r0, #0x4] //MPLL_CLOCK

str r1, [r0, #0x8] //EPLL_CLOCK

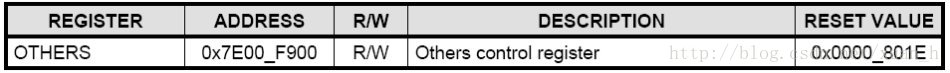

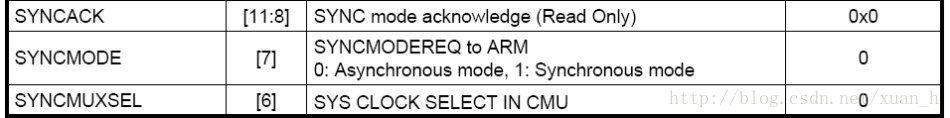

2、 接着设置时钟为异步模式,通过others寄存器设置。图和代码例如以下:

这是others被设置的相应的位。这里截取得当中用到的部分。

//set Async mode

ldr r0, =0x7e00f900 //OTHERS

ldr r1, [r0]

bic r1, #0xc0

str r1, [r0]

//wait for Async mode

loop1:

ldr r0, =0x7e00f900

ldr r1, [r0]

and r1, #0xf00

cmp r1, #0x00

bne loop1

3、6410有几个时钟分频器。以支持各种工作时钟频率。时钟分频比能够被CLK_DIV0、

CLK_DIV1、CLK_DIV2控制。如今我们设置CLK_DIV0。

注:CLK_DIV0 mainly controls the system clocks and special clocks of multimedia IPs。CLK_DIV1

controls MMC, LCD, TV scaler, and UHOST clocks;CLK_DIV2 controls SPI, AUDIO, UART, and IrDA clocks。寄存器的图太大,没附。希望大家自己參看数据手冊。上面有很具体的说明,搜索寄存器名字就可找到。

汇编代码例如以下:

//set the DIV

#define ARM_RATIO 0 //ARM_CLK=DOUTAPLL / (ARM_RATIO + 1)

#define MPLL_RATIO 0 //DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1)

#define HCLK_RATIO 1 //HCLK = HCLKX2 / (HCLK_RATIO + 1)

#define HCLKX2_RATIO 1 //HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1)

#define PCLK_RATIO 3 //PCLK = HCLKX2 / (PCLK_RATIO + 1) <=66Mhz

ldr r0, =0x7e00f020 //CLK_DIV0

ldr r1, =(ARM_RATIO) | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12)

str r1, [r0]

4、接着我们设置输出频率,通过APLL_CON、MPLL_CON设置。

以下先给出计算公式和典型值。

(1) 典型值例如以下图:

(2) 计算公式:FOUT = MDIV * FIN / (PDIV X 2^SDIV)

汇编代码例如以下:

//init the frequence

#define SDIV 1

#define PDIV 3

#define MDIV 266 //final 532Mhz

ldr r0, =0x7e00f00c //APLL_CON

ldr r1, =(1 << 31) | (MDIV << 16) | (PDIV << 8) | (SDIV)

str r1, [r0]

ldr r0, =0x7e00f010 //MPLL_CON

str r1, [r0]

5、最后我们还得设置下clk_src这个寄存器。

6410有很多时钟源。当中包含3个PLL输出。外部振荡器。外部时钟。以及从GPIO配置的其它时钟源.CLK_SRC寄存器控制每一个时钟分频器的时钟源。

这里我么用到了它最低的两位,截图例如以下:

watermark/2/text/aHR0cDovL2Jsb2cuY3Nkbi5uZXQveHVhbl9o/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70/gravity/SouthEast" width="800" height="60" alt="" />

汇编代码例如以下:

ldr r0, =0x7e00f01c

ldr r1, =0x03

str r1, [r0]

完整程序代码例如以下:

//set the clock time

ldr r0, =0x7e00f000 //APLL_CLOCK

ldr r1, =0xffff

str r1, [r0]

str r1, [r0, #0x4] //MPLL_CLOCK

str r1, [r0, #0x8] //EPLL_CLOCK

//set Async mode

ldr r0, =0x7e00f900 //OTHERS

ldr r1, [r0]

bic r1, #0xc0

str r1, [r0]

//wait for Async mode

loop1:

ldr r0, =0x7e00f900

ldr r1, [r0]

and r1, #0xf00

cmp r1, #0x00

bne loop1

//set the DIV

#define ARM_RATIO 0 //ARM_CLK=DOUTAPLL / (ARM_RATIO + 1)

#define MPLL_RATIO 0 //DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1)

#define HCLK_RATIO 1 //HCLK = HCLKX2 / (HCLK_RATIO + 1)

#define HCLKX2_RATIO 1 //HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1)

#define PCLK_RATIO 3 //PCLK = HCLKX2 / (PCLK_RATIO + 1) <=66Mhz

ldr r0, =0x7e00f020 //CLK_DIV0

ldr r1, =(ARM_RATIO) | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12)

str r1, [r0]

//init the frequence

#define SDIV 1

#define PDIV 3

#define MDIV 266 //final 532Mhz

ldr r0, =0x7e00f00c //APLL_CON

ldr r1, =(1 << 31) | (MDIV << 16) | (PDIV << 8) | (SDIV)

str r1, [r0]

ldr r0, =0x7e00f010 //MPLL_CON

str r1, [r0]

ldr r0, =0x7e00f01c

ldr r1, =0x03

str r1, [r0]

mov pc, lr

s3c6410时钟初始化的更多相关文章

- s3c6410_时钟初始化

参考: 1)<USER'S MANUAL-S3C6410X>第三章 SYSTEM CONTROLLER 2)u-boot/board/samsumg/smdk6410/lowlevel_i ...

- LPC1788系统时钟初始化

#ifndef __SYS_H_ #define __SYS_H_ #include "common.h" #define SystemCoreClock 120000000 ...

- dsPIC33EP 时钟初始化程序

//文件名p33clk.h #ifndef _P33CLK_H_ #define _P33CLK_H_ //#include "p33clk.h" #define WDT_ENB ...

- STM32_3 时钟初始化分析

在startup文件中,调用了2个函数,一个是System_Init, 另一个是main. System_Init()在system_stm32f10x.c 这个文件中,先看一下时钟树,再分析一下这个 ...

- ARM系统时钟初始化

2440时钟体系,12MHz的晶振 6410时钟体系,12MHz的晶振 210时钟体系,24MHz晶振 时钟初始化:1.设置locktime 2.设置分频系数 4.设置CPU到异步工作模式 3.设置f ...

- ARM时钟初始化

2440: S3C2440可以使用外部晶振(XTIpll)(默认为12MHZ)和外部时钟(EXTCLK)两种方式输入时钟信号.它由跳线OM[3:2]决定.S3C2440 默认的工作主频为12MHz(晶 ...

- X-005 FriendlyARM tiny4412 uboot移植之时钟初始化

<<<<<<<<<<<<<<<<<<<<<<<<< ...

- u-boot分析(六)----时钟初始化

u-boot分析(六) 上篇博文我们按照210的启动流程,分析到了关闭看门狗,今天我们继续按照u-boot的启动流程进行分析,今天我们会主要分析时钟的初始化. 今天我们会用到的文档: 1. ...

- STM32时钟初始化函数SystemInit()详解【转】

花了一天的时间,总算是了解了SystemInit()函数实现了哪些功能,初学STM32,,现记录如下(有理解错误的地方还请大侠指出): 使用的是3.5的库,用的是STM32F107VC,开发环境RVM ...

随机推荐

- Flask中cookie和session设置与csrf原理攻防

Flask之操作cookie app.py from flask import Flask, request, Response app = Flask(__name__) @app.route('/ ...

- LINUX软件包的安装、升级、删除

1.安装和升级一个rpm 包: [root@localhost beinan]#rpm -vih file.rpm 注:这个是用来安装一个新的rpm 包: [root@localhost beinan ...

- Blow up the city

Blow up the city 时间限制: 1 Sec 内存限制: 128 MB 题目描述 Country A and B are at war. Country A needs to organ ...

- h5+css3+Jq

1.侧边栏划出一个信息框 通常鼠标浮动侧边栏都会划出一个信息框,每个信息框距离侧边栏的距离是相等的,所以处理此问题的方法就是 量取信息框距离侧边栏的距离,信息框设置绝对定位,父元素设置相对定位之后,信 ...

- Codeforces 220B

B. Little Elephant and Array time limit per test 4 seconds memory limit per test 256 megabytes input ...

- ModelAndView返回mav时,报404

报404的可能性太多了 简单来看,404后边有信息,说明请已经分配到了控制器 经过调试发现,mav已经分配到了页面 原因,modelandview的包导入错误,正确的包是 import org.spr ...

- GIT → 04:Git与代码托管平台

4.1 Git 与 GitHub比较 Git 是一个版本管理工具 , 只在本地使用的一个版本管理工具,其作用就是可以让你更好的管理你的程序,比如你原来提交过的内容,后面虽然修改过,但是通过git这个工 ...

- IO流10 --- 缓冲流(字节型)实现非文本文件的复制 --- 技术搬运工(尚硅谷)

字节型缓冲流,BufferedOutputStream默认缓冲区大小 8192字节byte,满了自动flush() @Test public void test6(){ File srcFile = ...

- java-多线程的入门_进阶总结

多线程 概述图 1.概述 进程:正在执行中的程序,其实时应用程序在内存中运行的那片空间. 线程:进程中的一个执行单元,负责进程中的程序的运行,一个进程中至少要有一个线程. (进程可以理解为是一个QQ程 ...

- jsp必填项加红色星号

<th><font color=red>*</font>文字:</th>