奇分频电路如何实现? 负沿触发&非负沿触发

请设计一个奇分频电路,占空比为50%?

以下给出解答:

1、带负沿触发

module div //带负沿触发

#(parameter N = 5) //定义分频参数

(

input sys_clk ,

input sys_rst_n ,

output div_clk

); // 核心:在上下边沿的计数器 计数至 N/2 翻转 计数至 N-1 再翻转

// 上下边沿脉冲信号 或运算 即可得到最终的 奇分频结果 占空比50%

reg clk_pose ; //上升沿

reg clk_nege ; //下降沿

reg [N:0] cnt_pose ; //上升沿计数

reg [N:0] cnt_nege ; //下降沿计数 always@(posedge sys_clk or negedge sys_rst_n) begin //在上升沿计数

if(!sys_rst_n)

cnt_pose<='d0;

else if(cnt_pose==N-1)

cnt_pose<='d0;

else

cnt_pose<=cnt_pose+'d1;

end

always@(negedge sys_clk or negedge sys_rst_n) begin //在下升沿计数

if(!sys_rst_n)

cnt_nege<=1'b0;

else if(cnt_nege==N-1)

cnt_nege<='d0;

else

cnt_nege<=cnt_nege+'d1;

end always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

clk_pose<=1'b0;

else if(cnt_pose==N/2)

clk_pose<=~clk_pose;

else if(cnt_pose==N-1)

clk_pose<=~clk_pose;

else

clk_pose<=clk_pose;

end

always@(negedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

clk_nege<=1'b0;

else if(cnt_nege==N/2)

clk_nege<=~clk_nege;

else if(cnt_nege==N-1)

clk_nege<=~clk_nege;

else

clk_nege<=clk_nege;

end assign div_clk= clk_nege |clk_pose ; //上升沿 和下降沿 或运算 得到 奇分频 endmodule

`timescale 1ns/1ns

module tb_div();

reg sys_clk ;

reg sys_rst_n ;

wire div_clk ; initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end always #10 sys_clk<=~sys_clk; div #(.N()) //可自己定义想要的分频参数

div_inst(

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n) ,

.div_clk (div_clk)

); endmodule

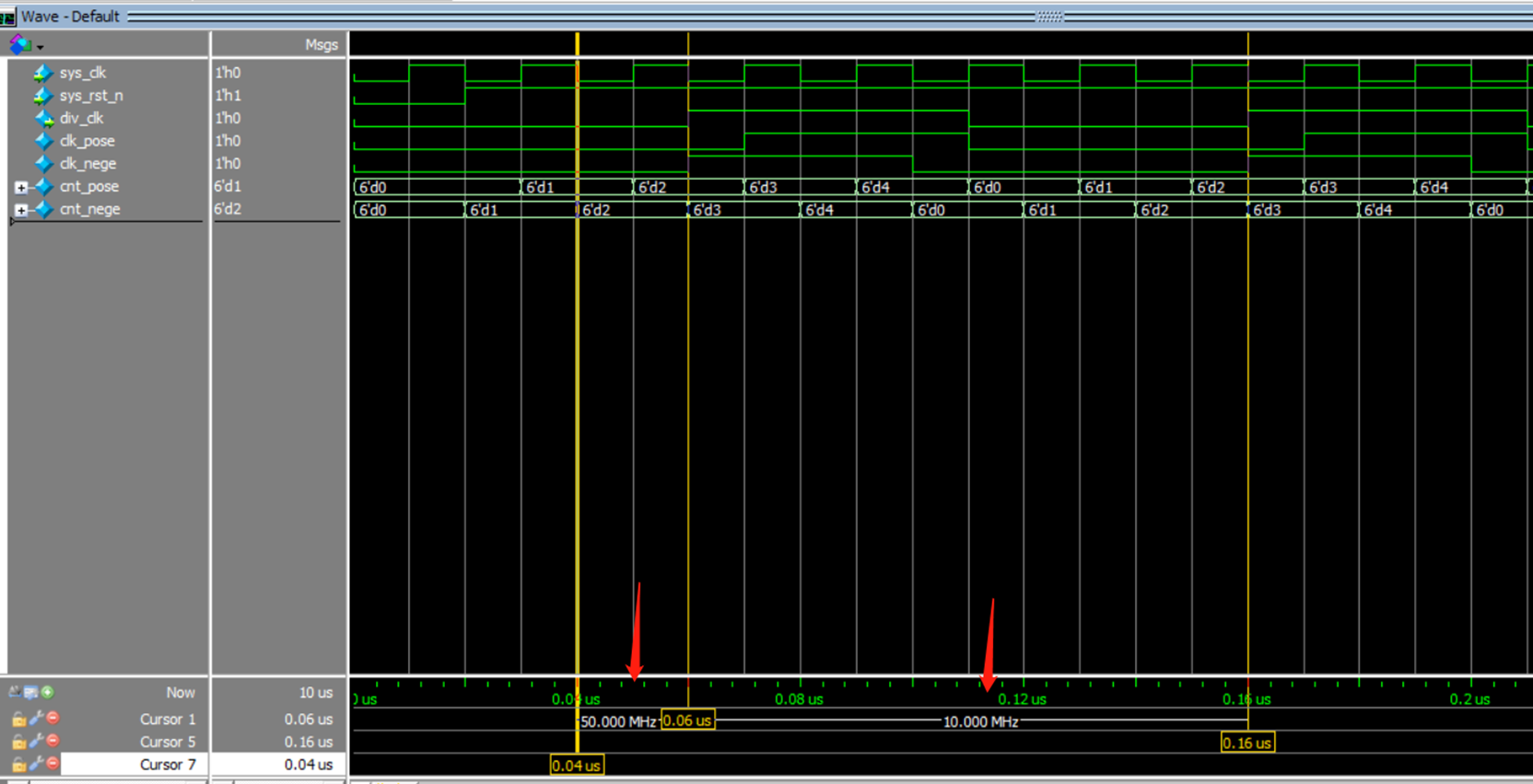

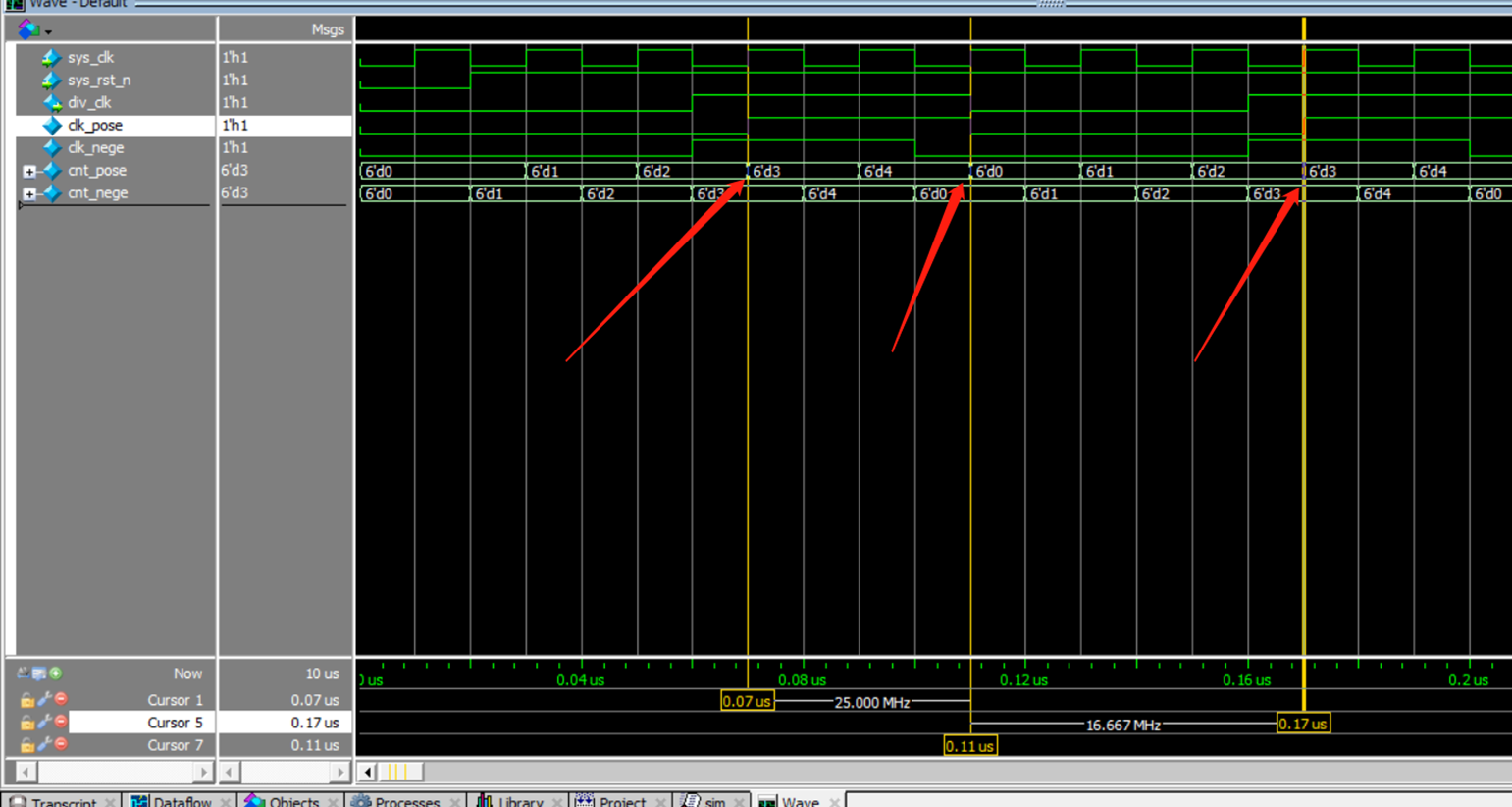

波形图如下

2、不带负沿触发

module div //不带负边沿触发

#(parameter N = 5) //定义分频参数

(

input sys_clk ,

input sys_rst_n ,

output div_clk

); // 核心:构造一个与时钟相反的新时钟 在原时钟域下 在前N/2 时钟周期保持0 后面 N/2+1 ~N-1 翻转

// 在新时钟域下 在原时钟域下 在前N/2 时钟周期保持0 后面 N/2+1 ~N-1 翻转

//在新时钟域下 对分频寄存器打拍一拍

//对两个时钟域下的分频时钟寄存器想或 得到 奇分频结果 占空比50%

reg clk_0 ; //原时钟域

reg clk_1 ; //新时钟域下

reg clk_2 ; //新时钟域下

reg [N:0] cnt ; //原时钟域上升沿计数

wire sys_clk_0 ; //构造的新时钟域 assign sys_clk_0=~sys_clk ; always@(posedge sys_clk or negedge sys_rst_n) begin //在上升沿计数

if(!sys_rst_n)

cnt<='d0;

else if(cnt==N-1)

cnt<='d0;

else

cnt<=cnt+'d1;

end always@(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

clk_0<=1'b0;

else if(cnt<=N/2)

clk_0<=1'b0;

else

clk_0<=1'b1;

end always@(posedge sys_clk_0 or negedge sys_rst_n) begin

if(!sys_rst_n) begin

clk_1<=1'b0;

clk_2<=1'b0;

end

else if(cnt<=N/2) begin

clk_1<=1'b0;

clk_2<=clk_1;

end

else begin

clk_1<=1'b1;

clk_2<=clk_1;

end

end assign div_clk= clk_0 |clk_2 ; //对两个时钟域下的分频时钟寄存器想或 得到 奇分频结果占空比50% endmodule

`timescale 1ns/1ns

module tb_div();

reg sys_clk ;

reg sys_rst_n ;

wire div_clk ; initial begin

sys_clk<=1'b0;

sys_rst_n<=1'b0;

#20

sys_rst_n<=1'b1;

end always #10 sys_clk<=~sys_clk; div #(.N()) //可自己定义想要的分频参数

div_inst(

.sys_clk (sys_clk) ,

.sys_rst_n (sys_rst_n) ,

.div_clk (div_clk)

); endmodule

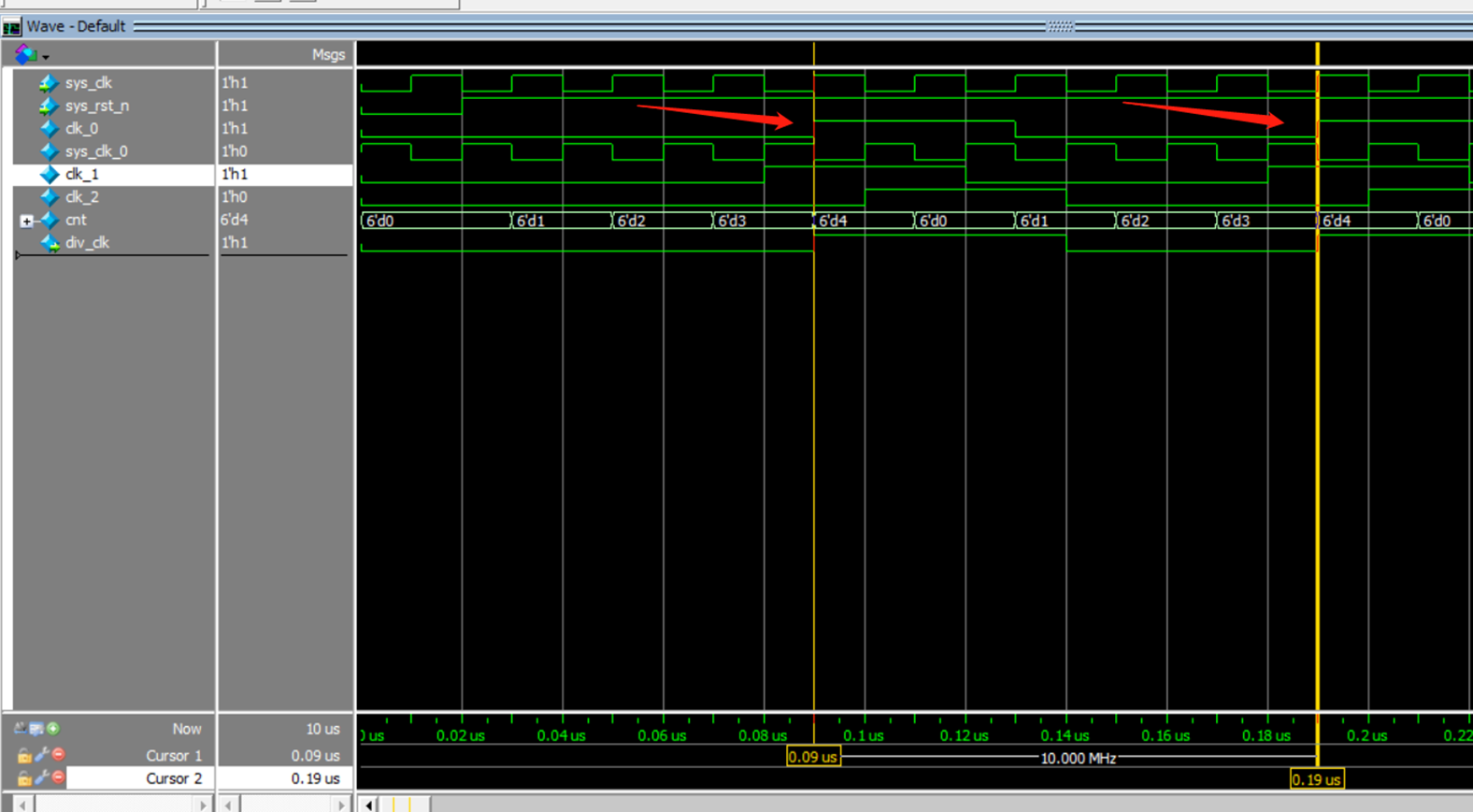

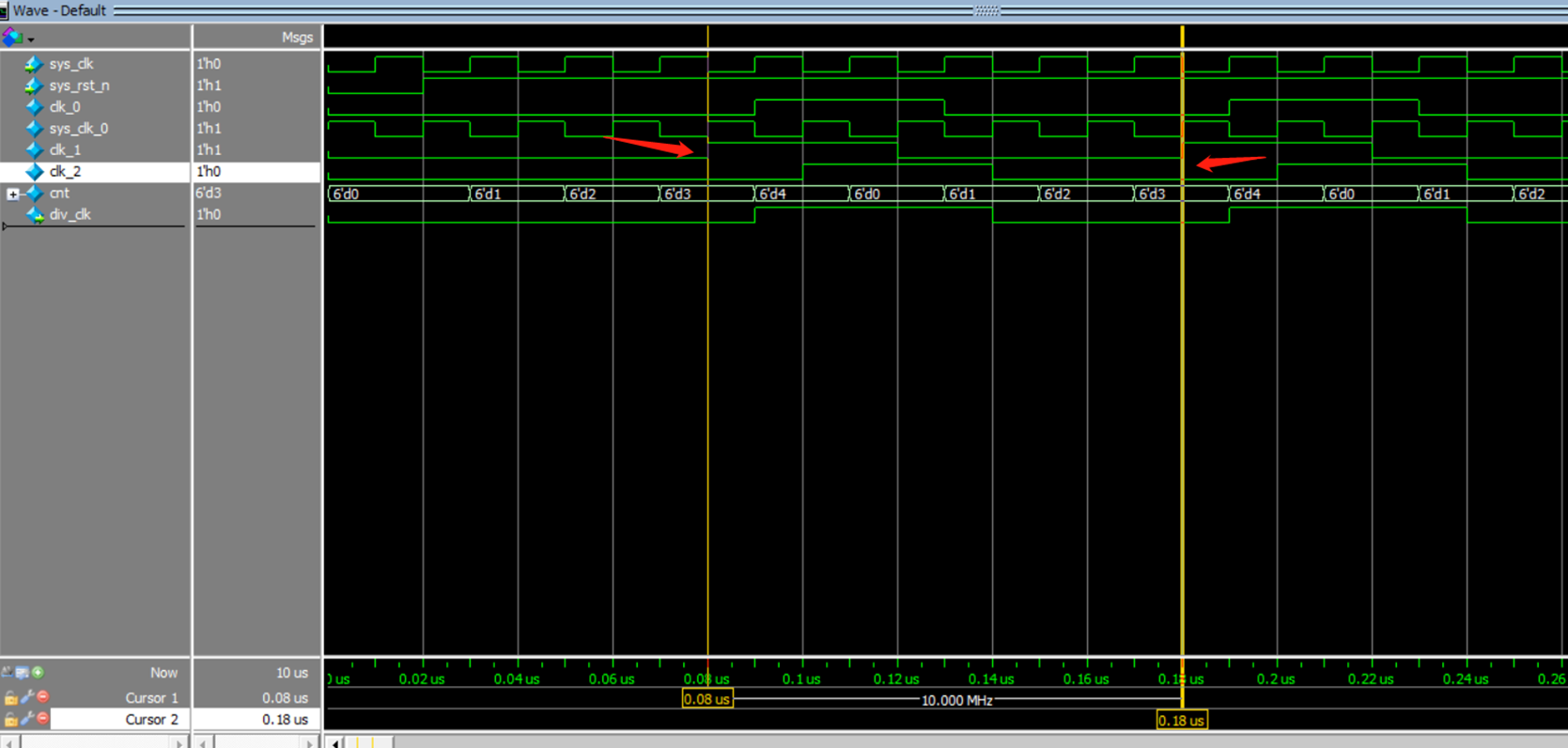

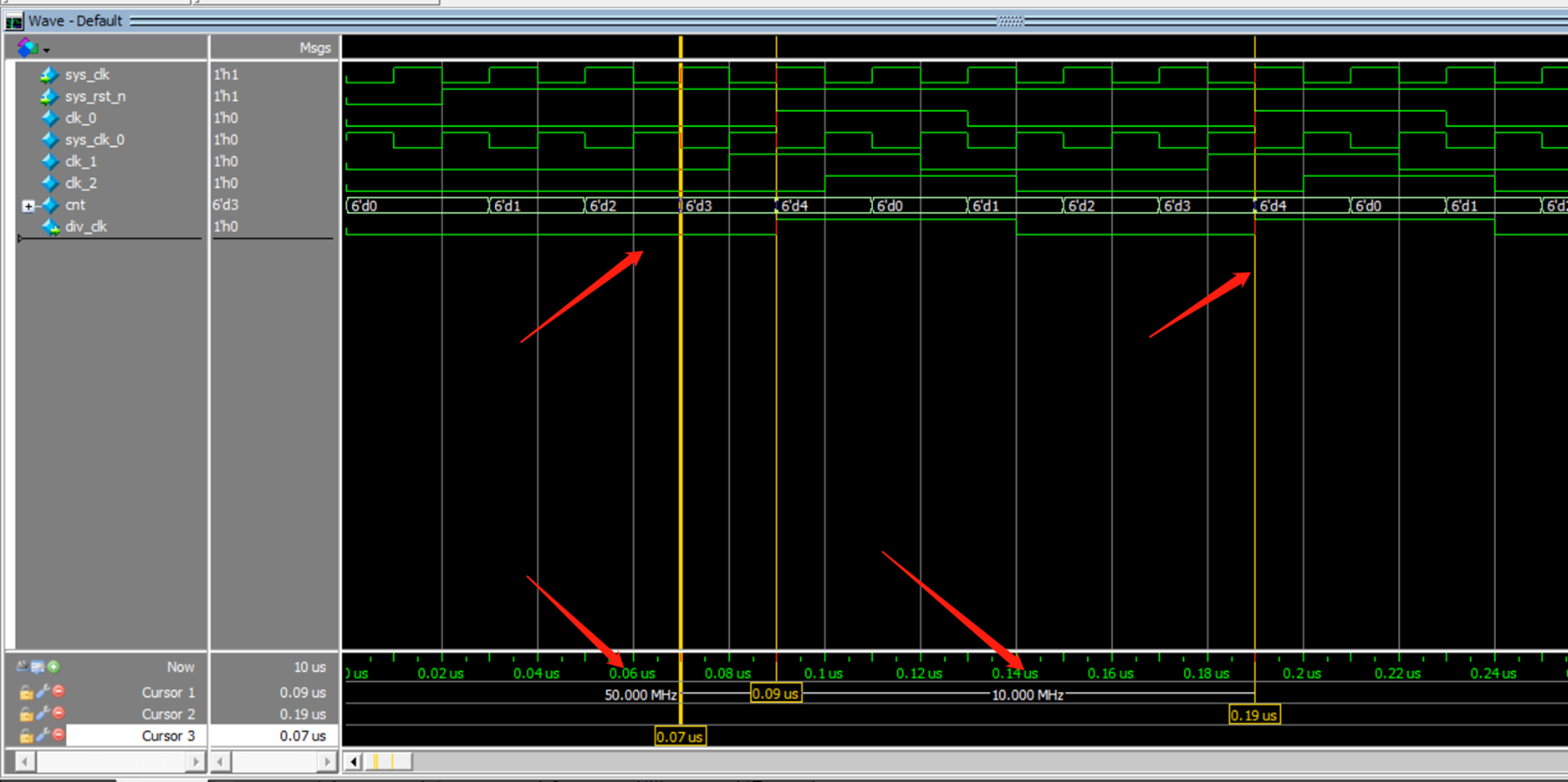

波形图如下:

以上是本人对奇分频电路的总结,若有不对的地方,敬请指正,万分感谢。

参考资料:

1、奇数分频--不使用负边沿触发verilog实现(占空比50%) - 影-fish - 博客园 (cnblogs.com)

奇分频电路如何实现? 负沿触发&非负沿触发的更多相关文章

- Verilog学习笔记简单功能实现(六)...............计数分频电路

在分频器电路中最重要的概念有两个:1)奇分频/偶分频:2)占空比. A)其中最简单的就是二分频电路,占空比为50%,其Verilog程序为 module half_clk(clr,clk_in,clk ...

- 背水一战 Windows 10 (24) - MVVM: 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令

[源码下载] 背水一战 Windows 10 (24) - MVVM: 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令 作者:webabcd ...

- 实例浅析epoll的水平触发和边缘触发,以及边缘触发为什么要使用非阻塞IO

一.基本概念 我们通俗一点讲: Level_triggered(水平触发):当被监控的 ...

- MVVM: 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令

介绍背水一战 Windows 10 之 MVVM(Model-View-ViewModel) 通过 Binding 或 x:Bind 结合 Command 实现,通过非 ButtonBase 触发命令 ...

- epoll的水平触发和边缘触发,以及边缘触发为什么要使用非阻塞IO

转自:http://www.cnblogs.com/yuuyuu/p/5103744.html 一.基本概念 ...

- [原创][FPGA]时钟分频之奇分频(5分频)

0. 简介 有时在基本模块的设计中常常会使用到时钟分频,时钟的偶分频相对与奇分频比较简单,但是奇分频的理念想透彻后也是十分简单的,这里就把奇分频做一个记录. 1. 奇分频 其实现很简单,主要为使用两个 ...

- 条件触发和边缘触发 及 epoll 的长处

条件触发: 仅仅要输入缓冲有数据就会一直通知该事件 边缘触发: 输入缓冲收到数据时仅注冊1次该事件.即使输入缓冲中还留有数据,也不会再进行注冊 水平触发(level-triggered.也被称为条件触 ...

- jenkins 判断是手动触发还是定时器触发

根据变量BUILD_CAUSE的值可以判断本次触发是手动触发还是定时器触发 手动触发:MANUALTRIGGER 定时器触发:TIMERTRIGGER

- epoll的边缘触发与水平触发

epoll的边缘触发与水平触发 Tcp连接是双向的,内核为每个socket维护两个缓冲区,读缓冲区与写缓冲区,内核会一个关注这两个缓冲区,当采用水平触发时,对于写缓冲区而言,如果有多余空间可写,对于读 ...

- 如何用代码而非事件触发PBO

通常我们通过抛出事件触发PBO,但若没有事件发生时,我们其实也可以用代码强制发出命令. 写法如下: CL_GUI_CFW=>SET_NEW_OK_CODE( NEW_CODE = <uco ...

随机推荐

- react 兄弟组件传值(发布订阅,使用于任何组件传值,包括vue)

react中兄弟组件传值常规操作一般是,A组件传给父组件,父组件再传给B组件 非常规操作 利用 pubsub-js 在Home组件内调用 PubSub.publish("第一个参数是事件名 ...

- 聊一聊 GDB 调试程序时的几个实用命令

一:背景 1. 讲故事 用惯了宇宙第一的 Visual Studio 再用其他的开发工具还是有一点不习惯,不习惯在于想用的命令或者面板找不到,总的来说还是各有千秋吧,今天我们来聊一下几个在调试中比较实 ...

- 如何将c#在线编辑器嵌入自己项目

如何将c#在线编辑器嵌入自己项目 首先我们需要介绍一下这个在线编辑器,当前的在线编辑器支持c#的代码编译运行,并且无需后台服务,基于WebAssembly实现的在浏览器端去执行我们的c#代码,基于Ro ...

- 字符串处理------Brute Force与KMP

一,字符串的简单介绍 例:POJ1488 http://poj.org/problem?id=1488 题意:替换文本中的双引号: #include <iostream> #includ ...

- 2020-11-24:n个物品每个物品都有一定价值,分给2个人,怎么分两个人的价值差最小?

福哥答案2020-11-24: 背包问题:背包容量是SUM/2. 每个物体的体积是数的大小,然后尽可能的装满背包. golang代码如下: package main import ( "fm ...

- 2020-12-26:mysql中,表person有字段id、name、age、sex,id是主键,name是普通索引,age和sex没有索引。select * from person where id=1 and name='james' and age=1 and sex=0。请问这条语句有几次回表?

2020-12-26:mysql中,表person有字段id.name.age.sex,id是主键,name是普通索引,age和sex没有索引.select * from person where i ...

- ubuntu搜狗输入法显示简体中文,输入却是繁体中文问题解决方案

一.现场重现 我的ubuntu版本是20.04,搜狗输入法版本是2.4.在输入的时候发生了如下场景: 明明输入法上是简体中文,可是打出来就变成了繁体中文! 二.解决方案 1.尝试 网上许多答案都是按下 ...

- docker部署gitlab CI/CD (二)终篇:部署gitlab runner和添加gitlab-ci.yml文件 终极踩坑版

关于gitlab部署的教程还好,有的看,但到了cicd环节,简直痛苦面具,教程虽多,但断断续续,先不说大部分都是只截取片段,让人云里雾里,不会的看不懂,懂的不需要看,根据步骤跑不起来不说,改了一堆,完 ...

- Linux 下的动态库、静态库与环境变量

最近这几天在处理集群软件的过程中,遇到各种各样的库和环境变量的问题,被虐的不清!趁此机会,整理了一下 Linux 下静态库.动态库(共享库)和环境变量的一些知识,与大家共享一下. 库的种类 Linux ...

- Java革命性ORM框架之快速上手的Jimmer

Jimmer是一款革命性的ORM框架,它的目标是提供一个简单易用的API,帮助开发人员更加轻松地操作数据库.Jimmer使用了Java 8的新特性,如Lambda表达式和Stream API,使得代码 ...