arm trustzone

arm的trustzone并不涉及到具体的crypto算法,只是实现:

1) 敏感信息的安全存储;

2) 控制bus和debug的安全访问,保证信息不被泄露;

trustzone是system_level的实现,涉及到软硬件,硬件方面包括:

1) ARM processor;

2) Bus fabric;

3) system peripheral IP;

硬件devices被attacked的几种方式:

1) Hack attack,通过植入病毒和木马,来执行一些非法的软件。

2) Shake attack,attackers可以物理访问到device,并且可以实现一些主动的动作,force pins,

利用JTAG,BIST,IO boundary scan,reprogrammming memory device。

3) Lab attack,attackes可以通过实验室设备,实验device,在silicon的metal layer加探针等操作。

危险性极大。

目前硬件中常用的几种security 实现方式:

1) 外加hardware security module,像SIM card这样。并不通用,而且成本高。

2) 在内部加入自己的hardware security module,security与normal world之间的数据交换复杂,因为没有形成

一个系统的解决方案。

3) software virtualization,任何带mmu的processor都可以实现,security通过hypervisor来实现,

但是对于DMA和GPU这样的master,没有解决方案。

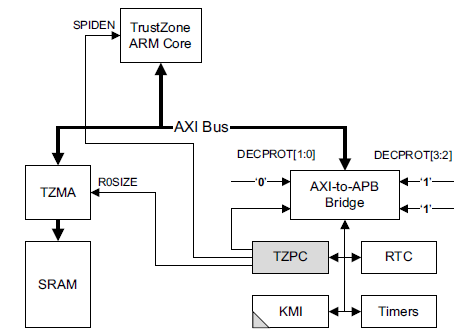

trustzone的硬件architecture:主要分为system achitecture,processor architecture,debug architecture

1) system achitecture:主要是指,bus中已经包含security signal,memory也可以通过增加一根security的信号,来物理上将

硬件bus系统隔绝为两个world。

2) Processor architecture:

arm-a9之后的processor都直接支持secure,两个virtual processor,之间切换,只能通过

指令SMC(Secure Monitor Call),或其他的一些exception,IRQ,FIQ,external Data Abort,external Prefetch Abort

当前的processor处在secure还是non-secure,通过coprocessor,CP15中的寄存器SCR(Secure Config Reg)来表示,

其中有一个NSbit,当processor处在monitor状态时,该状态位无效。

mmu,支持secure扩展,可以看做是两个virtual mmu,其中的TLB(Translation Lookaside Buffers),可以同时包含secure和

non-secure,在切换时,也不需要切换。

cache,加入secure特性的扩展后,world switch时,不需要再进行cache flush,任何non-lockdown的cache line都可以被evict,

与security属性无关,也就是说,secure的cache line可以被evict,为non-secure cache line加载。

interrupt,secure的interrupt,的很多控制寄存器,如mask,enable,clear,必须是由security world来访问。

推荐实现,IRQ应用在normal world,FIQ应用在secure world,monitor状态下,所有的irq被mask掉。

exception vector,支持TZ的proceesor的有三组exception vector tables,分别是normal world,secure world,

Monitor mode。各个基地址,可以通过CP15中的VBAR(Vector Base Address Register)

Multiprocessor system,主要分为SMP(Symmetric Multi-processor),AMP(Asymmetric Multi-processor),主要影响

在于软件,AMP结构中,软件调度更加复杂,

3) Debug architecture:可以分为processor debug components和system debug components。

processor debug:针对secure和privilege加入了更多的enable控制信号,

Secure privilege invasive debug(JTAG),SPIDEN signal

Secure privilege non-invasive debug(trace),SPNIDEN signal

Secure user invasive debug,SUIDEN signal

Secure user non-invasive debug,SUNIDEN signal

secure debug只有在确认安全的环境下,才能打开

global的enable信号:

global invasive debug mode,DEGEN

global non-invasive debug mode,NIDEN

对于multiprocessor debug control,每个cluster中的每个processor都有这些control signal。

armv7之后,每个processor内部都有PMU(performance Monitor Unit),内部counter记录processor执行

指令中的各个状态,如cache line evictions等,可以通过CP15的设置,来防止被non-secure非法看到

system debug:通过arm的coresight来保证,

arm提供的支持TrustZone的hardware的IP;

1) TrustZone Protection Controller(TZPC),主要实现对各个peripheral的secure的动态权限设置。再通过bus发送过来的状态,来

判断,该笔操作是否合法。

2) TZASC(TrustZone Address Space Controller),典型应用是将区分同一个AXI slave,比如chip外的DRAM,只挂载一个,

但是我们可以将其地址空间分为一半secure,一半non-secure

3) 其他的常用组建,Cache Controller,DMA Controller,interconnect,GIC

TrustZone Software achitecture:软件的实现方式比较灵活,最复杂的是在Secure World单独运行自己的OS(AMP结构),

最简单的是在Secure World,中使用一个标准的lib(SMP结构)。

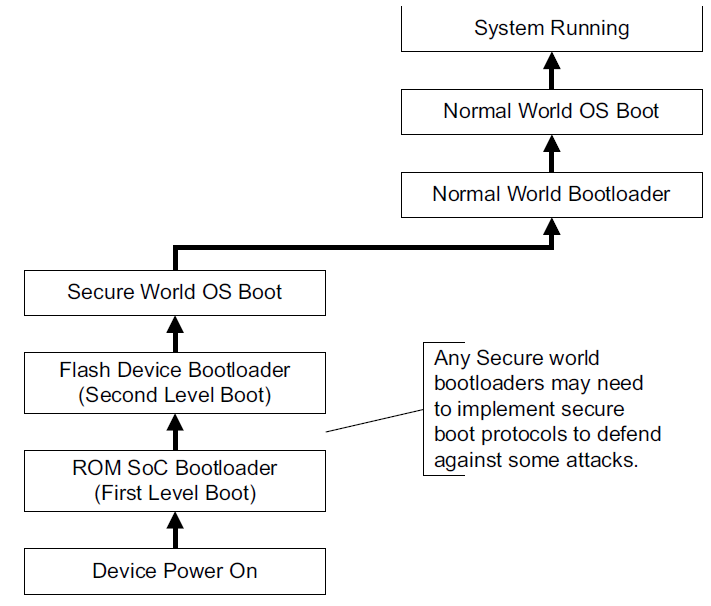

在一个secure system中,boot是信任链的最底层,是最重要的一部分,TrustZone要求,boot都是开始自Secure World。

secure boot之后,需要加cryptographic checks对bootload进行检查,算法一般选择RSA-PSS,公钥和golden签名也都保存在

device中,boot的时候,进行验证。

在进行secure world的切换时,从secure到non-secure,可以直接修改CPSR寄存器,直接进行world的切换,

如果processor中带有NEON,VFP这样的coprocessor reg,进行context-switching,可以选择Lazy context switch,

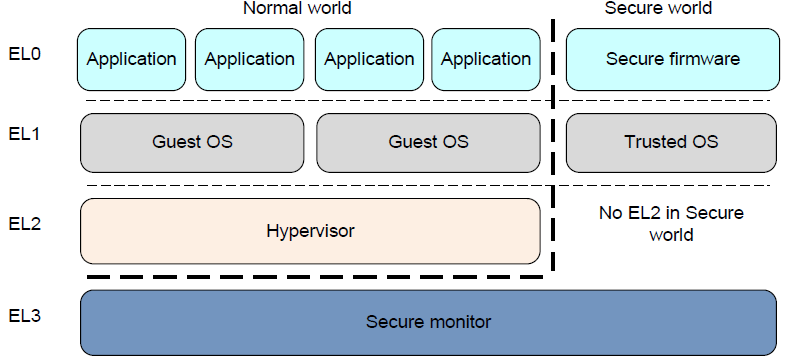

AARCH64架构中的secure结构:

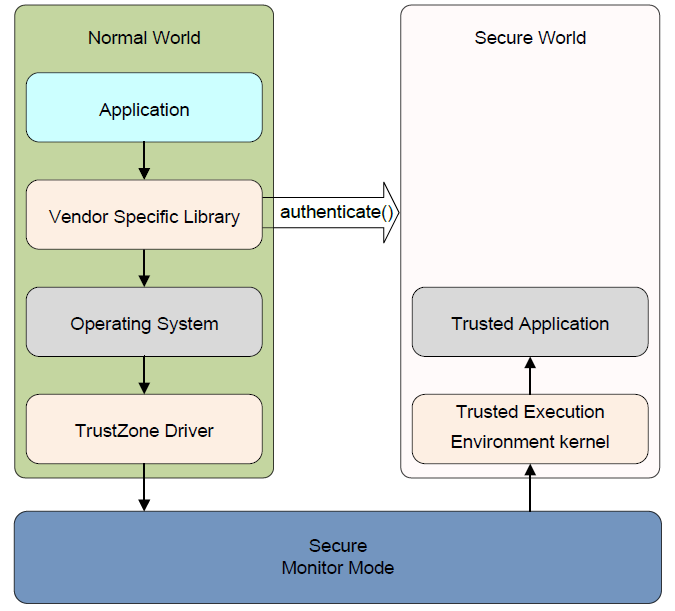

在软件应用中,secure和normal的interaction:

在软件切换过程中,有一个问题时,secure world的执行,可能会打断normal world的interrupt,

所以,一般要求secure world使用FIQ。

在armv7的AARCH32架构中,secure model与AARCH64是不同的,secure os执行在EL3,所以为了AARCH3和AARCH64能够保持统一,

需要secure os在secure状态下,和non-secure状态下的TTBR1_EL1不同,

arm trustzone的更多相关文章

- An Exploration of ARM TrustZone Technology

墙外通道:https://genode.org/documentation/articles/trustzone ARM TrustZone technology has been around fo ...

- ARM TrustZone白皮书部分阅读

嵌入式系统安全的一些解决方法及缺陷 外部硬件安全模块:在主SoC之外包含一个专用的硬件安全模块或可信元件,e.g. 手机的SIM卡.隔离仅限于可以从非易失性存储器运行的相对静态程序 内部硬件安全模块: ...

- ARM的体系结构与编程系列博客——ARM处理器系列介绍

ARM处理器系列介绍 现在到了3月,过年过得过于舒服了.系列博客也停更了近半月,我果然是个慢(lan)性(gui)子,那么趁着到校的第一天晚上,就写一篇博客来继续我的系列博客了!众所周知,ARM处理器 ...

- ARM Linux 内核 panic 之cache 一致性 ——Cortex-A9多核cache和TLB一致性广播

ARM Linux 内核 panic 之cache 一致性 ——Cortex-A9多核cache和TLB一致性广播 Cortex-A9的多喝CPU可以接收和执行一致性广播操作,当其使能并处于SMP模式 ...

- ARM Linux 内核 panic 之cache 一致性 ——cci-400 cache一致互联

ARM Linux 内核 panic 之cache 一致性 ——cci-400 cache一致互联 CCI-400 集合了互联和一致性功能,有 2 个 ACE slave 接口和 3 个 ACE-Li ...

- 如何在 arm 官网上找到合适的手册

http://infocenter.arm.com/help/advanced/help.jsp 在这里输入合适的版号即可 这样就可以不用去 CSDN 了 100000_0000_00_EN - AR ...

- [转帖]Marvell第二代ARM处理器ThunderX2解析

Marvell第二代ARM处理器ThunderX2解析 https://www.cnbeta.com/articles/tech/853137.htm 长久以来,服务器数据中心市场一直被x86 CPU ...

- Smart210学习记录-----中断

1. OVERVIEW OF VECTORED INTERRUPT CONTROLLER(概述向量中断控制器) 主要有4个VIC,4个TZIC还有一个很特殊的ARM PrimeCell PL192.主 ...

- STM32、Cortex-A、Cortex-R、Cortex-M、SecurCore

STM32是就是基于Cortex-M3这个核生产的CPU. arm7是arm公司推出的以V4指令集设计出来的arm核--其代表的芯片有s3c44b0 arm9是arm公司推出的以V5指令集设计出来的a ...

随机推荐

- oracle 11g/12c 密码复杂度验证设置

############################################################################### ###### 11g ###### ## ...

- SQL union介绍

UNION 操作符用于合并两个或多个 SELECT 语句的结果集 UNION 内部的 SELECT 语句必须拥有相同数量的列.列也必须拥有相似的数据类型.同时,每条 SELECT 语句中的列的顺序必须 ...

- Excel--数据透视图

原文:https://ke.qq.com/course/289406 1.数据源注意项 2. 3.选中数据源操作 任意选中数据源表格中的单元格(有值得单元格),插入数据透视表 默认数据源区域就是整个表 ...

- 对web标准化(或网站重构)知道哪些相关的知识,简述几条你知道的Web标准?

网页主要有三部分组成:结构(Structrue).表现(Presentation)和行为(Behavior).对应的网站标准也分为三方面: 1.结构化标准语言,主要包括XHTML和XML: 2.表现标 ...

- java实现消息队列的两种方式

https://blog.csdn.net/fenfenguai/article/details/79257928

- oc培训之变量课后练习

1.打印常用数据类型长度,打印2.3f,使小数点后面为4位. float i=2.3f; printf("%.4f",i); 2.打印以下图形. int i,j,k,m,n; ;i ...

- bat、sh等批处理文件(脚本文件)

批处理文件(batch file):也被称为批处理程序或脚本,可以简化日常或重复性任务.本质是无格式的文本文件,它包含一条或多条命令.(1).bat是dos下的批处理文件,在window系统上执行的文 ...

- 浅谈JS的变量提升

JS的解析机制,是JS的又一大重点知识点,在面试题中更经常出现,今天就来唠唠他们的原理.首先呢,我们在我们伟大的浏览器中,有个叫做JS解析器的东西,它专门用来读取JS,执行JS.一般情况是存在作用域就 ...

- NYOJ 92

1.深搜(会爆栈,通过开全局栈模拟递归) 爆栈代码 # include<iostream> # include<string> # include<string.h> ...

- abap中结构体嵌套结构体。

1: 结构体中嵌套结构体. *&---------------------------------------------------------------------* *& Re ...