DE10-Lite锁相环使用教程

DE10-Lite锁相环使用教程

目标:本文讲述如何在Quartus里设置和例化一个锁相环.

引言

锁相环(PLL)是一种闭环频率控制电路,用于比较压控振荡器的输入信号和输出信号之间的相位差. 负反馈回路迫使锁相环的输出信号与输入信号同相。

几乎所有的FPGA都含有用于时钟产生和分配的片内锁相环.锁相环最大的优点是能产生不同于输入时钟的输出时钟信号. 例如,完全可以使用锁相环从DE10‐LITE板上的50 MHz外部时钟在MAX10 fpga上生成100 MHz内部时钟。

本教程将演示如何使用Quartus中的IP(知识产权)核来实例化设计中的PLL,以生成不同的时钟频率。关于锁相环和Altera/Intel设计组件的更深入的讨论可以在https://www.altera.com/en_US/pdfs/literature/ug/ug_altpll.pdf查看.

生成PLL IP组件

- 打开工程.

- 在Quartus里打开IP目录窗口Tools > IP Catalog,在目录窗口的库里浏览,找到ALTPLL。

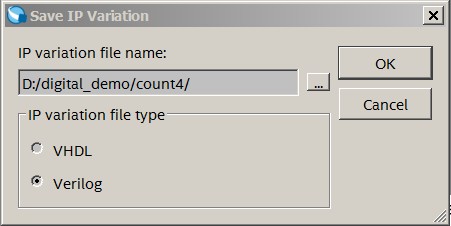

3. 双击ALTPLL。弹出的对话框询问存储IP组件的位置。通常我会建议在工程目录下建立一个IP子目录用来保存IP组件,这里指定保存路径,并以pll命名这个IP组件。

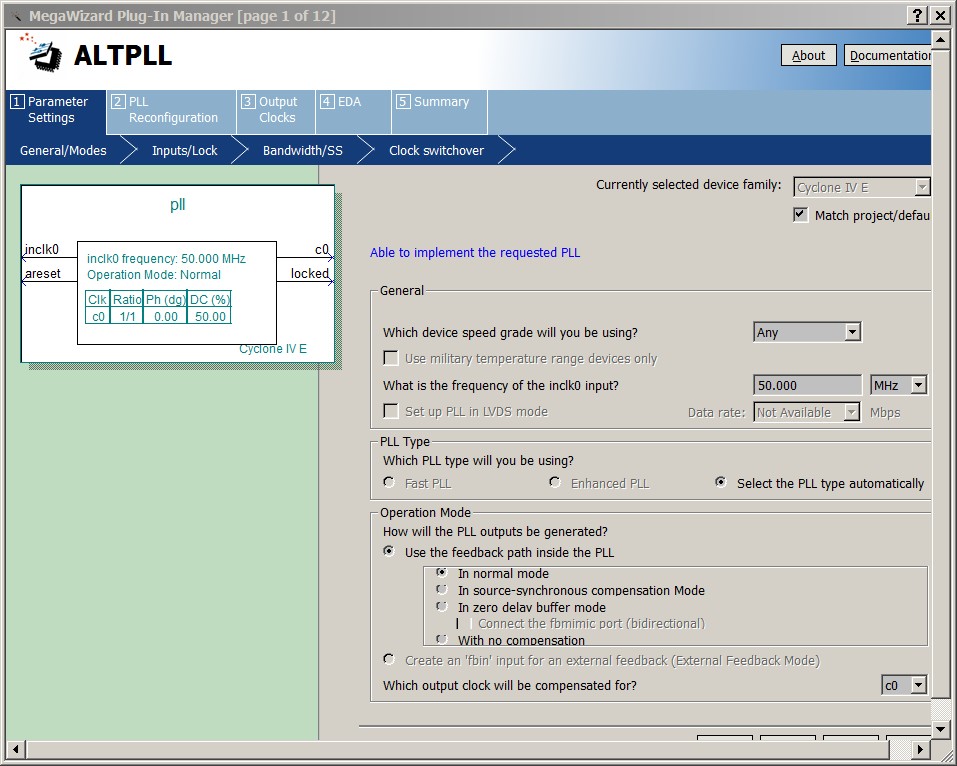

4. 单击OK。出现插件功能管理器窗口。为了匹配DE10-Lite上的外部时钟,把输入时钟inclk0的频率改为50MHz。

5. 单击Next。删除areset和locked,这里我们一般不需要这两个信号。

6. 一路单击Next直到设置时钟c0窗口。这里把c0的频率设为100MHz,Quartus将尽力生成这个频率的时钟信号。

7. 如果你需要更多的时钟信号,同样可以很容易的添加设置c1-c4。如果不需要,就一路单击Next,直到最后一个窗口。勾选例化模板项。这样在顶层设计里例化pll模块时将会很方便。然后单击Finish。

8. 会弹出对话框,询问你是否要把刚生成的pll组件添加到工程里,这里选Yes。

9. 在工程管理窗口的文件页,你会发现pll.qip文件。这样说明已经成功地生成PLL IP组件。

使用生成的IP组件

现在,我们将要在顶层模块里例化之前生成的PLL IP组件。

1. 打开存储PLL组件的目录,会发现pll_inst.v例化模板文件。

2. 打开pll_inst.v文件,把例化模板复制到剪切板。

3. 在顶层模块里(需要例化的地方)粘贴复制的例化模板,然后修改匹配端口名。必须注意输入/出的时钟信号要和实验板上的时钟名,电路里使用的时钟名匹配。比如输入时钟用MAX10_CLK1_50 或 MAX10_CLK2_50,输出时钟用clk(你顶层代码里的时钟信号的名称)。

4. 完成。

修改PLL IP组件

如果需要修改PLL组件,不用重复上面的步骤去生成一个新的组件,只需要在工程管理窗口打开IP Components页。双击要修改的IP组件,就会打开设置窗口,更改即可。

References:

- Tutorial: Instantiating and Using a PLL on the DE10‐LITE

https://www.ece.ucdavis.edu/~bbaas/180/tutorials/using.a.PLL.pdf

Written by YongfengXie

2022/05/26 Written

DE10-Lite锁相环使用教程的更多相关文章

- [PLL][PM]锁相环模拟相位解调

%锁相环测试 %模拟相位解调 clear close all clc fs=1000; %采样率 tend=100; t=0:1/fs:tend; t(end)=[]; fc=1; %载波频偏 fb= ...

- ‘初始化锁相环INIT_PLL()’

在XS128的SCI学习的过程中,INIT_PLL()显得很重要,初始化锁相环几乎在每个程序中都有,今天看的程序-初始化锁相环的相关代码如下: /*************************** ...

- 全数字锁相环(DPLL)的原理简介以及verilog设计代码

随着数字电路技术的发展,数字锁相环在调制解调.频率合成.FM 立体声解码.彩色副载波同步.图象处理等各个方面得到了广泛的应用.数字锁相环不仅吸收了数字电路可靠性高.体积小.价格低等优点,还解决了模拟锁 ...

- 第十四届智能车培训 PLL锁相环

什么是锁相环? PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等.PLL用于振荡器中的反馈技术. 许多电子设备要正常工作 ...

- 【iCore4 双核心板_FPGA】例程九:锁相环实验——锁相环使用

实验现象: 利用Quartus内部组件生成锁相环,用SignalTap II进行校验. 核心代码: module pll( input clk_25m, output clk_100m, output ...

- 【iCore1S 双核心板_FPGA】例程九:锁相环实验——锁相环的使用

实验现象: 利用Quartus内部组件生成锁相环,用SignalTap II进行校验. 核心代码: //--------------------Module_PLL------------------ ...

- 数字锁相环Octave仿真

clc; clear all; % 仿真数据长度 SimLens = 1000; % 载波信号 Fs = 2400; Ts = 1 / Fs; Fsig = 60; % 随机初相 Delta_Phas ...

- simulink pi的方法产生锁相环

pi方法就是比例积分方法,关于pi方法介绍参考http://www.elecfans.com/dianzichangshi/20120909287851.html 锁相环pi方法原理参考http:// ...

- 【iCore3 双核心板_FPGA】例程十:锁相环实验——锁相环使用

实验指导书及代码包下载: http://pan.baidu.com/s/1boeODjx iCore3 购买链接: https://item.taobao.com/item.htm?id=524229 ...

- 基于模k可逆计数的数字锁相环fpga实现

参考http://wenku.baidu.com/view/59420cb069dc5022aaea00bd.html 实现结构是参考的上边的实例,我用的全同步实现,实现过程中发现一些现象,做下记录. ...

随机推荐

- Python 汇总列数据到行

Python汇总Excel列数据到行(方法一) import pandas as pd # 读取Excel文件 df = pd.read_excel('C:\\Users\\liuchunlin2\\ ...

- Tableau 绘制圆环图

一.对应数据如下所示 二.打开tableau连接对应Excel数据源,将记录数字段连续拖动两次到行,显示设置按整个视图显示,标记里面设置按饼图显示 三.设置两个值按度量值平均值显示,并调整第一个图稍微 ...

- FCOSv2:原作的扩展版本,小修小改,性能高达50.4AP | IEEE T-PAMI 2020

本文是对FCOS的小修小改,最终性能达到了50.4AP,可谓相当强劲了,大家在工程上可以参考其中的改进以及提升方法 来源:晓飞的算法工程笔记 公众号 论文: FCOS: A Simple and ...

- KingbaesES数据库查看阻止vacuum的常用语句

KingbaesES数据库中遇到表膨胀,有时碰到vacuum失效的场景.最常见的原因如下. 以下测试基于有关analyze和autovacuum的默认阈值触发条件. 1.autovacuum是否运行, ...

- #期望dp#洛谷 6835 [Cnoi2020]线形生物

题目 分析 设\(f[i]\)表示由点\(i\)走到点\(i+1\)的期望步数, \(dp[i]\)表示由点1走到点\(i+1\)的期望步数, 那么\(dp\)为\(f\)的前缀和,最后答案为\(dp ...

- 一文了解网络编程之走进TCP三次握手和HTTP那些你不知道的事

受到很多引人入胜的标题党的影响,我终于决定,要起一个比他们还标题党的题目,打不过还不能加入吗,嘿嘿. 网络编程一直是我的弱项,其实归根结底还是我太懒了,一看到那个osi七层模型,TCP/IP模型还有那 ...

- C# 发布你的程序包到Nuget

1.新建一个.NET Standard 的类库项目 2.选择项目属性,在 package 栏目下填写我们的nuget包信息 3.选择我们的项目,点击"Pack" 打包 主要注意的是 ...

- Redis 19 SpringBoot集成

概述 SpringBoot 整合 Redis 是使用 SpringData 实现的. SpringData 是与 SpringBoot 齐名的顶级项目,整合了对常用数据库的模板型操作. 在 Sprin ...

- MogDB备机处于standby need-repair(WAL)状态

MogDB 备机处于 standby need-repair(WAL)状态 本文出处:https://www.modb.pro/db/402820 问题现象 Mogdb 主备环境,备机检查发现 Sta ...

- 【直播回顾】Hello HarmonyOS进阶课程第五课——原子化服务

由HDE李洋老师主讲的Hello HarmonyOS进阶系列应用篇第五课<原子化服务>, 已于6月1日晚上 19 点在HarmonyOS社群内成功举行.本节课李洋老师带领大家了解Harmo ...