【转】基于TMS320C6455的千兆以太网设计

基于TI公司最新DSP芯片TMS320C6455.设计并实现了以太网通信软硬件接口。采用TMS320C6455片内以太网接口模块EMAC/MDIO,结合片外AR8031 PHY芯片,在嵌入式操作系统DSP/BIOS架构上,运用TI官方网络开发包NDK提供的协议栈,实现了底层硬件驱动程序的编制及其协议栈接口,完成了数字信号的以太网传输。用户使用ndk网络协议站来实现的udp通信, 在DSP/BISO中启动了一个任务来实现网络通信。

1.硬件设计

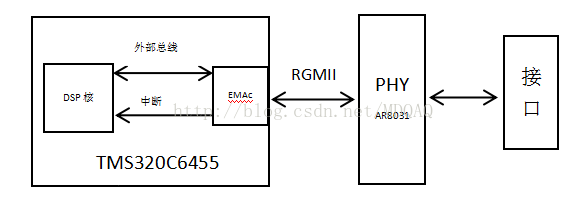

一块TMS320C6455处理器,一块AR8031 PHY芯片,和一个网络接口。C6455的EMAC接口与板上的AR8031 PHY芯片以RGMII方式连接,支持千兆双工通信模式。

整体框图:

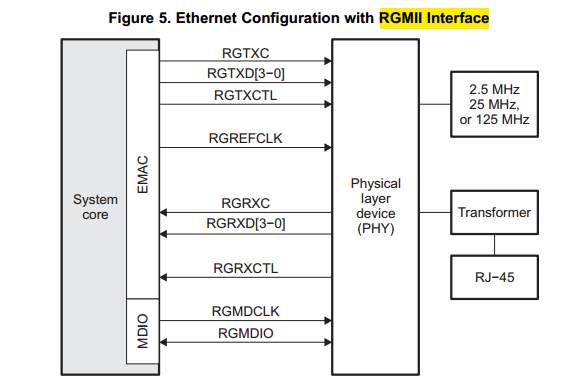

RGMII方式连接图:

2.C6455 EMAC接口介绍

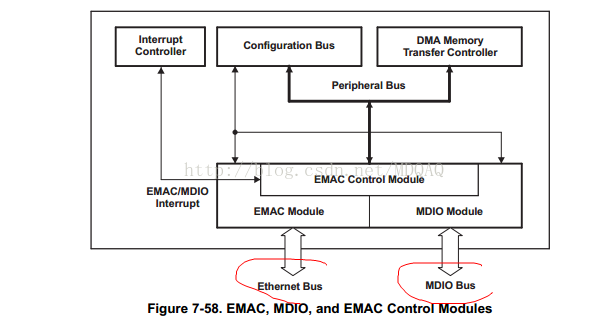

C6455的EMAC接口主要由3部分构成,包括MDIO模块、EMAC模块、EMAC控制模块。

(1)MDIO模块:通过802.3协议规定的串行通信接口,完成以太网物理层芯片的配置和管理

(2)EMAC模块:负责以太网数据包的发送和接收

(3)EMAC控制模块:作为DSP核和EMAC接口之间的桥梁,实现DSP核对EMAC模块和MDIO模块的控制

如图所示:

如上图所示,EMAC接口通过C6455提供的外设总线与DSP核连接,外设总线中的配置总线提供DSP核对EMAC寄存器的访问,数据总线完成DSP核与EMAC接口之间的以太网通信包的交换。此外,EMAC控制模块将EMAC模块和MDIO模块产生的18个中断信号综合在一起,对外提供一个中断信号,发往C6455的中断控制器,成为C6455处理器的第17号系统事件。C6455的DSP核在接到中断信号后,通过查询EMAC控制模块提供的中断状态寄存器判断中断产生的中断源。

3.以太网通信程序设计

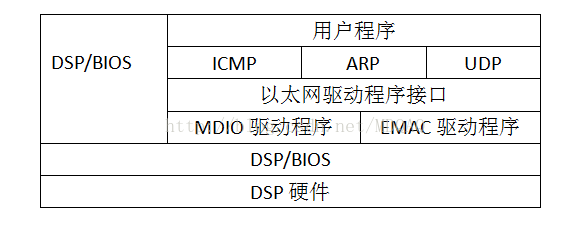

本中设计的以太网通信程序是基于TI公司提供的DSP操作系统DSP/BIOS之上,由该操作系统提供时钟定时、任务同步、硬件中断管理等功能。

上图所示,以太网通信程序主要由DSP/BIOS操作系统、网络驱动程序和用户程序构成。

(1)DSP/BIOS操作系统:为其他模块提供定时、任务同步等服务

(2)网络驱动程序:完成以太网通信功能 主要包括以太网硬件驱动程序(MDIO驱动程序与EMAC驱动程序)和几个基本的网络协议(ICMP,ARP和UDP协议)

(3)用户程序:负责解释并执行人机界面发送的命令和数据

备注:MDIO驱动程序完成C6455 EMAC与物理芯片的交互,而EMAC驱动程序为用户程序提供了以太网通信接口。

4.MDIO驱动模块的设计

MDIO模块主要负责搜索、配置和监控外部以太网物理收发芯片。该模块主要包括如下几个部分:MDIO硬件初始化;PHY芯片搜索和配置;PHY芯片状态监控。

(1)MDIO硬件初始化

1. 读取C6455设备状态寄存器(DEVSTFAT)中的MACSEL位,确定EMAC与PHY芯片之间的连接方式。文中所涉及的信号处理板上的C6455 EMAC与PHY芯片之间采用RGMII方式连接。

2. 初始化MDIO状态机,将状态机置为初始化状态。

3. 配置MDIO访问PHY芯片的时钟并使能MDIO模块。

(2)PHY芯片搜索和配置

由于PHY芯片的搜索过程并无确定的时间,因此PHY芯片搜索和配置的实现采用状态机来实现,该状态机每隔100 ms根据查询到的PHY芯片的状态完成相应的操作并更新到下一状态。PHY芯片的搜索经过芯片复位,通信速率自协商等过程,最终与通信对端建立以太网物理层连接。

(3)PHY芯片状态监控

在以太网物理层链路的建立后,有可能由于用户拔出网线、对端机器改变通信接口速率等情况而导致链路状态改变,因此MDIO模块需要每隔一段时间对网络进行监控。文中设计的状态监控模块由DSP/BIOS操作系统每隔100 ms查询一次网络状态,状态监控程序一旦发现链路状态有所变化,则根据引起链路变化的不同原因,进入相应的处理流程。

5.EMAC驱动模块的设计

EMAC驱动模块主要负责以太网数据包的接收和发送,它是以太网驱动程序的主要组成部分。该模块主要包括:EMAC硬件初始化;EMAC接收模块;EMAC发送模块。

(1)EMAC硬件初始化

EMAC硬件初始化主要的目的是将EMAC模块置于就绪状态,此时EMAC已经可以接收和发送以太网数据包。初始化过程主要包括如下步骤:

1)禁止EMAC中断,复位EMAC的HDP寄存器、统计寄存器等,设置EMAC的MAC地址,挂接应用程序提供的回调函数等操作。

2)根据需求为发送模块和接收模块分配相应的包缓存描述符,并初始化接收模块的包缓存描述符,使之指向应用程序提供的数据接收存储块。文中设计的以太网驱动程序为接收模块分配了32个包缓存描述符,为发送模块分配了480个包缓存描述符,为发送和接收模块共分配了64块存储块,每个存储块大小为4 096个字节。图6是接收模块初始化完成后,接收描述符和接收存储块之间的关系。

3)配置MAC的是否为多播地址,使能以太网中断,EMAC处于就绪状态。

(2)EMAC接收模块

EMAC接收模块主要由EMAC中断来驱动。当EMAC硬件接收完一个或多个包数据时,会向DSP核发出一个接收完成中断。DSP核在接收到中断后,调用应用程序提供的接收数据回调函数处理接收到的数据,并返回给中断服务程序一个空闲的存储块,中断服务程序将该存储块重新链接到接收存储块链表,完成接收数据流程。

(3)EMAC发送模块

EMAC发送模块主要由一个发送接口函数ethSendPacket(char*Buffer,int Length)构成,用户程序通过调用该函数完成以太网数据的发送。该函数参数中,Buffer表示应用程序需要发送的数据,Length表示发送数据的长度。该函数首先将Buffer中的数据拷贝到空闲的存储块,并将该储存块加入如图7所示的WaitQueue队列中,WaitQueue队列表示等待加入EMAC发送队列(DescQueue)的存储块。ethSendPacket函数接着检查EMAC发送队列DescQueue是否有空闲的发送描述符,如果有,将WaitQueue链表中的存储块加入到DeseQueue.EMAC硬件将通过相应的描述符,将DescQueue中的数据发送出去。

当数据发送完成后,EMAC向DSP核发出一个发送完成中断。发送完成中断服务程序将发送后的存储块从DescQueue中移除并交还给应用程序,然后将使用过的发送描述符置为空闲状态,以便下次发送数据时使用。

6.ARP/ICMP/UDP网络协议模块的设计

为了与上位机完成网络通信,信号处理机还必须提供基本的网络通信协议。文中在设计时,主要提供了ARP/ICMP/UDP 3种网络协议。

(1)ARP协议:主要完成信号处理机IP地址和MAC地址的转换

(2)ICMP协议:主要完成测试信号处理机与上位机之间的网络连通性

(3)UDP协议:主要完成实际指令和数据的通信。

【转】基于TMS320C6455的千兆以太网设计的更多相关文章

- 【转】简谈基于FPGA的千兆以太网

原文地址: http://blog.chinaaet.com/luhui/p/5100052903 大家好,又到了学习时间了,学习使人快乐.今天我们来简单的聊一聊以太网,以太网在FPGA学习中属于比较 ...

- 【小梅哥FPGA进阶学习之旅】基于Altera FPGA 的DDR2+千兆以太网电路设计

DDR2电路设计 在高速大数据的应用中,高速大容量缓存是必不可少的硬件.当前在FPGA系统中使用较为广泛的高速大容量存储器有经典速度较低的单数据速率的SDRAM存储器,以及速度较高的双速率DDR.DD ...

- 【重新发布,代码开源】FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片

原创博客,转载请注明出处:[重新发布,代码开源]FPGA设计千兆以太网MAC(1)——通过MDIO接口配置与检测PHY芯片 - 没落骑士 - 博客园 https://www.cnblogs.com/m ...

- AC6102 开发板千兆以太网UDP传输实验2

AC6102 开发板千兆以太网UDP传输实验 在芯航线AC6102开发板上,设计了一路GMII接口的千兆以太网电路,通过该以太网电路,用户可以将FPGA采集或运算得到的数据传递给其他设备如PC或服务器 ...

- AC6102 开发板千兆以太网UDP传输实验

AC6102 开发板千兆以太网UDP传输实验 在芯航线AC6102开发板上,设计了一路GMII接口的千兆以太网电路,通过该以太网电路,用户可以将FPGA采集或运算得到的数据传递给其他设备如PC或服务器 ...

- 千兆以太网TCP协议的FPGA实现

转自https://blog.csdn.net/zhipao6108/article/details/82386355 千兆以太网TCP协议的FPGA实现 Lzx 2017/4/20 写在前面,这应该 ...

- 迅为IMX6开发板支持全网通4G模块丨GPS模块丨WIFI蓝牙丨千兆以太网

迅为i.MX6开发板丨迅为i.MX6Q开发板丨四核imx6开发板丨Cortec-A9开发板丨资料介绍: 特点: 处理器:Freescale Cortex-A9四核i.MX6Q主频1GHz 核心板配置: ...

- 【VS开发】千兆以太网的传输速度

千兆以太网主流标准 千兆以太网络技术早在上世纪90年代末就已成熟,其中,1995年国际标准化组织TIA/EIA颁布了1000Base-TX标准,该标准的目的是把双绞线用于千兆以太网中,其目的是在6类非 ...

- 237-基于Xilinx Kintex-7 XC7K325T 的FMC/千兆以太网/SATA/四路光纤数据转发卡

基于Xilinx Kintex-7 XC7K325T 的FMC/千兆以太网/SATA/四路光纤数据转发卡 一. 板卡概述 本板卡基于Xilinx公司的FPGAXC7K325T-2FFG900 芯片, ...

随机推荐

- python 把带小数的浮点型字符串转换为整数的解决方案

以下内容在python中完全可以接受: 将整数的字符串表示形式传递给 int 将float的字符串表示形式传递给 float 但是,如果你将float型的字符串传递给int将会得到错误. >&g ...

- 【Redis】Redis 事务

Redis 事务介绍 Redis 事务可以一次执行多个命令, 并且带有以下三个重要的保证: 批量操作在发送 EXEC 命令前被放入队列缓存. 收到 EXEC 命令后进入事务执行,事务中任意命令执行失败 ...

- js 模糊搜索

function fuzzysearch (needle, haystack) { var hlen = haystack.length; var nlen = needle.length; if ( ...

- wamp64显示黄色图标不能忍

哎,昨天硬盘合区了下,重新安装了wamp64,删库的时候忘记备份数据库,灾难啊,只能自己重新建库建表了,深刻的教训啊. 然后还启动后是黄色图标,不能忍啊,发现wamp64需要启动三个服务,mysql, ...

- express 413 Request Entity Too Large解决办法

1.配置nginx 原因是请求实体太长了.一般出现种情况是Post请求时Body内容Post的数据太大了 如上传大文件过大; 如POST数据比较多 处理方法修改nginx.conf的值就可以解决了. ...

- 第07组 Beta冲刺(2/4)

队名:秃头小队 组长博客 作业博客 组长徐俊杰 过去两天完成的任务:学习了很多东西 Github签入记录 接下来的计划:继续学习 还剩下哪些任务:后端部分 燃尽图 遇到的困难:自己太菜了 收获和疑问: ...

- 在 Mac 系统下安装 PyCharm 的方法

首先,进入 PyCharm 的官网,PyCharm: Python IDE for Professional Developers by JetBrains. 如上图所示,直接点击DOWNLOAD N ...

- 基于 appium 的 UI 自动化测试

其中主要的目录和文件为: /MPTestCases ----------- 存放测试用例 /errorScreenShot ------------ 用例执行失败生成的错误截图 startTest.p ...

- [转帖]中信银行信用卡业务数据库实现国产替换,湖北银行新核心系统项目正式验收,阿里云与MongoDB达成战略合作

中信银行信用卡业务数据库实现国产替换,湖北银行新核心系统项目正式验收,阿里云与MongoDB达成战略合作 http://www.itpub.net/2019/10/31/3942/ 中信银行 gold ...

- 【C++札记】函数重载

概述 函数重载指在相同作用域中多个函数名相同,函数的形参不同. 遵循规则: 1.函数名相同 2.函数的参数,类型,个数或顺序不一样都可以构成重载. 3.函数返回值得类型不同不构成重载,编译直接报错,存 ...