FFT ip core

The FFT core provides four architecture options to offer a trade-off权衡取舍 between core size and

transform time.

• Pipelined Streaming I/O – Allows continuous data processing.

• Radix-4 Burst I/O – Loads and processes data separately, using an iterative approach. It

is smaller in size than the pipelined solution, but has a longer transform time.

• Radix-2 Burst I/O – Uses the same iterative approach as Radix-4, but the butterfly is

smaller. This means it is smaller in size than the Radix-4 solution, but the transform

time is longer.

Radix-2 Lite Burst I/O – Based on the Radix-2 architecture, this variant uses a

time-multiplexed approach to the butterfly for an even smaller core, at the cost of

longer transform time.

throughput 吞吐量

对于全精度无压缩结构,(unscaled)数据通道内任意一位有意义的整数都将被保留,在运算过程中产生的小数部分都被截断或者取整。此种结构,对于定点算法,经过多级乘法操作以后,数据位宽将加倍递增,其输出位宽为(输入位宽+log2(数据转换长度)+1)bits。

对于块浮点型,(block floating point)对于一帧数据里面的任何一数据点有相同的压缩比,这个压缩比值由块指数(Block Exponent)作为输出值显示,而且只有在FFT IP核检测到将会产生数据溢出的时候,才会进行压缩运算。

Burst I/O Architectures

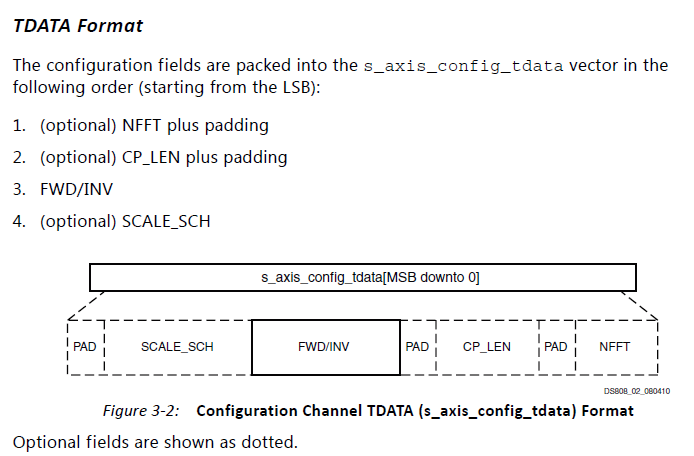

The scaling performed during successive stages can be set using the appropriate

SCALE_SCH field in the Configuration channel. For the Radix-4, Burst I/O and Radix-2

architectures, the value of the SCALE_SCH field is used as pairs of bits [... N4, N3, N2, N1,

N0], each pair representing the scaling value for the corresponding stage. Stages are

computed starting with stage 0 as the two LSBs. There are log4(point size) stages for

Radix-4 and log2(point size) stages for Radix-2. In each stage, the data can be shifted by 0,

1, 2, or 3 bits, which corresponds to SCALE_SCH values of 00, 01, 10, and 11. For example,

for Radix-4, when N = 1024, [01 10 00 11 10] translates to a right shift by 2 for stage 0, shift

by 3 for stage 1, no shift for stage 2, a shift of 2 for stage 3, and a shift of 1 for stage 4 (there

are log4(1024) = 5 Radix-4 stages). This scaling schedule scales by a total of 8 bits which

gives a scaling factor of 1/256. The conservative schedule SCALE_SCH = [10 10 10 10 11]

completely avoids overflows in the Radix-4, Burst I/O architecture. For the Radix-2, Burst I/

O and Radix-2 Lite, Burst I/O architectures, the conservative scaling schedule of [01 01 01 01

01 01 01 01 01 10] prevents overflow for N = 1024 (there are log2(1024) = 10 Radix-2

stages).

本文所采用的是定点压缩结构。(scaled)该结构相对于全精度无压缩结构,能够大大减少FPGA内部资源Xtreme DSP Slices和块RAM的使用,而相对于块浮点型,可灵活调节压缩比。定点压缩结构的压缩比例表(Scale_SCH)完全由用户自定义得到。压缩比例是按照1、2、4或者8对每一阶进行压缩,即对应于分别向右移位0、1、2或者3。如果压缩不充分,则蝶形输出结果会超出其动态范围,引起数据溢出。对于Burst I/O结构,Scale_SCH的表示方法:对于每一阶的压缩比都由指定的一个2bits的数表示,零阶的2bits数为最低位,具体形式为[N4,N3,N2,N1,N0],每一个2bits数分别对应着相应阶数的压缩比。例:对于基4结构,数据转换长度N=1024,Scale_SCH=[0110 00 1110]则表示对阶0右移位2,对阶1右移位3,对阶2右移位0,对阶3右移位2,对阶4右移位1。经验总结(可以防止产生数据溢出):对于1024点的基4,Burst I/O结构,Scale_SCH=[10 10 10 10 11];而对于1024点的基2结构,Scale_SCH=[01 01 01 01 01 01 01 01 0110]。对于流水线,Streaming I/O结构,把临近的一对基2阶组在一起,即阶0和阶1为组0,阶2和阶3为组1,等等。Scale_SCH的表示方法:对于每一组的压缩比都由指定的一个2bits的数表示,零组的2bits数为最低位,具体形式为[N4,N3,N2,N1,N0],每一个2bits数分别对应着相应组的压缩比,表示同组内的两个基2阶有相同的压缩比。例:数据长度N=1024,Scale_SCH=[10 10 00 01 11]表示对组0(阶0和阶1)右移位3,对组1(阶2和阶3)右移位1,对组2(阶4和阶5)没有移位,对组3(阶6和阶7)右移位2,对组4(阶8和阶9)右移位2。若变换长度N不是4的幂次方的时候,最后一组只包含一个基2阶,只能用00或者01表示。经验总结(可以防止产生数据溢出):N=512时,Scale_SCH=[01 10 10 10 11];N=1024时,Scale_SCH=[1010 10 10 11]。压缩比例Scale_SCH的位宽,对于流水线,Streaming I/O结构和基4,Burst I/O结构,为2*ceil(0.5*log2(N));对于基2,Burst I/O结构和基2Lite Burst I/O结构,为2* log2(N),其中N为转换数据长度。

FFT ip core的更多相关文章

- 在EDK里面添加ISE IP core的方法

(1)在ISE下,使用core generator,可以得到xilinx的IP的*.v和*.ngc 文件,将这两个文件拷贝出来: (2)在EDK下使用“Create or Import Periphe ...

- 使用xilinx ip core FIFO First- World First-Through (FWFT)模式的注意事项

也许很多人知道xilinx ip core 中的fifo可以配成standard 模式和FWFT模式,并知道两者的区别是:standard模式下,当rd为高时,fifo会延时一个时钟输出数据(时序逻辑 ...

- Quartus FFT IP核简介

为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide. ...

- Modelsim独立仿真Vivado Clocking Wizard IP Core

工欲善其事,必先利其器.在使用Vivado自带的仿真软件仿真的时候,相对于更优秀的仿真工具Modelsim,效率低了很多,为了更高效的开发,我尝试着用Vivado级联Modelsim仿真,但是级联后还 ...

- 从Xilinx FFT IP核到OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109.关于 ...

- IP Core 分类

IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的.具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中.到了SOC阶段,IP核 ...

- Xilinx FFT IP v9.0 使用(一)

reference:https://blog.csdn.net/shichaog/article/details/51189711 https://blog.csdn.net/qq_36375505/ ...

- 阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide

阅读 RAM-Based Shift Register(ALTSHIFT_TAPS) IP Core User Guide 说明:本文档自带测试工程: DE_ALTSHIFT_TAPS.zip 1.支 ...

- 实测—fft IP核使用(包括ifft的配置使用)

Vivado xilinx fft9.0 使用笔记: ****注 仿真实测1024点的转换需要经过1148个时钟周期才能得到转换结果: 模块配置信号含义请参考pg109文档手册(写的贼烂会看晕),不详 ...

随机推荐

- 关于ELK

官方文档:https://www.elastic.co/guide/en/elasticsearch/reference/6.0/getting-started.html 日志: https://ww ...

- ASP 基础二 内置对象

一 Request 二 Response 三 Application 四 Session 五 Server <script language="vbscript" runat ...

- Android学习之基础知识九—数据存储(持久化技术)

数据持久化是将那些内存中的瞬时数据保存到存储设备,保证即使在手机或电脑关机的情况下,这些数据仍然不会丢失. Android系统中主要提供了3种方式用于简单地实现数据持久化功能:文件存储.SharedP ...

- wifidog源码分析 - wifidog原理

wifidog是一个用于配合认证服务器实现无线网页认证功能的程序,常见的情景就是使用于公共场合的无线wifi接入点,首先移动设备会连接公共wifi接入点,之后会弹出网页要求输入用户名密码,认证过后才能 ...

- Identity(三)

本文摘自木宛城主的 ASP.NET MVC 随想录——开始使用ASP.NET Identity,初级篇 - 木宛城主 - 博客园 由于ASP.NET Membership.ASP.NET Simple ...

- 从harbor部署到在k8s中使用

一.概述 harbor是什么呢?英文单词的意思是:港湾.港湾用来存放集装箱(货物的),而docker的由来正是借鉴了集装箱的原理,所以harbor是用于存放docker的镜像,作为镜像仓库使用.官方的 ...

- python3 编程使用技巧

from random import randint data = {"Student{}".format(i):randint(60,100) for i in range(1, ...

- VM下设置CenOS为静态IP

在本机利用VM启动了4台虚拟机来搭建zookeeper集群,但是每次电脑重启后,虚拟机的IP都会变化,现在想来固定每台虚拟机的IP. 1.Step1:查看网关和子网掩码 记住选用NAT模式,点击NAT ...

- RHEL7基本命令

Terminal TTY TTY是TeleTYpe的一个老缩写. Teletypes,或者teletypewriters,原来指的是电传打字机,是通过串行线用打印机键盘通过阅读和发送信息的东西,和古老 ...

- cp 命令有坑

cp 是个很常用的命令, 基本语法为 cp -v a b 把文件a 复制为文件b(-v为显示做了什么,这是非常安全的做法,建议新手添加此参数) 参数说明: -a:此选项通常在复制目录时使用, ...