AMBA APB总线

前面分析了AHB总线协议。接下来分析APB总线协议。

(一) APB总线接口:

PCLK APB总线时钟。

PRESETn APB总线复位。低有效。

PADDR 地址总线。

PSELx 从设备选择。

PENABLE APB传输选通。

PWRITE 高为写传输,低为读。

PRDATA 读数据总线。

PWDATA 写数据总线。

接口信号定义如下:

interface apb_slv_intf #(

parameter AW = ,

DW =

) (

input logic PCLK,

input logic PRESETn

);

logic PSEL;

logic PENABLE;

logic [AW-:] PADDR;

logic PWRITE;

logic [DW-:] PWDATA; logic [DW-:] PRDATA; modport m (

input PRDATA,

output PSEL, PENABLE, PADDR, PWRITE, PWDATA

); modport s (

input PSEL, PENABLE, PADDR, PWRITE, PWDATA,

output PRDATA

); endinterface: apb_slv_intf

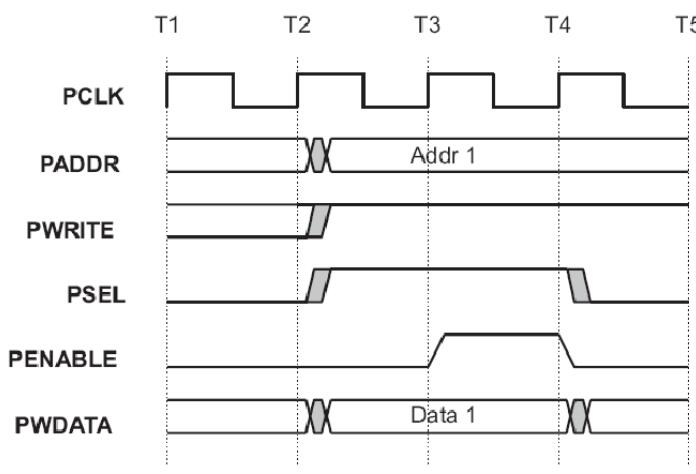

(二) APB总线时序图:

写传输

读传输

注意在PENABLE信号有效后从设备需要给出有效数据/读取有效数据。

(三) AHB总线到APB总线转换桥

module ahb2apb_bridge #(

parameter AHB_AW = ,

AHB_DW = ,

APB_AW = ,

APB_DW = ,

NSLV =

) (

input logic HCLK,

input logic HRESETn,

input logic PCLK,

input logic PRESETn,

ahb_slv_intf.s ahb,

apb_slv_intf.m apbv[NSLV]

); logic ahb_work;

logic apb_work; genvar i; typedef enum logic [:] {

AHB_IDLE = 'b00,

AHB_WRITE = 'b01,

AHB_READ = 'b10,

AHB_WAIT = 'b11

} ahb_state_e; // Signal of AHB Domain

struct {

logic work;

logic [AHB_AW-:] addr;

logic [AHB_DW-:] data;

logic write;

ahb_state_e cstate, nstate;

} ahbd; typedef enum logic [:] {

APB_IDLE = 'b00,

APB_WRITE = 'b01,

APB_READ = 'b10

} apb_state_e; // Signal of APB Domain

struct {

logic work;

logic [APB_DW-:] data[NSLV];

logic PSEL[NSLV];

logic PENABLE[NSLV];

apb_state_e cstate, nstate;

} apbd; // AHB Control Logic

always_comb begin

case (ahbd.cstate)

AHB_IDLE: begin

if (ahb.HSEL && ahb.HTRANS == HTRANS_NONSEQ) begin

if (ahb.HWRITE)

ahbd.nstate = AHB_WRITE;

else

ahbd.nstate = AHB_READ;

end

else

ahbd.nstate = AHB_IDLE;

end

AHB_WRITE: begin

if (apbd.work)

ahbd.nstate = AHB_WAIT;

else

ahbd.nstate = AHB_WRITE;

end

AHB_READ: begin

if (apbd.work)

ahbd.nstate = AHB_WAIT;

else

ahbd.nstate = AHB_READ;

end

AHB_WAIT: begin

if (!apbd.work)

ahbd.nstate = AHB_IDLE;

else

ahbd.nstate = AHB_WAIT;

end

default: ahbd.nstate = AHB_IDLE;

endcase

end always_ff @(posedge HCLK or negedge HRESETn) begin

if (!HRESETn)

ahbd.cstate <= AHB_IDLE;

else

ahbd.cstate <= ahbd.nstate;

end always_ff @(posedge HCLK or negedge HRESETn) begin

if (!HRESETn) begin

ahbd.work <= 'b0;

ahbd.addr <= '0;

ahbd.data <= '0;

ahbd.write <= 'b0;

ahb.HREADY <= 'b1;

ahb.HRDATA[APB_DW-:] <= '0;

end

else begin

case (ahbd.cstate)

AHB_IDLE: begin

if (ahb.HSEL && ahb.HTRANS == HTRANS_NONSEQ) begin

ahbd.addr <= ahb.HADDR;

ahbd.write <= ahb.HWRITE;

ahb.HREADY <= 'b0;

end

else begin

ahbd.addr <= '0;

ahbd.write <= 'b0;

ahb.HREADY <= 'b1;

end

ahbd.work <= 'b0;

ahbd.data <= '0;

ahb.HRDATA[APB_DW-:] <= apbd.data[ahbd.addr[AHB_AW-:AHB_AW-]];

end

AHB_WRITE: begin

ahb.HREADY <= 'b0;

ahbd.work <= 'b1;

ahbd.data <= ahb.HWDATA;

ahb.HRDATA[APB_DW-:] <= '0;

end

AHB_READ: begin

ahbd.work <= 'b1;

ahbd.data <= '0;

ahb.HREADY <= 'b0;

ahb.HRDATA[APB_DW-:] <= '0;

end

AHB_WAIT: begin

ahbd.work <= 'b0;

ahb.HREADY <= 'b0;

ahb.HRDATA[APB_DW-:] <= '0;

end

endcase

end

end assign ahb.HRESP = HRESP_OKAY;

// assign ahb.HRDATA[AHB_DW-1:APB_DW] = '0; // APB Control Logic

always_comb begin

case (apbd.cstate)

APB_IDLE: begin

if (ahbd.work) begin

if (ahbd.write)

apbd.nstate = APB_WRITE;

else

apbd.nstate = APB_READ;

end

else

apbd.nstate = APB_IDLE;

end

APB_WRITE: apbd.nstate = APB_IDLE;

APB_READ: apbd.nstate = APB_IDLE;

default: apbd.nstate = APB_IDLE;

endcase

end always_ff @(posedge PCLK or negedge PRESETn) begin

if (!PRESETn)

apbd.cstate <= APB_IDLE;

else

apbd.cstate <= apbd.nstate;

end always_ff @(posedge PCLK or negedge PRESETn) begin

if (!PRESETn) begin

apbd.work <= 'b0;

for (int j = ; j < NSLV; j++) begin

apbd.PSEL[j] <= 'b0;

apbd.PENABLE[j] <= 'b0;

end

end

else begin

case (apbd.cstate)

APB_IDLE: begin

if (ahbd.work) begin

apbd.work <= 'b1;

for (int j = ; j < NSLV; j++)

apbd.PSEL[j] <= (ahbd.addr[AHB_AW-:AHB_AW-] == j) ? 'b1 : 1'b0;

end

else begin

apbd.work <= 'b0;

for (int j = ; j < NSLV; j++)

apbd.PSEL[j] <= 'b0;

end

for (int j = ; j < NSLV; j++)

apbd.PENABLE[j] <= 'b0;

end

APB_WRITE: begin

apbd.work <= 'b1;

for (int j = ; j < NSLV; j++)

apbd.PENABLE[j] <= (ahbd.addr[AHB_AW-:AHB_AW-] == j) ? 'b1 : 1'b0;

end

APB_READ: begin

apbd.work <= 'b1;

for (int j = ; j < NSLV; j++)

apbd.PENABLE[j] <= (ahbd.addr[AHB_AW-:AHB_AW-] == j) ? 'b1 : 1'b0;

end

endcase

end

end generate

for (i = ; i < NSLV; i++) begin: apbv_loop

assign apbv[i].PADDR = {'h0, ahbd.addr[APB_AW-4-1:0]};

assign apbv[i].PWRITE = ahbd.write;

assign apbv[i].PWDATA = ahbd.data[APB_DW-:];

assign apbd.data[i] = apbv[i].PRDATA;

assign apbv[i].PSEL = apbd.PSEL[i];

assign apbv[i].PENABLE = apbd.PENABLE[i];

end

endgenerate endmodule: ahb2apb_bridge

AMBA APB总线的更多相关文章

- AHB总线和APB总线

AHB主要用于高性能模块(如CPU.DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作:非三态的实现方式:支持突发传输:支持分段传输:支持多个主控制器:可配置 ...

- APB总线

APB(Advance Peripheral Bus)是AMBA总线的一部分,从1998年第一版至今共有3个版本. AMBA 2 APB Specfication:定义最基本的信号interface, ...

- AMBA AHB总线

Advanced Microcontroller Bus Architecture, 即AMBA,是ARM公司提出的总线规范,被很多SoC设计所采用,常用的实现有AHB(Advanced High-P ...

- STM32WB AHB总线、APB总线与外设

方框图: 如图所示: 1)APB1外设 2)APB2外设 3)AHB1外设 4)AHB2外设 5)AHB3外设 6)AHB4外设(ABH共享总线外设) 内存映射关系图:

- AMBA总线介绍

The Advanced Microcontroller Bus Architecture (AMBA) specification defines an on- chip communication ...

- APB协议

https://wenku.baidu.com/view/2663f629ef06eff9aef8941ea76e58fafab04592.html https://www.cnblogs.com/l ...

- AMBA总线协议AHB、APB

一.什么是AMBA总线 AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus).ASB (Advanced ...

- AMBA总线协议AHB、APB、AXI对比分析【转】

转自:https://blog.csdn.net/ivy_reny/article/details/56274412 一.AMBA概述 AMBA (Advanced Microcontrolle ...

- [转]AMBA、AHB、APB、ASB总线简介

[转]http://www.cnblogs.com/zhaozhong1989/articles/3092140.html 1.前言 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大.数字IC ...

随机推荐

- html5手机 input file 上传图片 调用API

<input type="file" accept="video/*;capture=camcorder"> <input type=&quo ...

- 5个php实例,细致说明传值与传引用的区别

传值:是把实参的值赋值给行参 ,那么对行参的修改,不会影响实参的值 传引用 :真正的以地址的方式传递参数传递以后,行参和实参都是同一个对象,只是他们名字不同而已对行参的修改将影响实参的值 说明: 传值 ...

- 【python】time和datetime的strptime不是线程安全的!

来源:http://blog.csdn.net/kevin6216/article/details/9021039 在多线程中用strptime需要加锁!!!

- laravel 集合

最近一直在用laravel框架,比较喜欢laravel的ORM(通常我们理解的Model)...但是默认情况下,Eloquent 查询的结果总是返回 Collection 实例...所有不得不了解co ...

- laravel 接口跨域

最方便的方法,新建一个middleWare,把这个middleware加入到全局中间件,所有的请求,都会经过这个中间件的过滤. php artisan make:middleware CrossHtt ...

- 性能测试二十一:环境部署之mysql

在正常工作中,mysql应该部署到 一台独立的服务器上,不与tomcat共用服务器,由于成本原因,现部署到一起 为避免出错引起麻烦,先备份: 一:环境清理:先卸载系统自带的mysql 停止mysql: ...

- %SystemRoot%

%SystemRoot%即C:\windows

- 步步为营-58-SQLite的使用

说明:文档型关系数据库,多用于移动端 1.1 添加引用 ` 1.1.1 System.Data.SQLite.xml 1.1.2 System.Data.SQLite.dll 1.2 连接字符串的设置 ...

- Kubernetes学习系列

这段时间项目组内想要引入Kubernetes,作为第二代容器调度引擎,故最近在系统的学习Kubernetes.整理了一些学习笔记,心得,放到博客中,一来记录自己的学习经过,二来看能否帮到有需要的同学. ...

- Android-认识Bitmap

Android-认识Bitmap 学习自 Android开发艺术探索 例行废话 在Android的各种APP中都被离不开各种各样的图片,有的图片很大,有的图片很小不管这样图片都是一种很吃内存的资源,而 ...