uvm设计分析——tlm

tlm模块,用来在不同模块之间实现实时通信,主要基于两个定义在通信双方的port类来实现。

两个port之间,通过connect函数,来拿到双方的class指针,进而调用对方的function。

但是uvm规定,控制流(调用function与被调用方)只能按一定的方向来执行,所以只有某一类port类可以调对应port的function。

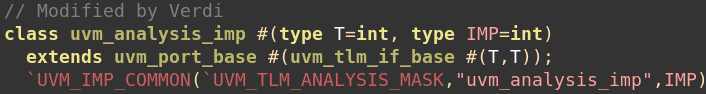

由于imp所在的class中,每次通信可能实现的function不同,而且做virtual function的重载也会引入新的class,

所以imp中的port类,在定义时,就调用parent中对应的function,这样在parent的class中就必须实现相应的function。

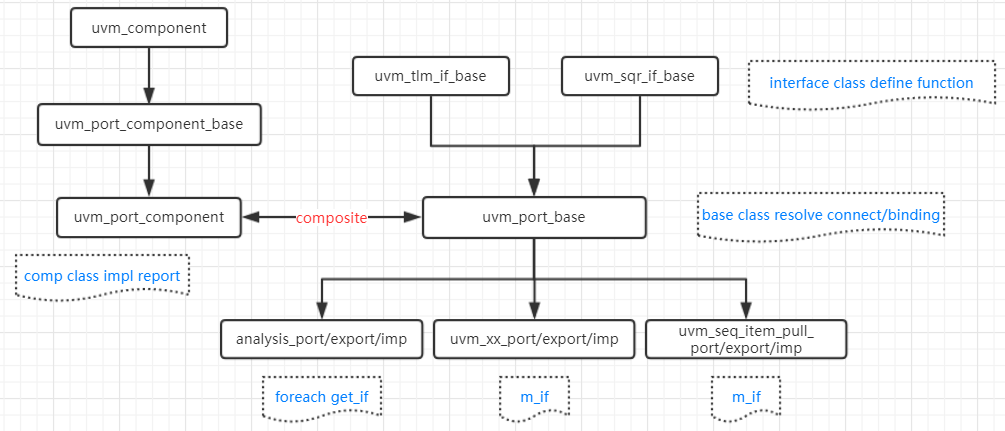

tlm模块的类图:

interface class,实现put,get,write,transparent等方法定义,

有两种,tlm_if_base,用在general的object或component class中,

sqr_if_base,用在driver和sequencer class中,

port_component,是基于uvm_component的extend,主要为了方便调用report机制,

port_base,定义connect,binding等function,实现内部provider,provided对象queue的初始化,

port_base与port_component class中互有对方的指针变量,可以实现对方的function,

但是在应用过程中,port_component只是提供了report的访问。

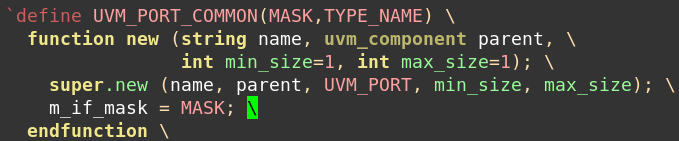

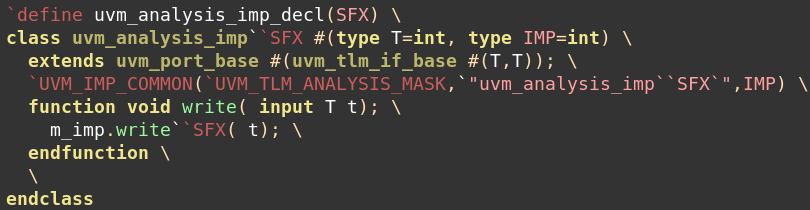

port/export/imp class,是实际应用中的class,都是通过macros来进行实现的。

其中只定义了该port对应的function和一个new函数。

从实现中的连接方式来看,port,export只是命令的传递者,imp是命令的执行者,其中实现了具体的function---调用parent相应的function。

所以,port,export可以被定义很多层级,来方便传递,都不影响最终的执行。

代码中表现为,port调用自己provider的put等函数,即export的provider的put等函数,即imp中调用的parent的put函数。

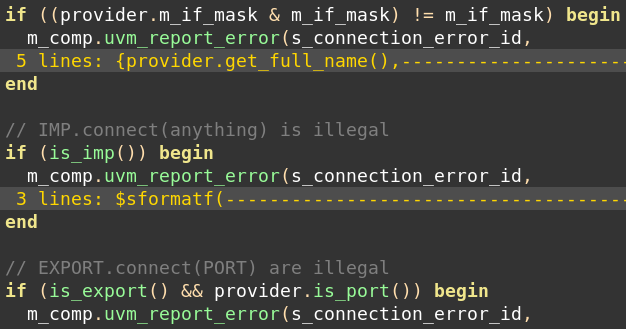

uvm还规定了自己的连接规则,定义在port_base connect和check_relation function中。每次进行connect函数调用的时候,都会检查。

error类型,1) mask_if不同,用来区分不同的port组;

2) 发起connect的是imp;

3) export连接port;

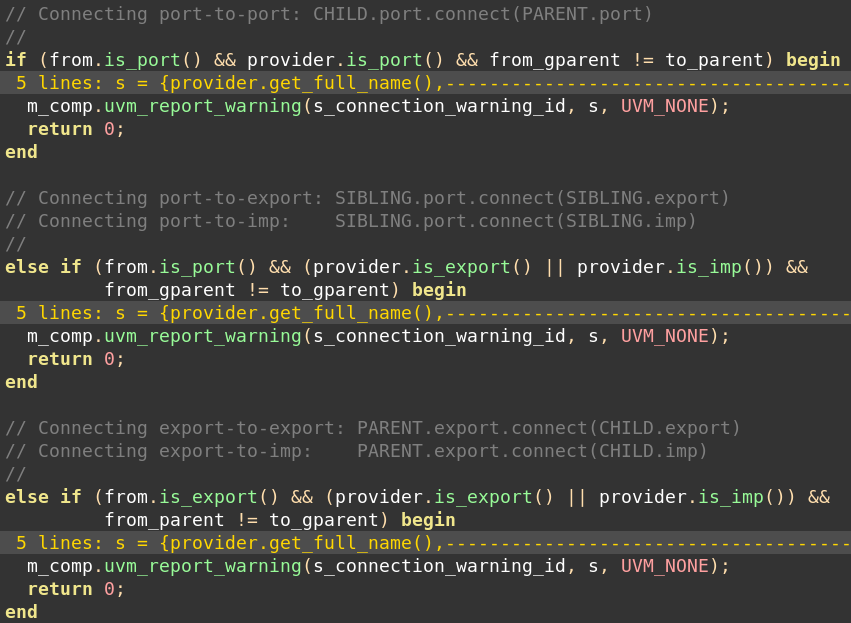

warning类型,1)port可以连接port,必须是child port连接parent的port;

2)port连接export,imp,必须是同一hierarchy;

3)export连接export,imp,必须是parent export,连接child export,imp;

analysis port并没有这些warning的要求。

从通信方式看,analysis类表示广播,可以connect多个,实现过程中,遍历各个port、export queue中的imp;

实现的是无延时的function write;

其他包括sqr_if都是一对一的,只能connect一个,

实现中,在每个port class的new函数中,都规定了该port能够连接的最小和最大的export,imp,

analysis [0:$],其他的port,只能是1。在resolve_binding的时候,会进行该size的检查。

从操作行为看,定义的port的function:try_put,can_put,try_get,can_get,try_peek,can_peek,nb_transport,write,

定义的port的task:put, get, peek,transport, (imp中固定function 实现bridge,具体实现与parent class)

sqr_if port中定义的function:item_done,has_do_available,put_response,

定义的task:get_next_item,try_next_item,wait_for_sequences,get,put,peek,

(实现于sequencer,调用于driver)

port_base中的三个重要函数:

1)connect函数,需要显式调用,必须在end_of_elaboration phase结束之前完成,之后调用会报错。

2)resolve_binding函数,由uvm_root 在 end_of_elaboration phase开始隐式递归调用,所有component中的child都会做检查。

3)get_if函数,在put,write等函数中被调用,拿到imp_list中的provider的指针,

port_base中的三个重要变量:

1)this_type m_provided_by[string]

this_type m_provided_to[string],存放provider和provided的port_base对象类型,在connect函数被赋值;

2)this_type m_imp_list[string],在resolve_binding函数中,被更新,存放对应provided的对象的类型;

如果provider的size很多,或遍历之后,都放在imp_list中。

3)this_type m_if,指向第一个m_imp_list中的port类型的对象,

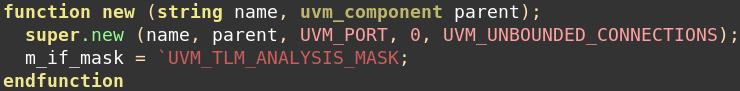

各个port class中的size, min,max,mask_if等配置在new的时候,直接初始化。

analysis min为0,max无限制,

其他port,min为1,max为1,

多个export调用同一个imp时的function重名问题,uvm的解决方法是重新define多个不同的class对象的imp,分别调用各自的不同名称的function;

使用时,需要先define,也就是定义一个新的class,之后进行正常的connect,在imp调用的时候,会调用write_suffix这样的function;

从而区分不同的export对应的imp实现。

这样的imp定义,需要根据mask_if来定义各自的class,因为new的时候,MASK define仍然是和正常的imp相对应的。

export并不需要担心重名的问题,因为它的function并没有具体的时候,只是进行imp_list中的遍历调用,所以function内容都一样。

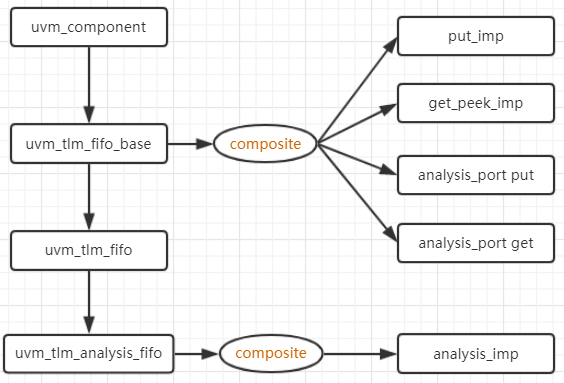

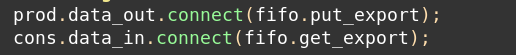

fifo部分,只是将多个port类型和一个mailbox封装在一起,中间保存,传递trans。

tlm_fifo_base中,定义了两个analysis_port,负责将trans,广播出去;

两个imp,分别实现,get,put,等等全部的interface function接口;

tlm_fifo中,定义了mailbox,可以在fifo new的时候,显式指定fifo的深度;默认1

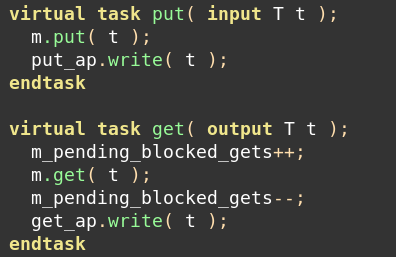

具体实现put,get等函数;(实现并不像parent中的那样具体);单纯写入mailbox,再用analysis port写出去;

tlm_analysis_fifo中,只是增加了一个analysis_imp,然后实现try_put;

tlm_fifo中的function,put操作,mailbox,put操作,然后通过put_ap的analysis再发出去;

get操作,mailbox,get操作,然后通过get_ap的analysis再发出去;

tlm_analysis_fifo中的function,只增加write函数;

tlm_fifo中的mailbox function:size,is_empty,is_full,used,flush,单纯的mailbox function;

tlm1中的绝大多数port,只支持一个参数,只有req或者rsp,不会同时有这两个。

但是transport或者master/slave类型的port,支持req和rsp的同时存在。

tlm_fifo,也只是支持一种req的mailbox的存在,

req_rsp_channel,支持req和rsp的同时存在,因为其中定义了两个mailbox,

在实际使用中,声明,port,export的声明,需要指定一种req,作为参数;

imp的声明,需要指定一种req参数,还必须将parent的type 也传进来;

new函数,port、export需要指定parent,需要solve_binding;

imp需要指定parent,因为需要调用parent的function;

connect函数,需要在各个port都例化之后,在进行连接,因为port中的imp_list需要的是一个object;

所以,目前connect函数,都被放在connect phase;

uvm设计分析——tlm的更多相关文章

- uvm设计分析——reg

项目中的reg_model一般只有一份,set到reg_sequence上,所以多个sequence并行启动结束的时候,reg model会成为一个共享资源. uvm_reg_field中的volat ...

- uvm设计分析——factory

uvm的factory机制,通过实例一个static类型default factory,并且通过宏将所有例化extend出来的object,component register到该factory的内部 ...

- uvm设计分析——field automation

uvm中的field_automation主要实现了class中的基础元素的copy,compare等函数, 实现方式分为两种:1)用户注册,field系列宏:uvm内部调用static status ...

- uvm设计分析——callback

uvm_callback,设计者在进行class的function设计时,有意留下的一些hook,总是遍历某个pool中的对象: 使用者在使用时,将实现添加到某个pool中: callback中,最重 ...

- uvm设计分析——report

uvm_report实现中的类图,如下: 1)uvm_component均从uvm_report_object extend而来,其中定义了report_warning,error,info,fata ...

- Guidelines for Successful SoC Verification in OVM/UVM

By Moataz El-Metwally, Mentor Graphics Cairo Egypt Abstract : With the increasing adoption of OVM/UV ...

- UVM的类库

[转]http://www.asicdv.com/ 一个UVM验证平台可以看成由多个模块组合在一起的,这和以前的verilog代码,以及verilog结合其它各种语言的验证手段在理念上是一样的,最大的 ...

- UVM中的class

UVM中的类包括:基类(base)------------uvm_void/uvm_object/uvm_transaction/uvm_root/uvm_phase/uvm_port_base 报告 ...

- (转)UVM内容梗概

1. 类: 面向对象基础传统的面向对象编程与systemverilog类的特点,类的定义,成员与方法,构造函数,对象的复制和深/浅拷贝,父类/子类关系,类的继承,作用域的规则,对象的句柄以及赋值,方法 ...

随机推荐

- SR锁存器

CRM(临界连续模式)BOOST PFC 电路控制系统 SR锁存器 S和R都等于0的时候为什么有两个不同的Q?正因为这样才叫锁存器.Q’是Q的取反,不可能相同.Q*和Q‘不一样.Q是Q*的前一个状态. ...

- charles4.2下载与破解方法以及配置https

Charles的使用方法 Charles下载地址 地址:https://www.charlesproxy.com/latest-release/download.do 2. Charles破解 破解地 ...

- LeetCode 985 Sum of Even Numbers After Queries 解题报告

题目要求 We have an array A of integers, and an array queries of queries. For the i-th query val = queri ...

- tensorflow入门笔记(一) tf.app.flags.FLAGS

tf.app.flags.DEFINE_xxx()就是添加命令行的optional argument(可选参数),而tf.app.flags.FLAGS可以从对应的命令行参数取出参数.举例如下: FL ...

- AT2046 Namori 图论

正解: 解题报告: 传送门! 首先看数据范围可以发现要么是棵树要么是个奇环要么是个偶环 然后就分类讨论分别看下这几个情况 首先是棵树的 首先可以想到树的情况就是个二分图,所以不妨把颜色重定义,让奇数层 ...

- 【python-opencv】30-角点检测

[微语]世上有很多不可能,不过不要在你未尽全力之前下结论 特征检测:找到图像特征的技术 特征描述:描述图像特征 Harris角点检测(Corner Detection) 参考: https://doc ...

- 拦截器的作用之session认证登录和资源拦截

背景: 在项目中我使用了自定义的Filter 这时候过滤了很多路径,当然对静态资源我是直接放过去的,但是,还是出现了静态资源没办法访问到springboot默认的文件夹中得文件.另外,经常需要判断当前 ...

- 【Selenium】selenium中隐藏元素如何定位?

前言 面试题:selenium 中隐藏元素如何定位?这个是很多面试官喜欢问的一个题,如果单纯的定位的话,隐藏元素和普通不隐藏元素定位没啥区别,用正常定位方法就行了 但是吧~~~很多面试官自己都搞不清楚 ...

- 【托业】【新托业TOEIC新题型真题】学习笔记5-题库二->P7

--------------------------------------单词-------------------------------------- amenity 适意:休闲设施 onsit ...

- 【雅思】【写作】【大作文】Discuss both views and give your own opinion

•Discuss both views and give your own opinion • • •Agree or disagree •Discuss both views •Report ...