实测52.4MB/s!全国产ARM+FPGA的CSI通信案例分享!

CSI总线介绍与优势

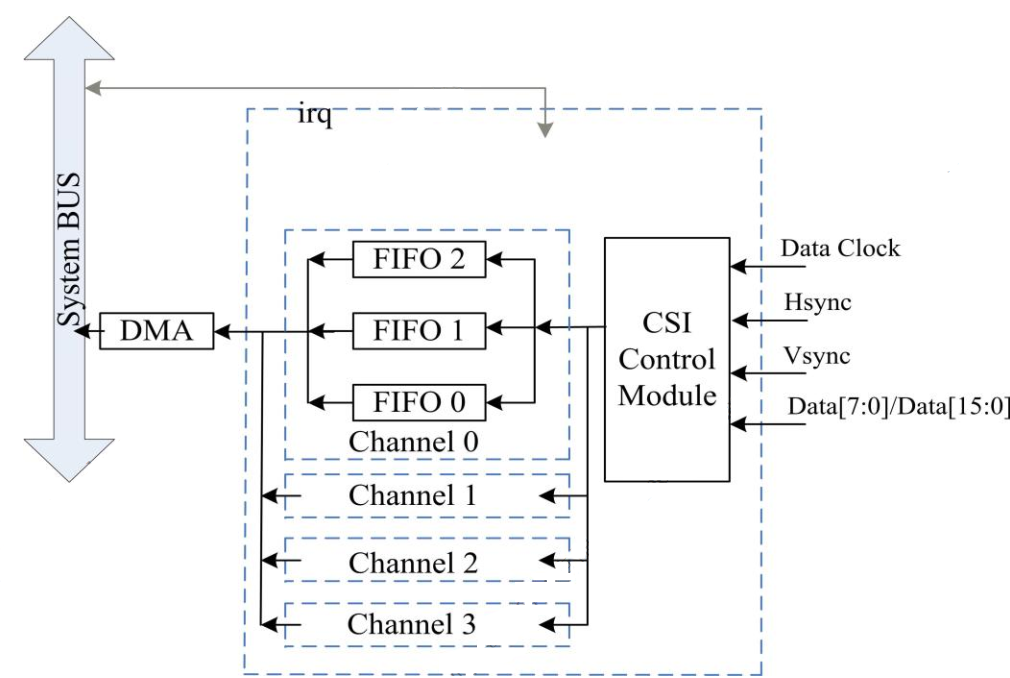

CSI(CMOS sensor parallel interfaces)总线是一种用于连接图像传感器和处理器的并行通信接口,应用于工业自动化、能源电力、智慧医疗等领域,CSI总线接口示意图如下所示(以全志科技T3处理器的CSI0为例)。

开发难度低:CSI总线采用并行数据和控制信号分离方式,时序简单,FPGA端接口开发难度低。

低成本:CSI总线采用并行传输方式,FPGA端使用资源少,对FPGA器件资源要求低。

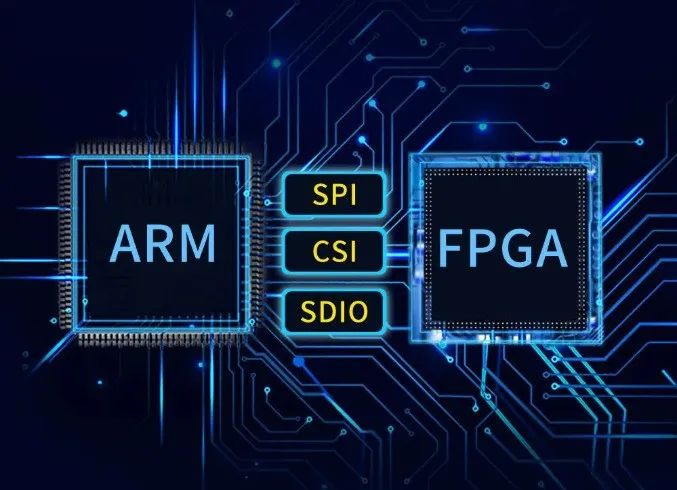

国产ARM + FPGA架构介绍与优势

近年来,随着中国新基建、中国制造2025规划的持续推进,单ARM处理器越来越难胜任工业现场的功能要求,特别是如今能源电力、工业控制、智慧医疗等行业,往往更需要ARM + FPGA架构的处理器平台来实现例如多路/高速AD采集、多路网口、多路串口、多路/高速并行DI/DO、高速数据并行处理等特定功能,因此ARM + FPGA架构处理器平台愈发受市场欢迎。

创龙科技SOM-TLT3F是一款基于全志科技T3四核ARM Cortex-A7处理器 + 紫光同创Logos PGL25G/PGL50G FPGA设计的异构多核全国产工业核心板,ARM Cortex-A7处理单元主频高达 1.2GHz。核心板ARM、FPGA、ROM、RAM、电源、晶振、连接器等所有元器件均采用国产工业级方案,国产化率100%。

全志T3为准车规级芯片,四核ARM Cortex-A7架构,主频高达1.2GHz,支持双路网口、八路UART、SATA大容量存储接口,同时支持4路显示、GPU以及1080P H.264视频硬件编解码。另外,创龙科技已在T3平台适配国产嵌入式系统翼辉SylixOS,真正实现软硬件国产化。

紫光同创Logos PGL25G/PGL50G FPGA在工业领域应用广泛,逻辑资源分别为27072/51360,与国外友商产品pin to pin兼容,主要用于多通道/高速AD采集或接口拓展。因其价格低、质量稳定、开发环境易用等优点,受到工业用户的广泛好评。

国产ARM + FPGA的CSI通信案例介绍

本章节主要介绍全志科技T3与紫光同创Logos基于CSI的ARM + FPGA通信方案,使用的硬件平台为:创龙科技TLT3F-EVM工业评估板。

为了简化描述,正文仅摘录方案功能描述与测试结果,详细开发文档请扫描文末二维码下载。

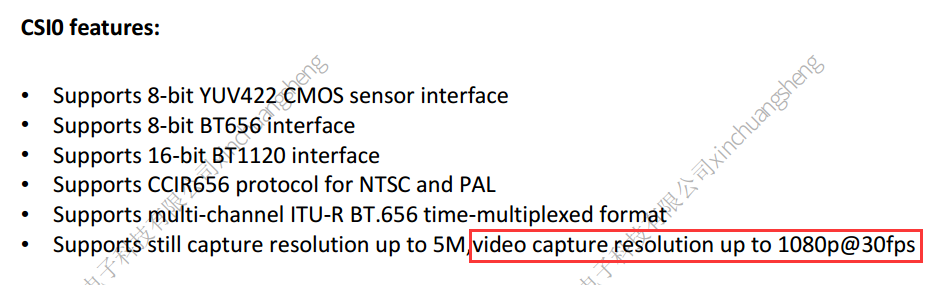

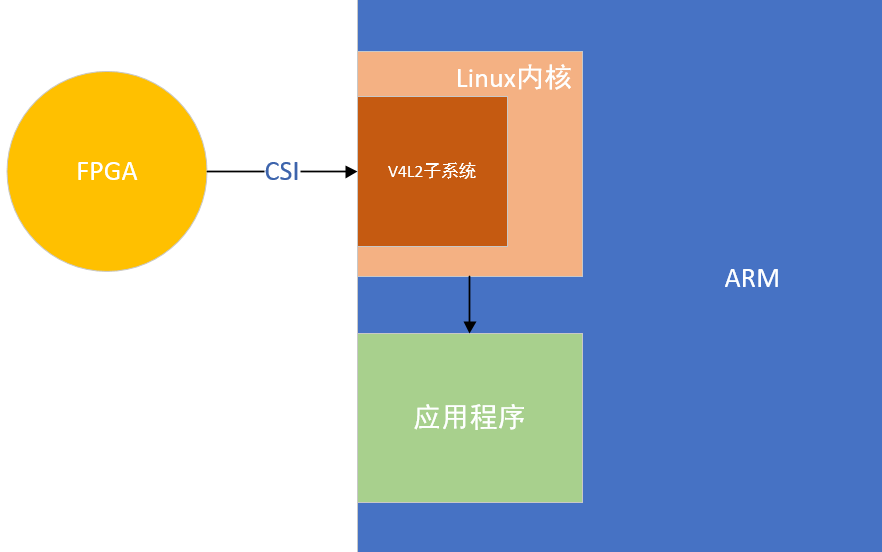

该案例实现T3(ARM Cortex-A7)与FPGA的CSI通信功能。案例使用的CSI0总线,最高支持分辨率为1080P@30fps,数据位宽为8bit,如下图所示。CSI0理论传输带宽为:1920 x 1080 x 8bit x 30fps ≈ 59MB/s。

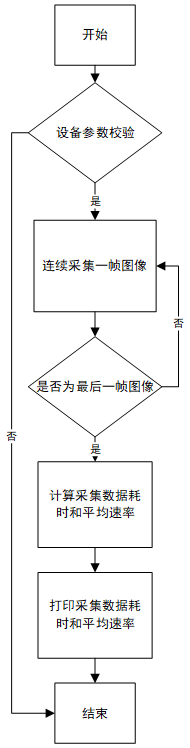

功能框图与程序流程图,如下图所示。

ARM端案例csi_test案例说明

ARM端案例csi_test主要功能如下:(1)基于Linux子系统V4L2;(2)通过CSI总线,采集指定帧数数据;(3)计算总耗时;(4)打印平均采集速率,并校验最后一帧图像的数据。

FPGA端案例parallel_csi_tx案例说明

FPGA端案例parallel_csi_tx主要功能如下:

(1)将测试数据(0x00~0xFF)写入FIFO;

(2)从FIFO读出数据,按行与帧的方式、1024x512的分辨率,通过CSI总线发送至ARM端。

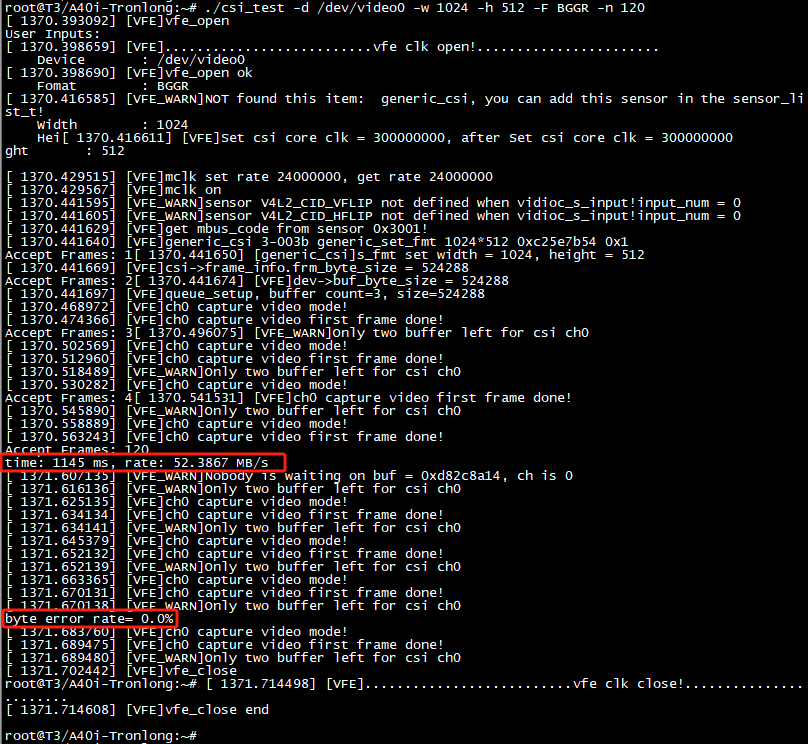

案例测试演示

FPGA程序将CSI_PCLK设置为65MHz,测试数据写入FIFO的时钟FIFO_WR_CLK设置为59MHz。由于FPGA端需将数据写入FIFO再从FIFO读出后发送,每一行与每一帧之间的间隔时间会受FIFO写入的速率影响,因此CSI通信的实际理论传输带宽应为:(59MHz x 8bit / 8)MB/s = 59MB/s。从上图可知,本次实测传输速率约为52.4MB/s,误码率为0,接近理论通信速率。

实测52.4MB/s!全国产ARM+FPGA的CSI通信案例分享!的更多相关文章

- 【新产品发布】【iCore2 ARM / FPGA 双核心板】

iCore2是一款包含ARM / FPGA两大利器的双核心板.ARM方面,采用意法半导体高性能的32位Cortex-M3内核STM32F103VE微处理器,主频达72MHz,并包含丰富外设接口.FPG ...

- 案例分享:Qt+Arm基于RV1126平台的内窥镜软硬整套解决方案(实时影像、冻结、拍照、录像、背光调整、硬件光源调整,其他产品也可使用该平台,如视频监控,物联网产品等等)

自研产品系列方案 1. 基于瑞芯微的 RV1126 芯片平台: 2. 外接 USB 摄像头(OV9734. OV6946.OV2740 等 UVC 模块)作为图像输入源: 3. 可通过 LED ...

- 《FPGA设计技巧与案例开发详解-第二版》全套资料包

本人参与写的一本书(TimeQuest一章由我所写),希望大家多多支持: 全书配套资料上传各大网盘资料中附送大量源码,你值得拥有--<FPGA设计技巧与案例开发详解-第二版>全套资料包-V ...

- FPGA+DSP SRIO通信(一)——DSP端参数设置(通道)

FPGA+DSP SRIO通信(一)——DSP端参数设置(通道) 原创 2017年04月19日 18:56:45 标签: SRIO-C66x 1217 经过漫长的探索之后,博主发现关于TI的板子调试和 ...

- 基于FPGA的光口通信开发案例|基于Kintex-7 FPGA SFP+光口的10G UDP网络通信开发案例

前言 自著名华人物理学家高锟先生提出"光传输理论",实用化的光纤传输产品始于1976年,经历了PDH→SDH→DWDM→ASON→MSTP的发展历程.本世纪初期,ASON/OADM ...

- 012 基于FPGA的网口通信实例设计【转载】

一.网口通信设计分类 通过上面其他章节的介绍,网口千兆通信,可以使用TCP或者UDP协议,可以外挂PHY片或者不挂PHY片,总结下来就有下面几种方式完成通信: 图8‑17基于FPGA的网口通信实例设计 ...

- 009 FPGA实现网口通信的几种方式【转载】

从硬件上来说,一般PHY芯片为模数混合电路,负责接收电.光这类模拟信号,经过解调和A/D转换后通过MII接口将信号交给MAC芯片进行处理.一般MAC芯片为纯数字电路. 物理层定义了数据传送与接收所需要 ...

- ARM与FPGA通过spi通信设计2.spi master的实现

这里主要放两个代码第一个是正常的不使用状态机的SPI主机代码:第二个是状态机SPI代码 1.不使用状态机:特权同学<深入浅出玩转FPGA>中DIY数码相框部分代码: /////////// ...

- ARM FPGA Extended Memory Interface

Connect a ARM Microcontroller to a FPGA using its Extended Memory Interface (EMI) http://elinux.org/ ...

- [转帖]全国产 台式机/笔记本/服务器都有 方正龙芯3A3000整机三连发

台式机/笔记本/服务器都有 方正龙芯3A3000整机三连发 2019年03月29日 17:17 4171 次阅读 稿源:快科技 7 条评论 https://www.cnbeta.com/article ...

随机推荐

- ABAP CDS 在7.55有比较大的更新

几年前翻译过CDS的相关文章,部分内容已经过时,比如当时的DDIC CDS在7.55以后已经沦为obsolete,在新版本中,开发者应使用DEFINE VIEW ENTITY而非DEFINE VIEW ...

- CCE云原生混部场景下的测试案例

本文分享自华为云社区<CCE云原生混部场景下在线任务抢占.压制离线任务CPU资源.保障在线任务服务质量效果测试>,作者:可以交个朋友. 背景 企业的 IT 环境通常运行两大类进程,一类是在 ...

- 特工17Agent17汉化版游戏破解金币方法修改破解金币的增加方法

又是一个renpy游戏,昨晚搞了半个小时搞定的,其实这个游戏要赚钱也不难,就是点点点就可以了,但是我觉得还是挺费劲的,因为好多道具都很贵,攒钱又不怎么容易,花钱的地方还挺多的,所以干脆不如直接破解了算 ...

- Surge多配置文件聚合配置方法

目录 摘要 1. Surge配置原理 2. Surge托管配置 3. Surge多配置文件聚合配置 (1)找到配置文件 (2)编辑配置文件 参考 摘要 Surge 是一个在 macOS 和iOS 平台 ...

- homebrew的安装和使用

目录 背景 安装xcode 安装homebrew 有关报错解决 卸载脚本 homebrew软件搜索 brew 常用命令 brew redis安装 PhpWebStudy安装 安装php 背景 最近用b ...

- uniapp中正确使用echart

uniapp中不能直接使用百度echart,要么就只能嵌入html,然后在html中进入echart进行使用,这样非常不方便, 下面介绍这个插件,对百度echart进行局部小改造,使他能在uniapp ...

- Shopify Theme 开发 —— 性能优化

一.概述 关于 Shopify Theme 的性能优化,通常有以下几点: 1.卸载未使用的应用程序 有些 app 会在 theme 里面插入一些代码,即使 app 未被使用,也可能会加载一些脚本文件, ...

- 效率工具mysoV0.3.0功能介绍

也许大家在日常工作中,有使用过提升效率的工具,比如快速搜索文件的Everything:火柴:Listary等,这些工具都在一定程度上提升您的工作效率.myso作为后来者,跟上述软件一样,也是为提升 ...

- Django信号与扩展:深入理解与实践

title: Django信号与扩展:深入理解与实践 date: 2024/5/15 22:40:52 updated: 2024/5/15 22:40:52 categories: 后端开发 tag ...

- EDP .Net开发框架--权限

平台下载地址:https://gitee.com/alwaysinsist/edp 权限介绍 权限实际上就是谁有权使用或是访问什么,这里的"谁"可以视作"授权对象&quo ...