spi master接口的fpga实现

前言

当你器件的引脚贼少的时候,需要主机和从机通信,spi就派上了用场,它可以一对多,但只是片选到的从机能和主机通信,其他的挂机。

spi:serial peripheral interface 串行外围接口

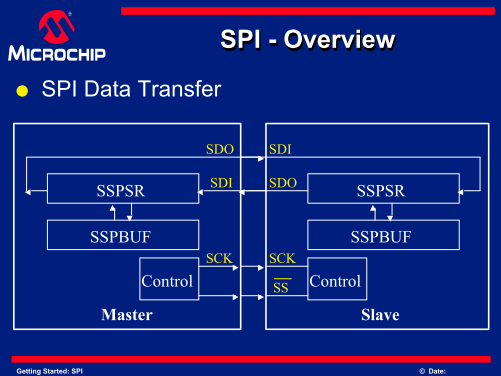

大致了解:

spi是个同步协议,数据在master和slaver间交换通过时钟sck,由于它是同步协议,时钟速率就可以各种变换。

sck:主机提供,从机不能操控,从器件由主机产生的时钟控制。数据只有在sck来了的上升沿或者下降沿才传输。

高级一点的spi芯片有配置寄存器,高级一点的工作有四种模式,采样相位和sck空闲电平可配置。

当然在这里我们主要实现简单的spi协议:sck是系统时钟的四分频,wr请求信号有效时,主机开始工作,数据位8bit,sck空闲时低电平,工作时第一个沿数据传输。只有一个从机,cs低电平片选。

看下结构:

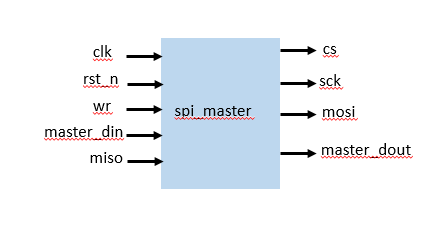

接口定义:

编码实现:(版权所有,请勿用于商业用途,仅供学习使用)

//************************************************

// Filename : spi_ms_test1.v

// Author : Kingstacker

// Company : School

// Email : kingstacker_work@163.com

// Device : Altera cyclone4 ep4ce6f17c8

// Description : spi master module;data 8bit;sck is 4 div of the clk;

//************************************************

)(

//input;

input wire clk,

input wire rst_n,

input wire wr, //send request;

:] master_din, //the data you want send;

input wire miso, //the data form slave;

//output;

output reg cs, //slave select;

output reg sck, //data exchange clock;

output reg mosi, //master out;

:] master_dout //the data you received;

);

:] DIV_NUMBER = ; //div number,you can change;

) - 'b1; //max cnt number,6/2 -1 ;

reg cnt; //sck cnt;

reg sck_en; //enable sck;

reg data_cnt_en;

reg sck_reg1;

reg sck_reg2;

wire sck_p; //posedge sck;

wire sck_n; //negedge sck;

wire send_over;

'b00;

'b01;

'b10;

:] cstate;

:] data_cnt; //cnt the send data;

:] master_din_reg;

:] master_dout_reg;

:] mosi_cnt;

//produce sck;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cnt <= ;

sck <= 'b0;

end //if

else begin

'b1) begin

if (cnt == CNT_MAX) begin

cnt <= ;

sck <= ~sck;

end

else begin

cnt <= cnt + 'b1;

sck <= sck;

end

end

else begin

cnt <= ;

sck <= 'b0;

end

end //else

end //always

//produce sck_p and sck_n;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

sck_reg1 <= 'b0;

sck_reg2 <= 'b0;

end //if

else begin

sck_reg1 <= sck;

sck_reg2 <= sck_reg1;

end //else

end //always

assign sck_p = (sck_reg1 & (~sck_reg2)); //sck posedge;

assign sck_n = ((~sck_reg1) & sck_reg2); //sck negedge;

//fsm;hot code;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cstate <= IDEL;

end

else begin

case (cstate)

IDEL: cstate <= (wr)? SEND : IDEL;

SEND: cstate <= (send_over) ? FINISH : SEND;

FINISH: cstate <= IDEL;

default: cstate <= IDEL;

endcase //case

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cs <= 'b1;

data_cnt_en <= 'b0;

sck_en <= 'b0;

master_din_reg <= ;

master_dout <= ;

end

else begin

case (cstate)

IDEL: begin

data_cnt_en <= 'b0;

master_din_reg <= (wr) ? master_din : master_din_reg; //load the data you want send to slaver;

end

SEND: begin

data_cnt_en <= 'b1;

cs <= 'b0;

sck_en <= 'b1;

master_dout <= (send_over) ? master_dout_reg : master_dout; //master receiverd data;

end

FINISH: begin //send and load ok;

sck_en <= 'b0;

cs <= 'b1;

data_cnt_en <= 'b0;

end

default: begin

cs <= 'b1;

sck_en <= 'b0;

data_cnt_en <= 'b0;

end

endcase //case

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

data_cnt <= ;

end

else begin

data_cnt <= (data_cnt_en) ? (data_cnt + 'b1) : 5'd0; //4 div * 8bit = 32 cnt;

end

end

'b0;

//rising edge miso;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

master_dout_reg <= ;

end

else begin

master_dout_reg <= (sck_p) ? {master_dout_reg[:],miso} : master_dout_reg;

end

end

//miso;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

mosi_cnt <= ;

end

else begin

if (sck_n) begin

'd7) begin

mosi_cnt <= ;

end

else begin

mosi_cnt <= mosi_cnt + 'b1;

end

end

else begin

mosi_cnt <= mosi_cnt;

end

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

mosi <= 'b0;

end

else begin

mosi <= (sck_n) ? master_din_reg['d7-mosi_cnt] : mosi;

end

end

endmodule

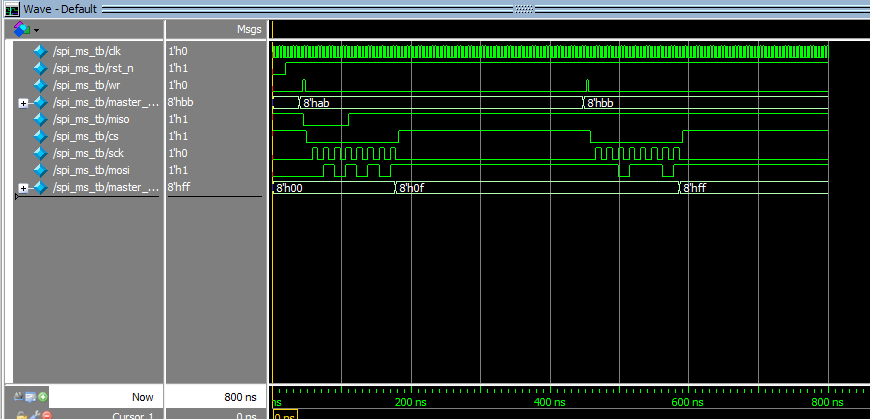

仿真:

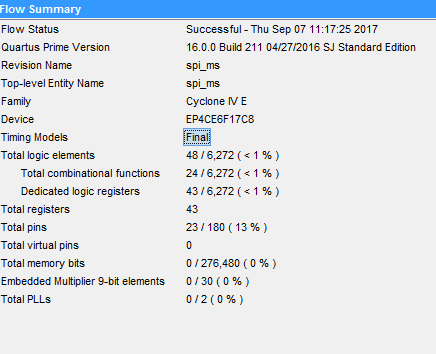

综合资源使用:

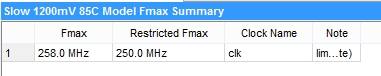

Fmax:

以上。

spi master接口的fpga实现的更多相关文章

- spi slaver接口的fpga实现

前言 spi从机接口程序,数据位8bit,sck空闲时低电平,工作时第一个沿数据传输.只有一个从机,cs低电平片选,slaver开始工作. 流程: 接口定义: 编码实现:(版权所有,请勿用于商业用途, ...

- ARM与FPGA通过spi通信设计2.spi master的实现

这里主要放两个代码第一个是正常的不使用状态机的SPI主机代码:第二个是状态机SPI代码 1.不使用状态机:特权同学<深入浅出玩转FPGA>中DIY数码相框部分代码: /////////// ...

- Linux SPI总线和设备驱动架构之二:SPI通用接口层

通过上一篇文章的介绍,我们知道,SPI通用接口层用于把具体SPI设备的协议驱动和SPI控制器驱动联接在一起,通用接口层除了为协议驱动和控制器驱动提供一系列的标准接口API,同时还为这些接口API定义了 ...

- [转载]Linux驱动-SPI驱动 之二:SPI通用接口层

通过上一篇文章的介绍,我们知道,SPI通用接口层用于把具体SPI设备的协议驱动和SPI控制器驱动联接在一起,通用接口层除了为协议驱动和控制器驱动提供一系列的标准接口API,同时还为这些接口API定义了 ...

- SPI通信实验---verilog(FPGA作为从机,使用可读可写)

本实验讲究实用性,故设计思想为:主机先向从机发送地址,若是向从机写入数据,则向从机发送数据,若是读取从机数据,则向从机发送时钟,然后在时钟下降沿读取数据即可.cs信号上升沿作为SPI通信的结束信号.r ...

- Zynq-PL中创建AXI Master接口IP及AXI4-Lite总线主从读写时序测试(转)

转载:原文 http://www.eefocus.com/antaur/blog/17-08/423751_6cc0d.html 0. 引言 通过之前的学习,可以在PL端创建从机模式的AXI接口IP ...

- EMIF接口与FPGA的互联(转)

reference: https://blog.csdn.net/ruby97/article/details/7539151 DSP6455的EMIFA模块 之前介绍了DSP6455的GPIO和中断 ...

- 【iCore4 双核心板_FPGA】例程十三:基于SPI的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符HELLO. 3.通过串口精灵发送命令可以控制ARM·LE ...

- AM5728通过GPMC接口与FPGA高速数据通信实现

硬件:AM5728开发板:Artix-7开发板软件:Linux am57xx-evm 4.4.19:Vivado 2015.2作者:杭州矢志信息科技有限公司邮箱:admin@sysjoint.com ...

随机推荐

- 函数响应式编程及ReactiveObjC学习笔记 (四)

今天我们继续看其他的类别 UIImagePickerController+RACSignalSupport.h #import <UIKit/UIKit.h> @class RACDele ...

- 【SignalR学习系列】1. SignalR理论介绍

什么是SignalR? ASP.NET SignalR 是一个让 ASP.NET开发者可以简单地给自己的程序添加即时通讯功能的开发库.即时通讯功能可以直接从服务器端给在线的客户端发送数据,而不用等待客 ...

- Flunetd 用于统一日志记录层的开源数据收集器

传统的日志查看方式 使用fluentd之后 一.介绍 Fluentd是一个开源的数据收集器,可以统一对数据收集和消费,以便更好地使用和理解数据. 几大特色: 使用JSON统一记录 简单灵活可插拔架构 ...

- ABP从入门到精通(3):aspnet-zero-core 使用Redis缓存

一.Redis是什么? redis是一个key-value存储系统.和Memcached类似,它支持存储的value类型相对更多,包括string(字符串).list(链表).set(集合).zset ...

- 面向对象设计——抽象工厂(Abstract Factory)模式

定义 提供一个创建一系列相关或者相互依赖对象的接口,而无需指定它们具体的类.抽象工厂允许客户使用抽象的接口来创建一组相关的产品,而不需要知道或关心实际产出的具体产品是什么.这样一来,客户就能从具体的产 ...

- hdu--4148--Length of S(n)

#include<iostream> #include<string> #include<cstring> void priTable(); using names ...

- Java Socket 编程

1. 背景 网络编程是指编写运行在多个设备(计算机)的程序,这些设备都通过网络连接起来. java.net 包中 J2SE 的 API 包含有类和接口,它们提供低层次的通信细节.你可以直接使用这些类和 ...

- Head First 设计模式 第5章 单例模式

第5章 单例模式 1.定义:确保一个类只有一个实例,并为其创建访问点. 2.单例模式的类图: 对应的单例模式的代码: package com.ek.singleton; /** * @包名 com.e ...

- HDU--1003 Max Sum(最大连续子序列和)

Problem Description Given a sequence a[1],a[2],a[3]......a[n], your job is to calculate the max sum ...

- Unicode、UTF-8 和 ISO8859-1到底有什么区别

说明:本文转载于新浪博客,旨在方便知识总结.原文地址:http://blog.sina.com.cn/s/blog_673c81990100t1lc.html 本文主要包括以下几个方面:编码基本知识, ...