spi master接口的fpga实现

前言

当你器件的引脚贼少的时候,需要主机和从机通信,spi就派上了用场,它可以一对多,但只是片选到的从机能和主机通信,其他的挂机。

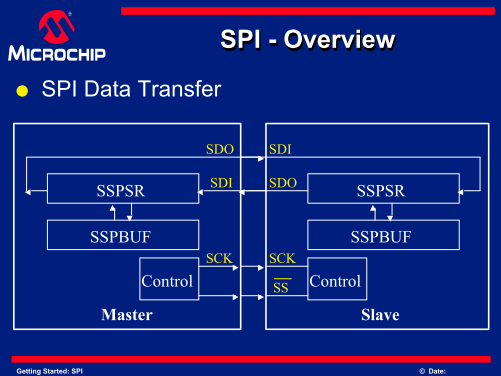

spi:serial peripheral interface 串行外围接口

大致了解:

spi是个同步协议,数据在master和slaver间交换通过时钟sck,由于它是同步协议,时钟速率就可以各种变换。

sck:主机提供,从机不能操控,从器件由主机产生的时钟控制。数据只有在sck来了的上升沿或者下降沿才传输。

高级一点的spi芯片有配置寄存器,高级一点的工作有四种模式,采样相位和sck空闲电平可配置。

当然在这里我们主要实现简单的spi协议:sck是系统时钟的四分频,wr请求信号有效时,主机开始工作,数据位8bit,sck空闲时低电平,工作时第一个沿数据传输。只有一个从机,cs低电平片选。

看下结构:

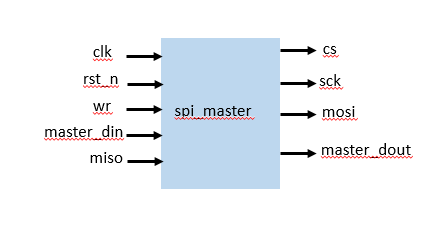

接口定义:

编码实现:(版权所有,请勿用于商业用途,仅供学习使用)

//************************************************

// Filename : spi_ms_test1.v

// Author : Kingstacker

// Company : School

// Email : kingstacker_work@163.com

// Device : Altera cyclone4 ep4ce6f17c8

// Description : spi master module;data 8bit;sck is 4 div of the clk;

//************************************************

)(

//input;

input wire clk,

input wire rst_n,

input wire wr, //send request;

:] master_din, //the data you want send;

input wire miso, //the data form slave;

//output;

output reg cs, //slave select;

output reg sck, //data exchange clock;

output reg mosi, //master out;

:] master_dout //the data you received;

);

:] DIV_NUMBER = ; //div number,you can change;

) - 'b1; //max cnt number,6/2 -1 ;

reg cnt; //sck cnt;

reg sck_en; //enable sck;

reg data_cnt_en;

reg sck_reg1;

reg sck_reg2;

wire sck_p; //posedge sck;

wire sck_n; //negedge sck;

wire send_over;

'b00;

'b01;

'b10;

:] cstate;

:] data_cnt; //cnt the send data;

:] master_din_reg;

:] master_dout_reg;

:] mosi_cnt;

//produce sck;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cnt <= ;

sck <= 'b0;

end //if

else begin

'b1) begin

if (cnt == CNT_MAX) begin

cnt <= ;

sck <= ~sck;

end

else begin

cnt <= cnt + 'b1;

sck <= sck;

end

end

else begin

cnt <= ;

sck <= 'b0;

end

end //else

end //always

//produce sck_p and sck_n;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

sck_reg1 <= 'b0;

sck_reg2 <= 'b0;

end //if

else begin

sck_reg1 <= sck;

sck_reg2 <= sck_reg1;

end //else

end //always

assign sck_p = (sck_reg1 & (~sck_reg2)); //sck posedge;

assign sck_n = ((~sck_reg1) & sck_reg2); //sck negedge;

//fsm;hot code;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cstate <= IDEL;

end

else begin

case (cstate)

IDEL: cstate <= (wr)? SEND : IDEL;

SEND: cstate <= (send_over) ? FINISH : SEND;

FINISH: cstate <= IDEL;

default: cstate <= IDEL;

endcase //case

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cs <= 'b1;

data_cnt_en <= 'b0;

sck_en <= 'b0;

master_din_reg <= ;

master_dout <= ;

end

else begin

case (cstate)

IDEL: begin

data_cnt_en <= 'b0;

master_din_reg <= (wr) ? master_din : master_din_reg; //load the data you want send to slaver;

end

SEND: begin

data_cnt_en <= 'b1;

cs <= 'b0;

sck_en <= 'b1;

master_dout <= (send_over) ? master_dout_reg : master_dout; //master receiverd data;

end

FINISH: begin //send and load ok;

sck_en <= 'b0;

cs <= 'b1;

data_cnt_en <= 'b0;

end

default: begin

cs <= 'b1;

sck_en <= 'b0;

data_cnt_en <= 'b0;

end

endcase //case

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

data_cnt <= ;

end

else begin

data_cnt <= (data_cnt_en) ? (data_cnt + 'b1) : 5'd0; //4 div * 8bit = 32 cnt;

end

end

'b0;

//rising edge miso;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

master_dout_reg <= ;

end

else begin

master_dout_reg <= (sck_p) ? {master_dout_reg[:],miso} : master_dout_reg;

end

end

//miso;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

mosi_cnt <= ;

end

else begin

if (sck_n) begin

'd7) begin

mosi_cnt <= ;

end

else begin

mosi_cnt <= mosi_cnt + 'b1;

end

end

else begin

mosi_cnt <= mosi_cnt;

end

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

mosi <= 'b0;

end

else begin

mosi <= (sck_n) ? master_din_reg['d7-mosi_cnt] : mosi;

end

end

endmodule

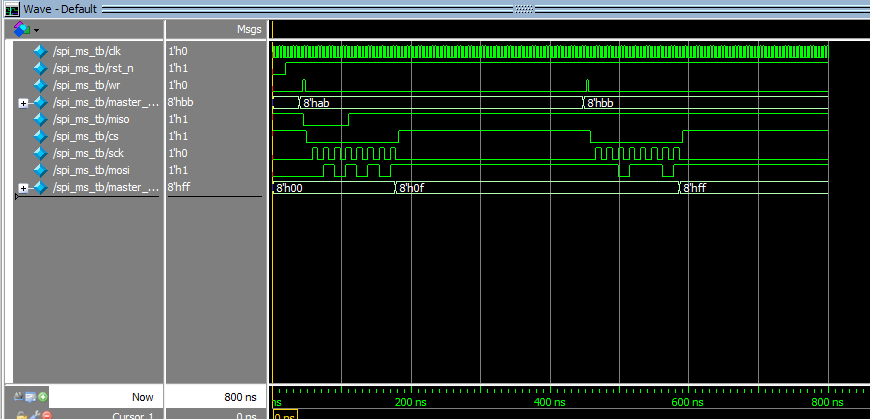

仿真:

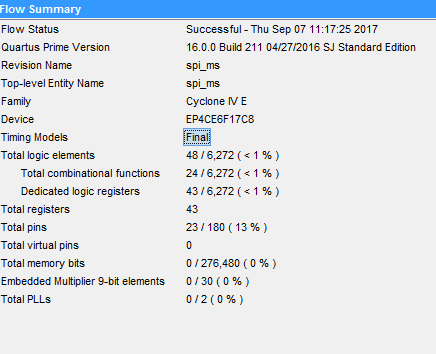

综合资源使用:

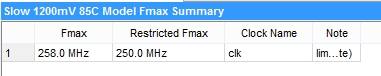

Fmax:

以上。

spi master接口的fpga实现的更多相关文章

- spi slaver接口的fpga实现

前言 spi从机接口程序,数据位8bit,sck空闲时低电平,工作时第一个沿数据传输.只有一个从机,cs低电平片选,slaver开始工作. 流程: 接口定义: 编码实现:(版权所有,请勿用于商业用途, ...

- ARM与FPGA通过spi通信设计2.spi master的实现

这里主要放两个代码第一个是正常的不使用状态机的SPI主机代码:第二个是状态机SPI代码 1.不使用状态机:特权同学<深入浅出玩转FPGA>中DIY数码相框部分代码: /////////// ...

- Linux SPI总线和设备驱动架构之二:SPI通用接口层

通过上一篇文章的介绍,我们知道,SPI通用接口层用于把具体SPI设备的协议驱动和SPI控制器驱动联接在一起,通用接口层除了为协议驱动和控制器驱动提供一系列的标准接口API,同时还为这些接口API定义了 ...

- [转载]Linux驱动-SPI驱动 之二:SPI通用接口层

通过上一篇文章的介绍,我们知道,SPI通用接口层用于把具体SPI设备的协议驱动和SPI控制器驱动联接在一起,通用接口层除了为协议驱动和控制器驱动提供一系列的标准接口API,同时还为这些接口API定义了 ...

- SPI通信实验---verilog(FPGA作为从机,使用可读可写)

本实验讲究实用性,故设计思想为:主机先向从机发送地址,若是向从机写入数据,则向从机发送数据,若是读取从机数据,则向从机发送时钟,然后在时钟下降沿读取数据即可.cs信号上升沿作为SPI通信的结束信号.r ...

- Zynq-PL中创建AXI Master接口IP及AXI4-Lite总线主从读写时序测试(转)

转载:原文 http://www.eefocus.com/antaur/blog/17-08/423751_6cc0d.html 0. 引言 通过之前的学习,可以在PL端创建从机模式的AXI接口IP ...

- EMIF接口与FPGA的互联(转)

reference: https://blog.csdn.net/ruby97/article/details/7539151 DSP6455的EMIFA模块 之前介绍了DSP6455的GPIO和中断 ...

- 【iCore4 双核心板_FPGA】例程十三:基于SPI的ARM与FPGA通信实验

实验现象: 1.先烧写ARM程序,然后烧写FPGA程序. 2.打开串口精灵,通过串口精灵给ARM发送数据从而给FPGA发送数据 ,会接收到字符HELLO. 3.通过串口精灵发送命令可以控制ARM·LE ...

- AM5728通过GPMC接口与FPGA高速数据通信实现

硬件:AM5728开发板:Artix-7开发板软件:Linux am57xx-evm 4.4.19:Vivado 2015.2作者:杭州矢志信息科技有限公司邮箱:admin@sysjoint.com ...

随机推荐

- Spring源码情操陶冶-AbstractApplicationContext#postProcessBeanFactory

阅读源码有利于陶冶情操,承接前文Spring源码情操陶冶-AbstractApplicationContext#prepareBeanFactory 约定:web.xml中配置的contextClas ...

- Java以及PHP安装环境

开学前想把web的知识系统掌握一下,跟着极客学院学html5. 安装了intellij idead.xampp.jdk.eclipse for php. 下面列举一些安装过程中会出现的问题,以及解决. ...

- 智慧航空AI大赛-阿里云算法大赛总结 第一赛季总结

[以前的文章]最后一公里极速配送 - 阿里云算法大赛总结 总结一下新的教训 1.由于都是NP难题,获得最优解用常规的方法非常困难,对于不是算法科班出身的人来说,首先应该到网络上寻找一下论文,是否有一些 ...

- python中list总结

转自python中list总结 一.list可以看做是一个数据结构,也是一个class, 用help(list)可以看见其方法,元素的增删改查都有各种现成的方法, 二.list操作包含以下函数:1.c ...

- 【模板--完全背包】HDU--2602 Bone Collector

Problem Description Many years ago , in Teddy's hometown there was a man who was called "Bone C ...

- 对接第三方平台JAVA接口问题推送和解决

前言 本节所讲为实际项目中与第三方对接出现的问题最后还是靠老大解决了问题以此作为备忘录,本篇分为三小节,一小节解析Java加密接口数据,二小节解析XML文件需注意问题,最后一节则是请求Java Soa ...

- 【机器学习笔记之二】决策树的python实现

本文结构: 是什么? 有什么算法? 数学原理? 编码实现算法? 1. 是什么? 简单地理解,就是根据一些 feature 进行分类,每个节点提一个问题,通过判断,将数据分为几类,再继续提问.这些问题是 ...

- JavaScript闭包只学这篇就够了

闭包不是魔法 这篇文章使用一些简单的代码例子来解释JavaScript闭包的概念,即使新手也可以轻松参透闭包的含义. 其实只要理解了核心概念,闭包并不是那么的难于理解.但是,网上充斥了太多学术性的文章 ...

- HTML 笔记 基础1

html 笔记 20170807 晴 <h1>标题</h1> 标题分为6个 从1到6字体逐渐变小 <p>段落</p> <html> < ...

- 使用postgre数据库实现树形结构表的子-父级迭代查询,通过级联菜单简单举例

前言:开发常用的关系型数据库MySQL,mssql,postgre,Oracle,简单的增删改查的SQL语句都与标准SQL兼容,这个不用讲,那么对于迭代查询(不严格的叫法:递归查询)每种数据库都不一样 ...