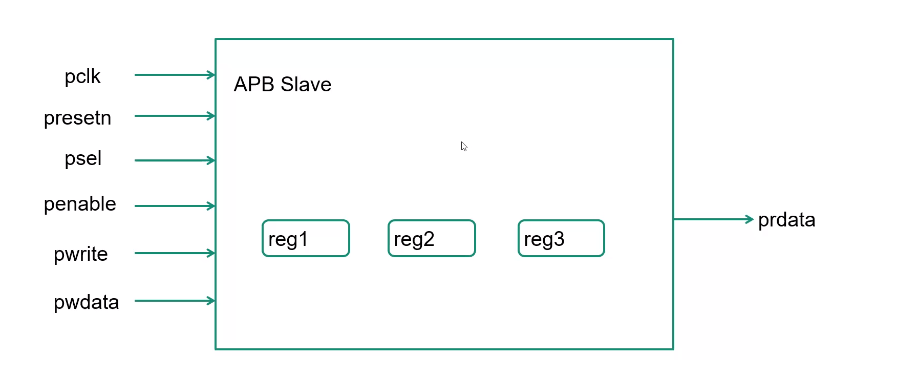

APB Slave Design

APB Slave Design

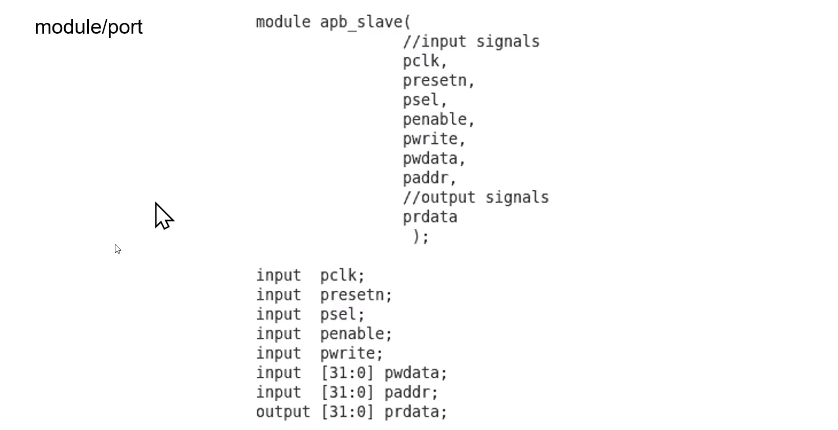

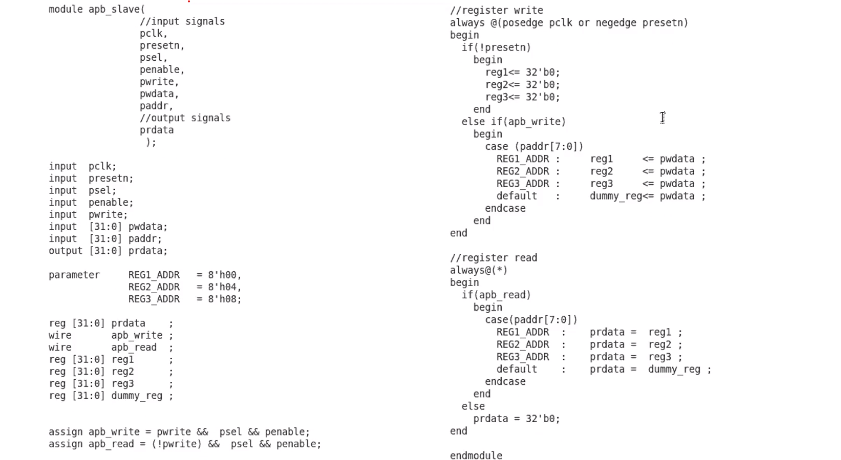

module apb_slave

#(

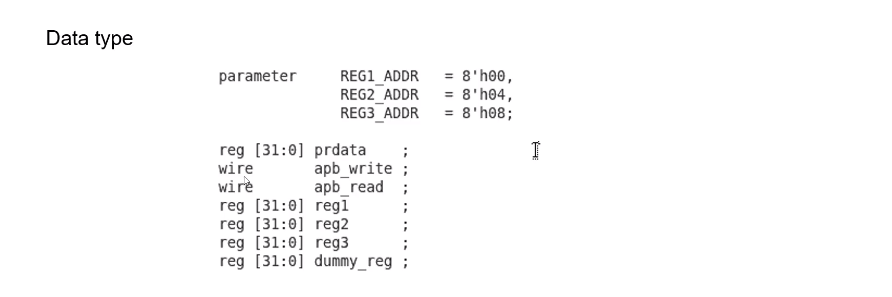

REG1_ADDR = 8'h00,

REG2_ADDR = 8'h04,

REG3_ADDR = 8'h08

)

(

// input signals

input pclk,

input presetn,

input psel,

input penable,

input pwrite,

input [31:0] pwdata,

input [31:0] paddr,

output reg [31:0] prdata,

);

// 读写信号

wire apb_write;

wire apb_read;

// 定义三个寄存器

reg [31:0] reg1;

reg [31:0] reg2;

reg [31:0] reg3;

reg [31:0] dummy_reg;

// 产生读写信号

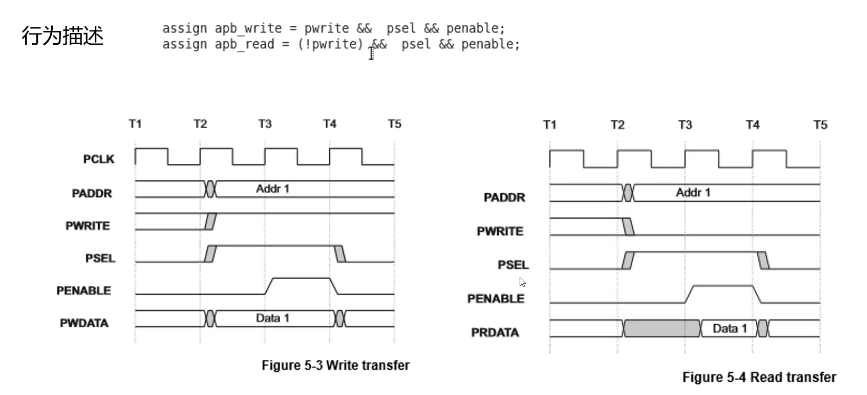

assign apb_write = pwrite && psel && penable;

assign apb_read = (!pwrite) && psel && penable;

// 写操作

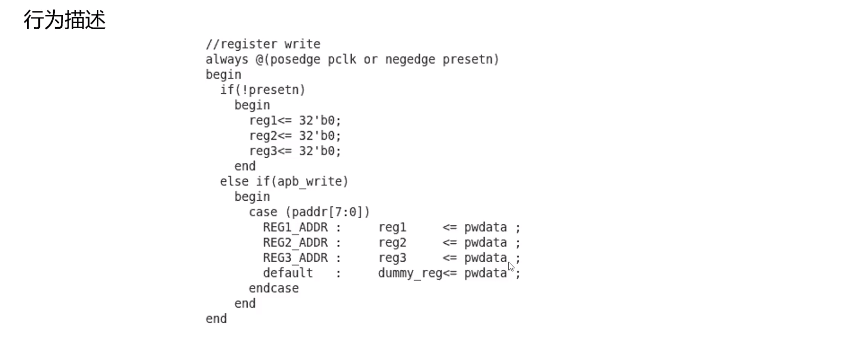

always @ (posedge pclk or negedge presetn) begin

if(!presetn)

begin

reg1 <= 32'b0;

reg2 <= 32'b0;

reg3 <= 32'b0;

end

else if(ahb_write)

begin

case (paddr[7:0])

REG1_ADDR:reg1 <= pwdata;

REG2_ADDR:reg2 <= pwdata;

REG3_ADDR:reg3 <= pwdata;

default:dummy_reg <= pwdata;

endcase

end

end

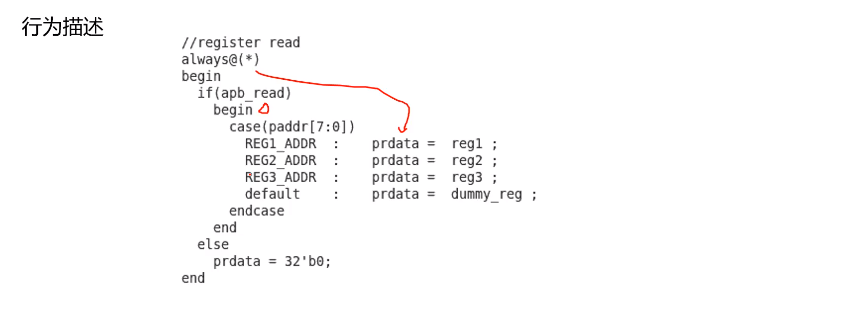

always @ (posedge pclk or negedge presetn) begin

if(ahb_read)

begin

case (paddr[7:0])

REG1_ADDR:prdata <= reg1;

REG2_ADDR:prdata <= reg2;

REG3_ADDR:prdata <= reg3;

default:prdata <= dummy_reg;

endcase

end

end

endmodule

总结

- 硬件思维和软件思维需要区分,Verilog是并行执行的

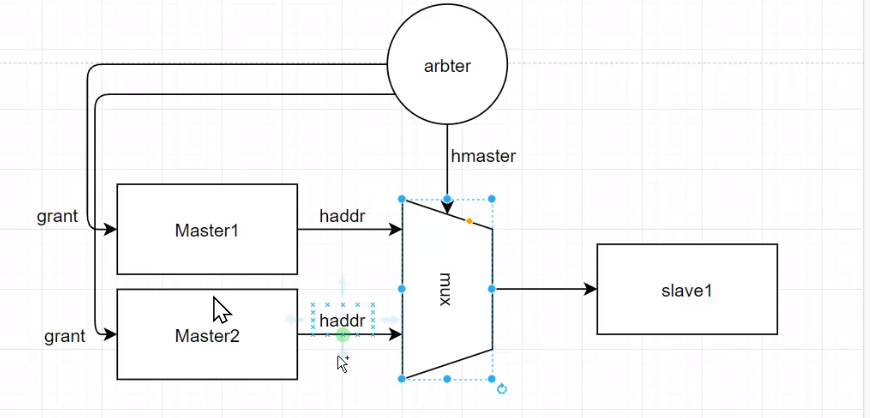

- 多个master,其中一个被grant,其他的master发送的信号仍然存在,所以需要mux通过hmaster进行选择master

APB Slave Design的更多相关文章

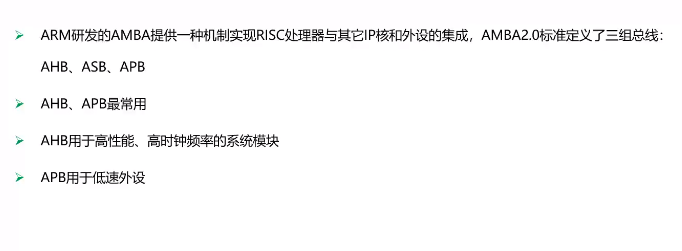

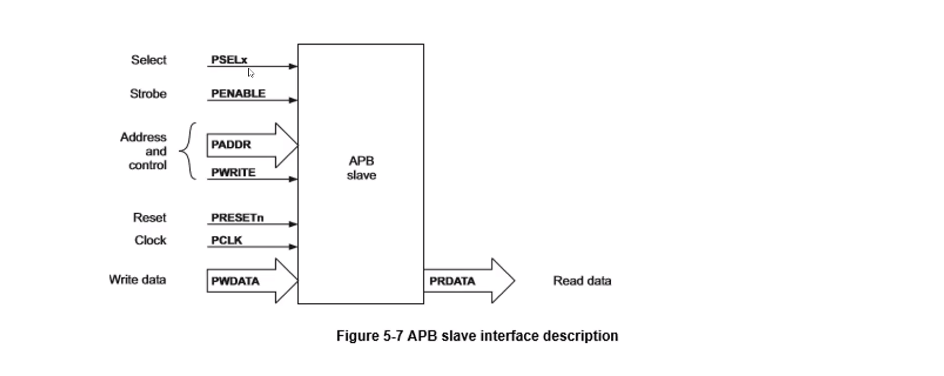

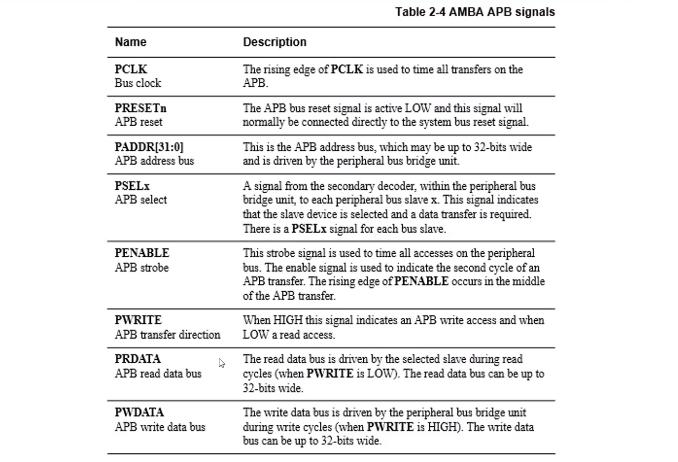

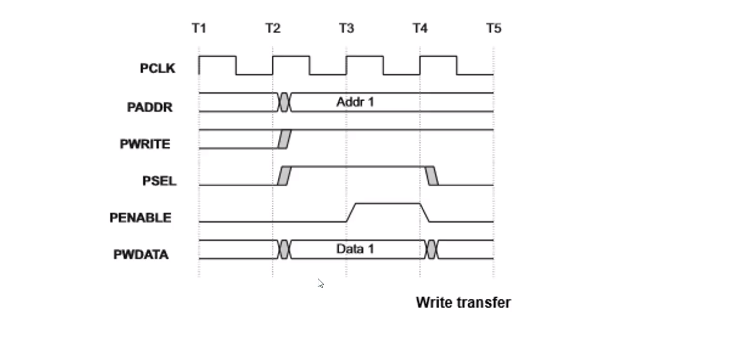

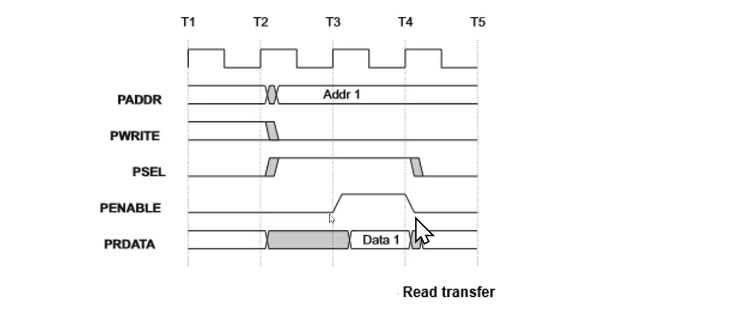

- APB总线

APB(Advance Peripheral Bus)是AMBA总线的一部分,从1998年第一版至今共有3个版本. AMBA 2 APB Specfication:定义最基本的信号interface, ...

- DMA-330(一)

DMA Controller的interface: DMA Controller提供这些feature: 1)instruction set,对DMA transfer进行program 2)AXI ...

- STM

STM(System Trace macrocell) STM是coresight system中的一个trace source,可以提供high-bandwidth的trace data. STM优 ...

- 痞子衡嵌入式:Ethos-U55,ARM首款面向Cortex-M的microNPU

大家好,我是痞子衡,是正经搞技术的痞子.今天痞子衡给大家介绍的是ARM Ethos-U55. ARM 前几天刚发布了 Cortex-M 家族最新一款内核 - Cortex-M55 以及首款面向 Cor ...

- AHB总线和APB总线

AHB主要用于高性能模块(如CPU.DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作:非三态的实现方式:支持突发传输:支持分段传输:支持多个主控制器:可配置 ...

- AHB/APB简介

AHB AHB总线互联结构图 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大.数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SOC设计中得到了广泛应用.在基于IP复用的 ...

- AMBA总线协议AHB、APB、AXI对比分析【转】

转自:https://blog.csdn.net/ivy_reny/article/details/56274412 一.AMBA概述 AMBA (Advanced Microcontrolle ...

- [转]AMBA、AHB、APB、ASB总线简介

[转]http://www.cnblogs.com/zhaozhong1989/articles/3092140.html 1.前言 随着深亚微米工艺技术日益成熟,集成电路芯片的规模越来越大.数字IC ...

- Qsys 设计流程---Qsys System Design Tutorial

Qsys 设计流程 ---Qsys System Design Tutorial 1.Avalon-MM Pipeline Bridge Avalon-MM Pipeline Bridge在slave ...

- 简易APB4 slave实践

一个简易的(不完整的)APB4 slave的可以没有PREADY和PSLVERR,这两个信号都被赋予常数,以及没有PPROT. 两种不同类型的寄存器: 图: 普通寄存器电路图 图: 带读写控制寄存器电 ...

随机推荐

- Windows系统激活工具HK

下载:https://wwsi.lanzoum.com/iyUNn10e7foh 密码:g05d GitHub开源 .无毒 原文链接:https://github.com/zbezj/HEU_KMS_ ...

- 9.mysql的数据迁移到es中

背景 从开发的角度说,就是老板叫我用es了,没那么多为什么,爸爸说了算 从业务角度,mysql已经不能满足我对全文检索的需求了.我需要检索某一个字段包含"圣诞节刚刚过去"这一字符串 ...

- 第十三部分_awk

一.awk介绍 1. awk概述 awk是一种编程语言,主要用于在linux/unix下对文本和数据进行处理,是linux/unix下的一个工具.数据可以来自标准输入.一个或多个文件,或其它命令的输出 ...

- 【昇腾】ModelArts与Atlas 200 DK云端协同开发——行人检测Demo(完整版)

摘要:本文主要为大家展示如何基于ModelArts与Atlas 200 DK 端云协同开发的行人检测Demo实现过程. 基于开源数据集,使用ModelArts训练行人检测模型,在本地MindStudi ...

- 云图说|ModelArts开发环境,让AI开发、探索、教学更简单

摘要:ModelArts开发环境,以云原生的资源使用和开发工具链的集成,目标为不同类型AI开发.探索.教学用户. 本文分享自华为云社区<[云图说]| 第280期 ModelArts开发环境,让A ...

- 华为云MVP付健权:从机械工程师到AI开发者的华丽转身

摘要:谁说AI开发难,看一个机械工程师是如何转型成为AI工程师的. 付健权,华为云MVP,企业上云导师.软通动力,售前解决方案经理,为制造业讲解华为云产品,为客户提供上云和云上解决方案.为企业提供大数 ...

- 一文了解如何使用移动应用安全组件Soot和Flowdroid

摘要:移动应用安全检测,soot.flowdroid分别作为静态分析.污点分析主要工具,能我们能够快速高效的进行检测分析.本文主要介绍两个工具的基本操作及相应的使用场景 本文分享自华为云社区<移 ...

- 专注提升用户体验,Superset 1.3发布!

近期Superset发布了新的版本1.3.0,此版本专注于提升用户体验.并进行了大量的改进与错误修复. 用户体验 此版本的一个主要目标是改进仪表盘原生过滤器.这些过滤器的级别为仪表盘级别,而不是图表级 ...

- Solon Aop 特色开发(4)Bean 扫描的三种方式

Solon,更小.更快.更自由!本系列专门介绍Solon Aop方面的特色: <Solon Aop 特色开发(1)注入或手动获取配置> <Solon Aop 特色开发(2)注入或手动 ...

- MySQL java new dat() 后插入数据库的时间不一致

别用时间字段,做为关联字段,代码里的时间和插到数据库中有误差 MySQL java new dat() 后插入数据库的时间不一致,代码里new 的时间插到数据库中不一致