MIPS指令的CPU实现:ALU设计

设计CPU的第一步,设计一个简单的逻辑运算单元ALU。同时对Verilog语言也有一定要求。

一、实验内容

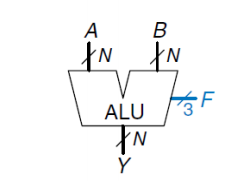

- 如图,ALU接受两个N位的输入,得到N位的输出,通过控制信号F决定运算功能。

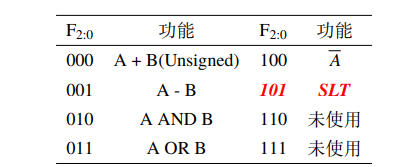

- 将ALU的输出结构与七段数码管显示模块连接,使用实验配置的NEXYS4开发板。

结构如下:

- 编写顶层模块top连接上述模块。

- 仿真,编写约束文件,生成二进制文件,在开发板上验证。

整体难度不大,主要任务就是编写ALU和top,以及约束文件。

但是这学期之前在摸鱼,这个小实验都没认真弄好。。。地基打不好,CPU肯定写不出来啊。

二、RTL级的部分Verilog代码,也是重点部分

ALU.v

真的很简单,方法两种,一种是always逻辑,一种是assign逻辑。

- always:

module ALU(

input wire [31:0] A,

input wire[31:0] B,

input wire [2:0] OP, // 输入用wire

output reg [31:0] F //输出用寄存器reg

);

always @(*) begin

case(OP)

3'b000: begin F <= A + B; end //这里实际上连进位都没有考虑

3'b001: begin F <= A - B; end

3'b010: begin F <= A & B; end

3'b011: begin F <= A | B; end

3'b100: begin F <= ~A; end

3'b101: begin F <= A<B; end

default: begin F <= 0; end

endcase

end

endmodule

- assign:

assign相当于连线,一般是将一个变量的值不间断地赋值给另一个变量,所以赋值的类型应用wire。

module ALU(

input wire [31:0] A,

input wire[31:0] B,

input wire [2:0] OP,

output wire [31:0] F

);

assign F = (OP == 3'b000) ? A + B:

(OP == 3'b001) ? A + B:

(OP == 3'b010) ? A + B:

(OP == 3'b011) ? A + B:

(OP == 3'b100) ? A + B:

(OP == 3'b101) ? A + B:

32'b0;

endmodule

数码管显示模块display.v和seg7.v(实验提供)

- display.v

module display(

input wire clk,reset,

input wire [31:0]s,

output wire [6:0]seg,

output reg [7:0]ans

);

reg [20:0]count;

reg [4:0]digit;

always@(posedge clk,posedge reset)

if(reset)

count = 0;

else

count = count + 1;

always @(posedge clk)

case(count[20:18])

0:begin

ans = 8'b11111110;

digit = s[3:0];

end

1:begin

ans = 8'b11111101;

digit = s[7:4];

end

2:begin

ans = 8'b11111011;

digit =s[11:8];

end

3:begin

ans = 8'b11110111;

digit = s[15:12];

end

4:begin

ans = 8'b11101111;

digit = s[19:16];

end

5:begin

ans = 8'b11011111;

digit = s[23:20];

end

6:begin

ans = 8'b10111111;

digit =s[27:24];

end

7:begin

ans = 8'b01111111;

digit = s[31:28];

end

endcase

seg7 U4(.din(digit),.dout(seg));

endmodule

- seg7.v

module seg7(

input wire [3:0]din,

output reg [6:0]dout

);

always@(*)

case(din)

5'h0:dout = 7'b000_0001;

5'h1:dout = 7'b100_1111;

5'h2:dout = 7'b001_0010;

5'h3:dout = 7'b000_0110;

5'h4:dout = 7'b100_1100;

5'h5:dout = 7'b010_0100;

5'h6:dout = 7'b010_0000;

5'h7:dout = 7'b000_1111;

5'h8:dout = 7'b000_0000;

5'h9:dout = 7'b000_0100;

5'ha:dout = 7'b000_1000;

5'hb:dout = 7'b110_0000;

5'hc:dout = 7'b011_0001;

5'hd:dout = 7'b100_0010;

5'he:dout = 7'b011_0000;

5'hf:dout = 7'b011_1000;

default:dout = 7'b111_1111;

endcase

endmodule

top.v

module top(

input wire clk, rst,

output wire[6:0] seg,

output wire[7:0] ans,

input wire [2:0] op,

input wire [7:0] num_1

);

wire [31:0] f; // f从ALU传给display

ALU U1(.A({24'b0,num_1}),.B(32'h1),.OP(op),.F(f)); // 输入a为8位扩充至32位,b为固定值32'h1

display U2(.clk(clk),.reset(rst),.s(f),.ans(ans),.seg(seg));

endmodule

三、存在的问题

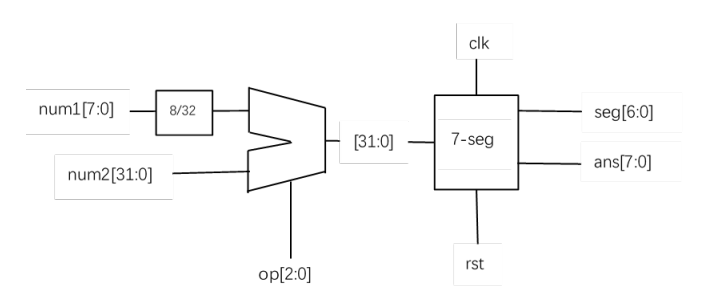

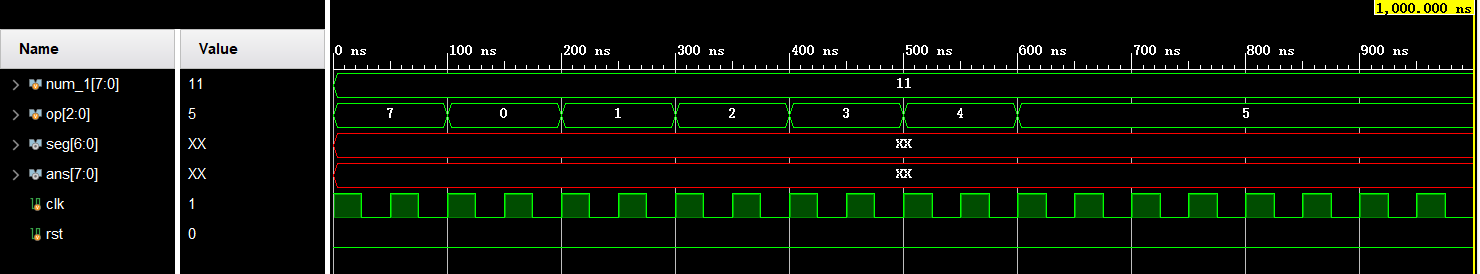

- 仿真测试中得不到结果,但是下到板子上以后能正常运行

test文件:

module test();

reg [7:0] num_1;

reg [2:0] op;

wire [6:0]seg;

wire [7:0]ans;

reg clk,rst;

always #25 clk = ~clk;

initial begin

clk = 1;

rst = 0;

num_1 = 8'h 11;

op = 3'b 111;

# 100 op = 3'b 000;

# 100 op = 3'b 001;

# 100 op = 3'b 010;

# 100 op = 3'b 011;

# 100 op = 3'b 100;

# 100 op = 3'b 101;

end

top x(

.clk(clk),

.rst(rst),

.seg(seg),

.ans(ans),

.num_1(num_1),

.op(op)

);

endmodule

MIPS指令的CPU实现:ALU设计的更多相关文章

- 自己动手写CPU之第五阶段(3)——MIPS指令集中的逻辑、移位与空指令

将陆续上传本人写的新书<自己动手写CPU>(尚未出版),今天是第17篇.我尽量每周四篇 5.4 逻辑.移位操作与空指令说明 MIPS32指令集架构中定义的逻辑操作指令有8条:and.and ...

- 16位CPU多周期设计

16位CPU多周期设计 这个工程完成了16位CPU的多周期设计,模块化设计,有包含必要的分析说明. 多周期CPU结构图 多周期CPU设计真值表 对应某一指令的情况,但仅当对应周期时才为对应的输出,不是 ...

- verilog实现的16位CPU单周期设计

verilog实现的16位CPU单周期设计 这个工程完成了16位CPU的单周期设计,模块化设计,包含对于关键指令的仿真与设计,有包含必要的分析说明. 单周期CPU结构图 单周期CPU设计真值表与结构图 ...

- 3.6 MIPS指令简介

计算机组成 3 指令系统体系结构 3.6 MIPS指令简介 MIPS秉承着指令数量少,指令功能简单的设计理念.那这样的设计理念是如何实现的呢?在这一节,我们就将来分析MIPS指令的特点. 相比于X86 ...

- MIPS指令 MIPS架构

华中科技大学 - 计算机组成原理 华中科技大学 - 计算机硬件系统设计 Microprocessor without Interlocked Pipleline Stages 无内部互锁流水级的微处理 ...

- verilog简易实现CPU的Cache设计

verilog简易实现CPU的Cache设计 该文是基于博主之前一篇博客http://www.cnblogs.com/wsine/p/4661147.html所增加的Cache,相同的内容就不重复写了 ...

- QtSpim实现MIPS指令的编写

QtSpim实现MIPS指令的编写 由于各种对齐问题,cnblogs的格式难以控制,故贴图片,谅解.

- MIPS指令学习二

1.MIPS寻址方式 MIPS架构的寻址模式有寄存器寻址.立即数寻址.寄存器相对寻址和PC相对寻址4种,其中寄存器相对寻址.PC相对寻址介绍如下: 1.1.寄存器相对寻址 这种寻址模式主要被加载/存储 ...

- P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2.p3.p4.p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽 ...

随机推荐

- Tomcat9配置HTTP/2

1 概述 Tomcat从Tomcat8的一些较新版本就支持HTTP/2了,Tomcat9直接支持,本文首先讲述了相关HTTP/2的特性,接着利用一个简单的开源工具mkcert生成证书并利用该证书配置H ...

- .netcore 写快递100的快递物流信息查询接口

快递100的物流信息查询接口,官方提供了一些demo;还好官方提供的代码是.netcore版本写的,不过写的有点low;根据官方提供的代码,我按照.netcore 的风格重构了代码:核心代码如下: / ...

- Day11_58_增强for循环

增强for循环 * 语法 : for(数据类型 变量名:数组名/集合名) * 集合如果要使用增强for循环需要先使用泛型来确定元素类型,如果没有使用泛型就使用foreach,那么变量类型设置为Obje ...

- 程序员的开源月刊《HelloGitHub》第61期

兴趣是最好的老师,HelloGitHub 让你对编程感兴趣! 简介 分享 GitHub 上有趣.入门级的开源项目. 内容包括:有趣.入门级的开源项目.开源书籍.实战项目.企业级项目等,让你在短时间内感 ...

- Mysql - 使用入门

本文是学习 Mysql必知必会 后的笔记 学习之前需要创建一个数据库,然后导入下面两个mysql脚本 create database db1 charset utf8; ############### ...

- pc/shouji/weixin判断跳转

pc 和 手机端 判断 function IsPC() { var userAgentInfo = navigator.userAgent; var Agents = ["Android&q ...

- Python学习笔记-StatsModels 统计回归(3)模型数据的准备

1.读取数据文件 回归分析问题所用的数据都是保存在数据文件中的,首先就要从数据文件读取数据. 数据文件的格式很多,最常用的是 .csv,.xls 和 .txt 文件,以及 sql 数据库文件的读取 . ...

- vscode 将本地项目上传到github、从github克隆项目以及删除github上的某个文件夹

一.将本地项目上传到github 1.创建本地仓库(文件夹) mkdir study//创建文件夹studycd study //进入study文件夹 2.通过命令git init把这个文件夹变成Gi ...

- LINQ之查询语法

新开一节LINQ的入门讲解. LINQ(Language Integrated Query)语言集成查询,是C#语言的扩展,它的主要功能是从数据集中查询数据,就像通过sql语句从数据库查询数据一样(本 ...

- Mybatis学习之自定义持久层框架(五) 自定义持久层框架:封装CRUD操作

前言 上一篇文章我们完成了生产sqlSession的工作,与数据库的连接和创建会话的工作都已完成,今天我们可以来决定会话的内容了. 封装CRUD操作 首先我们需要创建一个SqlSession接口类,在 ...