P4-verilog实现mips单周期CPU

最近对学习的掌控可能出现了问题,左支右绌,p2挂了,p2、p3、p4、p5每周在计组花的连续时间少了很多,学习到的东西也少了很多,流水线都还没真正开始写,和别人比落后了一大截,随笔自然就荒废了,我得尽快调整状态,下决心只要学不死,就往死里学,尽快迎头赶上鸭!!

由于p4断断续续做的,现在临考前来总结一下p4,顺便恢复一下记忆,对Verilog命名规范、p4设计CPU技巧、实现细节等等进行初步总结,如有不对烦请指正。

一、Verilog设计单周期CPU流程

由于p3和理论部分我们已经掌握了单周期CPU的理论知识,也对CPU的实现有形象化的认识。我们要做的就是“翻译”一遍。

我主要是先设计CPU文档,再用Verilog描述CPU。

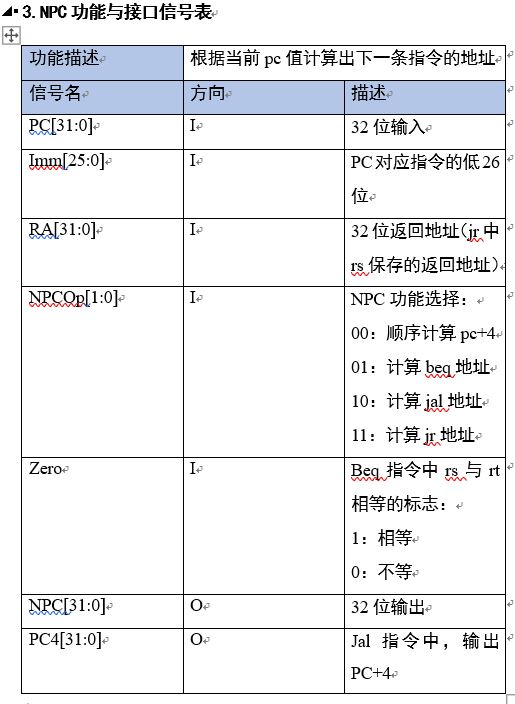

1.画出各个部件的端口及功能定义表,定义各个基础部件的端口,描述部件的功能。在这里我们不需要考虑部件功能的实现细节,只需要遵循高内聚低耦合的特点划分部件,将各个部件的功能描述清楚就可以了。

关于部件的划分,在这里我主要遵循高小鹏老师的《计算机组成与实现》,单独设计了NPC组合逻辑部件,将求beq,jal等跳转指令的地址都放到这里来,我认为在设计单周期CPU时会显得更加清晰,不容易出错。

关于各个部件的命名规范,我稍后再提。

大概表头设计如下:

2.设计各条指令的数据通路,同时修正扩展第一步中相应模块的端口和功能。

在这里其实理论上可以建一个以指令为列各个部件端口为行的表格,但我最初是在word里画的,所以把他拆分成了各个部件。

表头列出单个部件的信号端口(输入端)和驱动源(其他部件的输出端),各条指令,我称之为数据综合表:

由图所示,表头设计好了,需要的做的只是按照每一条指令数据通路进行填空而已,在这个过程中,如果需要对部件端口功能进行修改扩展则及时修改扩展。

填表的过程就相当于在logisim中连线,这样就不要照着图就能设计出Verilog描述的CPU了。

注意:端口名称需要严格按照之前表格里的名称来写,方便后面verilog的描述。

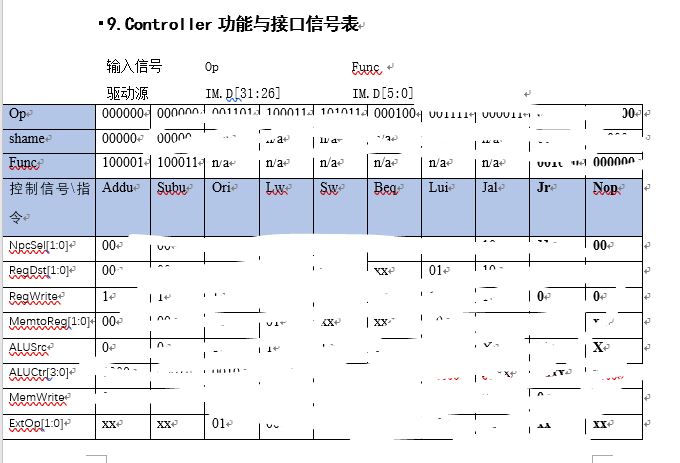

3.综合数据通路 初步构建Controller

如上表所示,综合数据通路的过程就是添加多路选择器以及描述控制器的过程。

四、构建Controller端口与功能表

直接上图,关注表头:

端口定义也可从图中获得。

4.利用上述端口与功能定义表使用Verilog描述各个部件和多路选择器(包括controller)

注意:实验中reset需要对所有时序部件(包括GRF DM PC进行同步复位,不包括IM);

理解:将CPU看成大型的有限状态机,复位代表保存的状态全部清零。

5.描述数据通路

利用设计的数据通路综合表,就能知道端口之间的连接关系。

用Verilog描述时,由于需要模块实例化,不同部件端口不能直接相连,必须使用wire型作为媒介,命名规范之后提。

6.测试程序

二、描述Controller的方法

我是采用assign赋值、和或逻辑,

或逻辑就是或门;和逻辑可以利用三目运算符从而代替直接描述logisim中的门级描述,避免出错。

例如 assign subu=(Op==6'b000000&&Func==6'b100011)?1:0;

至于if-else和case语句我觉得并没有更简单,宏定义我就想不到了,评论区可以指正完善我的思考题orz。

我的P4 Verilog的命名规范(尝试总结,试行版)大概率P5要修改

1.各部件端口定义与功能表

杜绝单纯的I O 等毫无意义千篇一律的设置。

在填写表格时,可以PC.DO 部件名+.+端口名

DO DI WD RD Addr 只要在表格中写清楚就好·····注意大小写

2.在写数据通路时,wire和各个部件的输出端口同名,从而确保CPU连接的正确性

PC.DO -> PCDO去掉.

特殊情况下须标注

3.多路选择器按顺序命名Mux1 Mux2 Mux3 实例化时改为M1 M2 M3

好像没有要强调的啊。。。。啊先这样吧

加油鸭!

P4-verilog实现mips单周期CPU的更多相关文章

- 使用Verilog搭建一个单周期CPU

使用Verilog搭建一个单周期CPU 搭建篇 总体结构 其实跟使用logisim搭建CPU基本一致,甚至更简单,因为完全可以照着logisim的电路图来写,各个模块和模块间的连接在logisim中非 ...

- Verilog hdl 实现单周期cpu

参考计组实验测试指令 - 简书,添加了一些细节. 1.添加 bne指令 修改 ctrl.v 之后修改mipstestloopjal_sim.asm,mars dump 为 bnetest. ...

- Verilog单周期CPU(未完待续)

单周期CPU:指令周期=CPU周期 Top模块作为数据通路 运算器中有ALU,通路寄存器(R1.R2.R3.R4),数据缓冲寄存器(鉴于书上的运算器只有R0)........... 此为ALU和通用寄 ...

- 单周期cpu设计代码解读

目录 写在前面 单周期cpu设计代码讲解 概念回顾 Verilog代码讲解 写在前面 欢迎转载,转载请说明出处. 单周期cpu设计代码讲解 概念回顾 一.电子计算机的部件 分为:中央处理器(cpu). ...

- 单周期CPU设计的理论基础

写在前面:本博客内容为本人老师原创,严禁任何形式的转载!本博客只允许放在博客园(.cnblogs.com),如果您在其他网站看到这篇博文,请通过下面这个唯一的合法链接转到原文! 本博客全网唯一合法UR ...

- 单周期CPU设计

终于有点时间了,恰好多周期的设计也已经完成,其实只想写写多周期的,无奈单周期补上才好,哈哈哈~ —————+—————黄金分割线—————+————— 首先要理解什么叫单周期CPU(与后面多周期CPU ...

- 为什么现在使用多周期CPU,而单周期CPU被弃用?

最初设计的CPU结构简单,内部不复杂.之所以制造它是为了让机器自动跑程序,算数. 早期CPU都是单周期的,人们没考虑那么多,性能啥的.就让CPU每个时钟周期跑一个指令,这些时钟周期等长.这样下来,有的 ...

- 单周期CPU

一个时钟周期执行一条指令的过程理解(单周期CPU): https://blog.csdn.net/a201577F0546/article/details/84726912 单周期CPU指的是一条指令 ...

- 使用logisim搭建单周期CPU与添加指令

使用logisim搭建单周期CPU与添加指令 搭建 总设计 借用高老板的图,我们只需要分别做出PC.NPC.IM.RF.EXT.ALU.DM.Controller模块即可,再按图连线,最后进行控制信号 ...

随机推荐

- thinkphp5框架笔记(ing)

重新整理下学习tp5手册的笔记.自己再好好看一次tp5的开发手册,学到哪里记到哪里. 0x01 安装 Composer安装 ThinkPHP5支持使用Composer安装 curl -sS https ...

- [NOIp2011] luogu P1311 选择客栈

我妈的抽象歌曲真 nb. 题目描述 给你 nnn 个点,每个点有两个参数 ci,dic_i,d_ici,di,给你一个数 DDD.定义一种方案合法,当且仅当你选出整数 i,j∈[1,n],i< ...

- php的cookie怎么使用

PHP中Cookie的使用---添加/更新/删除/获取Cookie 及 自动填写该用户的用户名和密码和判断是否第一次登陆 什么是cookie? 服务器在客户端保存用户的信息,比如登录名,密码等. 这些 ...

- 『嗨威说』算法设计与分析 - 动态规划思想小结(HDU 4283 You Are the One)

本文索引目录: 一.动态规划的基本思想 二.数字三角形.最大子段和(PTA)递归方程 三.一道区间动态规划题点拨升华动态规划思想 四.结对编程情况 一.动态规划的基本思想: 1.1 基本概念: 动态规 ...

- 开源造轮子:一个简洁,高效,轻量级,酷炫的不要不要的canvas粒子运动插件库

一:开篇 哈哈哈,感谢标题党的莅临~ 虽然标题有点夸张的感觉,但实际上,插件库确实是简洁,高效,轻量级,酷炫酷炫的咯.废话不多说,先来看个标配例子吧: (codepen在线演示编辑:http://co ...

- [AHOI2002]哈利·波特与魔法石

这道题比较简单,就是一个最短路(SSSP).数据水,用Floyd即可AC.这里用了Dijkstra. #include <iostream> #include <cstdio> ...

- 第五篇 Flask 中内置的 Session

Flask中的Session非常的奇怪,他会将你的SessionID存放在客户端的Cookie中,使用起来也非常的奇怪 1. Flask 中 session 是需要 secret_key 的 from ...

- Mybatis JdbcType与Oracle、MySql 数据类型对应关系

MyBatis 包含的jdbcType类型 ------------------------------------------------------------------------------ ...

- 关于RocketMQ消息消费与重平衡的一些问题探讨

其实最好的学习方式就是互相交流,最近也有跟网友讨论了一些关于 RocketMQ 消息拉取与重平衡的问题,我姑且在这里写下我的一些总结. ## 关于 push 模式下的消息循环拉取问题 之前发表了一篇关 ...

- Mybaits 源码解析 (九)----- 全网最详细,没有之一:一级缓存和二级缓存源码分析

像Mybatis.Hibernate这样的ORM框架,封装了JDBC的大部分操作,极大的简化了我们对数据库的操作. 在实际项目中,我们发现在一个事务中查询同样的语句两次的时候,第二次没有进行数据库查询 ...