基于Verilog的带FIFO输出缓冲的串口接收接口封装

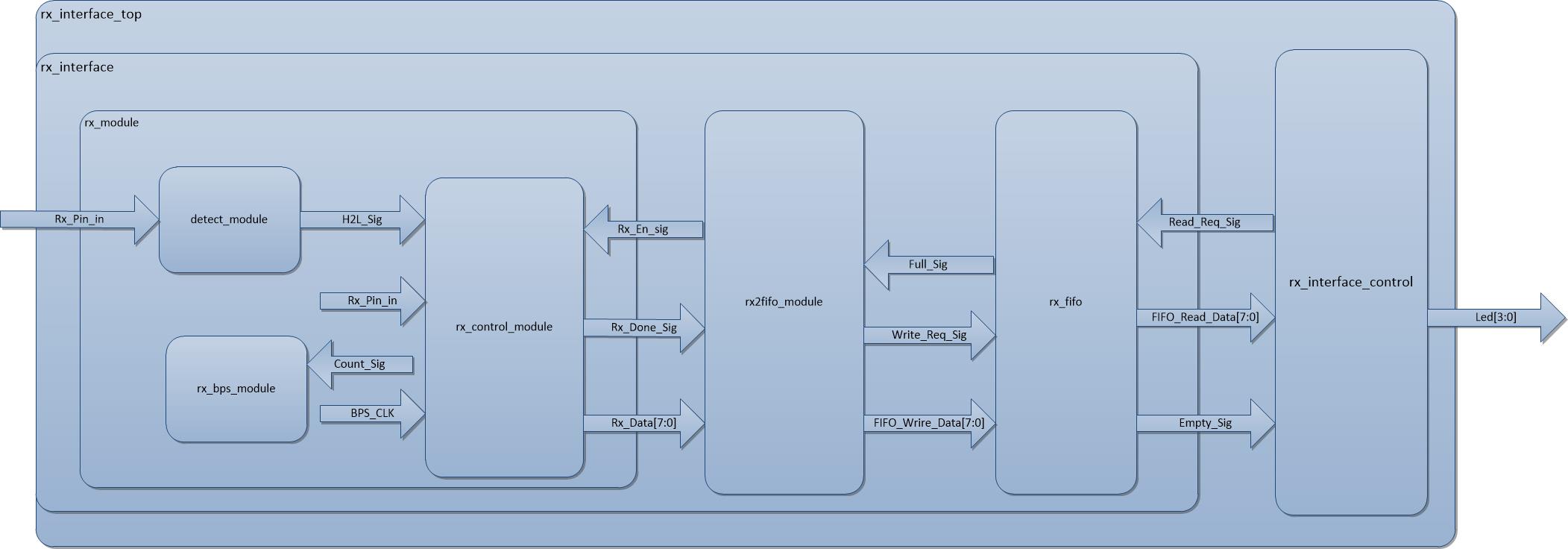

一、模块框图及基本思路

rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验”

rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能是不断接收并将数据写入rx_fifo

rx_interface:串口接收接口封装,也就是前两个模块的组合

rx_interface_control:串口接收接口控制模块,每隔1s读取一次串口rx_fifo,并将数据的低四位用Led显示出来

rx_interface_top:串口接收接口顶层模块

二、软件部分

detect_module:

module detect_module(

CLK,RSTn,

RX_Pin_in,

H2L_Sig

);

input CLK,RSTn;

input RX_Pin_in;

output H2L_Sig; /**********************************/

reg RX_r1;

reg RX_r2; always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

RX_r1<='b1;

RX_r2<='b1;

end

else

begin

RX_r1<=RX_Pin_in;

RX_r2<=RX_r1;

end

end

/*********************************/ assign H2L_Sig=RX_r2&(!RX_r1); endmodule

rx_bps_module:

module rx_bps_module #(parameter Baud=)(

CLK,RSTn,

Count_Sig,

BPS_CLK

);

input CLK;

input RSTn;

input Count_Sig;

output BPS_CLK; /***************************/

localparam Baud_Div=50_000_000/Baud-;

localparam Baud_Div2=Baud_Div/; reg[:] Count_BPS;

/*************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_BPS<='d0;

else if(Count_BPS==Baud_Div)

Count_BPS<='d0;

else if(Count_Sig)

Count_BPS<=Count_BPS+;

else Count_BPS<='d0;

end

/************************/

assign BPS_CLK=(Count_BPS==Baud_Div2)?'b1:1'b0;

endmodule

rx_control_module:

module rx_control_module(

CLK,RSTn,

H2L_Sig,BPS_CLK,RX_Pin_in,

Count_Sig,RX_En_Sig,RX_Done_Sig,RX_Data

); input CLK,RSTn;

input H2L_Sig,BPS_CLK,RX_En_Sig,RX_Pin_in;

output Count_Sig,RX_Done_Sig;

output [:] RX_Data; reg[:] i;

reg isCount;

reg isDone;

reg [:] rData;

/********************************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

i<='d0;

isCount<='b0;

isDone<='b0;

rData<='d0;

end

else if(RX_En_Sig)

begin

case(i)

'd0:if(H2L_Sig) begin i<=i+1'b1;isCount<='b1; end //接收到下降沿开始启动波特率计数

'd1:if(BPS_CLK) begin i<=i+1'b1; end //起始位

'd2,4'd3,'d4,4'd5,'d6,4'd7,'d8,4'd9:

if(BPS_CLK) begin rData[i-]<=RX_Pin_in;i<=i+'b1;end //数据位

'd10:if(BPS_CLK) begin i<=i+1'b1; end //校验位

'd11:if(BPS_CLK) begin i<=i+1'b1; end //停止位

'd12:if(BPS_CLK) begin i<=i+1'b1;isDone<='b1;isCount<=1'b0; end //一个时钟脉冲的 isDone 信号

'd13:begin i<=1'b0;isDone<='b0; end

endcase

end end /********************************************/

assign Count_Sig=isCount;

assign RX_Done_Sig=isDone;

assign RX_Data=rData; endmodule

rx_module:

module rx_module(

CLK,RSTn,

RX_Pin_in,RX_Done_Sig,RX_Data,RX_En_Sig

); input CLK,RSTn;

input RX_Pin_in,RX_En_Sig;

output RX_Done_Sig;

output [:] RX_Data; wire Count_Sig;

wire BPS_CLK;

wire H2L_Sig; rx_bps_module U0(

.CLK(CLK),.RSTn(RSTn),

.Count_Sig(Count_Sig),

.BPS_CLK(BPS_CLK)

); detect_module U1(

.CLK(CLK),.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.H2L_Sig(H2L_Sig)

); rx_control_module U2(

.CLK(CLK),.RSTn(RSTn),

.H2L_Sig(H2L_Sig),.BPS_CLK(BPS_CLK),.RX_Pin_in(RX_Pin_in),

.Count_Sig(Count_Sig),.RX_En_Sig(RX_En_Sig),.RX_Done_Sig(RX_Done_Sig),.RX_Data(RX_Data)

); endmodule

rx2fifo_module:

module rx2fifo_module(

CLK,RSTn,

RX_Done_Sig,RX_En_Sig,RX_Data,

Write_Req_Sig,FIFO_Write_Data,Full_Sig

);

input CLK,RSTn;

input RX_Done_Sig;

output RX_En_Sig;

input [:] RX_Data;

input Full_Sig;

output Write_Req_Sig;

output [:] FIFO_Write_Data; reg isRx;

reg isWrite;

reg [:] i;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

isRx<='b0;

isWrite<='b0;

i<='d0;

end

else

case(i)

'd0:if(RX_Done_Sig) begin i<=i+1'b1;isRx<='b0; end

else isRx<='b1;

'd1:if(!Full_Sig) begin isWrite<=1'b1;i<=i+'b1;end

'd2:begin isWrite<=1'b0;i<='d0;end

endcase end assign FIFO_Write_Data=RX_Data;

assign RX_En_Sig=isRx;

assign Write_Req_Sig=isWrite; endmodule

rx_interface:

module rx_interface(

CLK,RSTn,

RX_Pin_in,

Read_Req_Sig,Empty_Sig,FIFO_Read_Data

);

input CLK,RSTn;

input RX_Pin_in;

input Read_Req_Sig;

output Empty_Sig;

output [:] FIFO_Read_Data; wire RX_Done_Sig;

wire [:]RX_Data;

wire RX_En_Sig;

rx_module U0 (

.CLK(CLK),

.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.RX_Done_Sig(RX_Done_Sig),

.RX_Data(RX_Data),

.RX_En_Sig(RX_En_Sig)

); wire Write_Req_Sig;

wire Full_Sig;

wire [:]FIFO_Write_Data;

rx2fifo_module U1 (

.CLK(CLK),

.RSTn(RSTn),

.RX_Done_Sig(RX_Done_Sig),

.RX_En_Sig(RX_En_Sig),

.RX_Data(RX_Data),

.Write_Req_Sig(Write_Req_Sig),

.FIFO_Write_Data(FIFO_Write_Data),

.Full_Sig(Full_Sig)

);

rx_fifo U2 (

.clk(CLK), // input clk

.rst(!RSTn), // input rst

.din(FIFO_Write_Data), // input [7 : 0] din

.wr_en(Write_Req_Sig), // input wr_en

.rd_en(Read_Req_Sig), // input rd_en

.dout(FIFO_Read_Data), // output [7 : 0] dout

.full(Full_Sig), // output full

.empty(Empty_Sig) // output empty

); endmodule

rx_interface_control:

module rx_interface_control(

CLK,RSTn,

Read_Req_Sig,FIFO_Read_Data,Empty_Sig,

Led

);

input CLK,RSTn;

output Read_Req_Sig;

input [:] FIFO_Read_Data;

input Empty_Sig;

output [:]Led; /*******************************************/

localparam T1S=50_000_000-;

reg[:] Count_1s;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn) Count_1s<='d0;

else if(Count_1s==T1S) Count_1s<='d0;

else if(isCount) Count_1s<=Count_1s+'b1;

else Count_1s<='d0;

end

/*******************************************/

reg isRead;

reg [:]i;

reg isCount;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

isRead<='b0;

i<='d0;

isCount<='b0;

end

else

case(i)

'd0:if(Count_1s==T1S) begin isCount<=1'b0;i<=i+'b1; end

else isCount<='b1;

'd1:if(!Empty_Sig) begin isRead<=1'b1; i<=i+'b1;end

'd2:begin isRead<=1'b0;i<='d0; end

endcase

end

/*************************************************/

assign Read_Req_Sig=isRead;

assign Led=FIFO_Read_Data[:]; endmodule

rx_interface_top:

module rx_interface_top(

CLK,RSTn,RX_Pin_in,

Led

);

input RX_Pin_in;

input CLK,RSTn;

output [:]Led; wire Read_Req_Sig;

wire Empty_Sig;

wire[:] FIFO_Read_Data;

rx_interface U0 (

.CLK(CLK),

.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.Read_Req_Sig(Read_Req_Sig),

.Empty_Sig(Empty_Sig),

.FIFO_Read_Data(FIFO_Read_Data)

);

rx_interface_control U1 (

.CLK(CLK),

.RSTn(RSTn),

.Read_Req_Sig(Read_Req_Sig),

.FIFO_Read_Data(FIFO_Read_Data),

.Empty_Sig(Empty_Sig),

.Led(Led)

); endmodule

三、硬件部分

黑金SPARTAN-6开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3;

NET "RX_Pin_in" LOC = C11;

NET "Led[0]" LOC = P4;

NET "Led[1]" LOC = N5;

NET "Led[2]" LOC = P5;

NET "Led[3]" LOC = M6;

基于Verilog的带FIFO输出缓冲的串口接收接口封装的更多相关文章

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 基于Zabbix API文档二次开发与java接口封装

(继续贴一篇之前工作期间写的经验案例) 一. 案例背景 我负责开发过一个平台的监控报警模块,基于zabbix实现,需要对zabbix进行二次开发. Zabbix官方提供了Rest ...

- 基于Verilog的简单FIFO读写实验

一.模块框图及基本思路 fifo_ip:ISE生成的IP fifo_control:在fifo未满情况下不断写入递增的四位数,每隔1s读出一个数据驱动Led显示 fifo_top:前两个模块的组合 二 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 【转】分享两个基于MDK IDE的调试输出技巧

我们在STM32开发调试过程中,常常需要做些直观的输出,如果手头没有相关的设备或仪器,我们可以使用 IDE自带的工具.这里分享两个基于MDK IDE的调试输出技巧. 一.使用其自带的逻辑分析仪查看波 ...

- 基于Opencv自带BP网络的车标简易识别

代码地址如下:http://www.demodashi.com/demo/12966.html 记得把这几点描述好咯:代码实现过程 + 项目文件结构截图 + 演示效果 1.准备工作 1.1 训练集和测 ...

- PHP中的输出缓冲控制

在 PHP 中,我们直接进行 echo . 或者 print_r 的时候,输出的内容就会直接打印出来.但是,在某些情况下,我们并不想直接打印,这个时候就可以使用输出缓冲控制来进行输出打印的控制.当然, ...

随机推荐

- 使用Microsoft SyncToy 文件同步/备份 自动化处理

SyncToy 是由 微软 推出的一款免费的文件夹同步工具.百度搜索Microsoft SyncToy,官网可以直接下载 安装完成后 操作也非常简单,主要有三种模式 synchronize :在这个模 ...

- WDA基础十七:ALV不同行显示不同下拉

1.给ALV结构添加VALUE SET字段. 2.初始化时将TYPE_SET字段设置为值范围. METHOD wddoinit . DATA: lo_node TYPE REF TO if_wd_co ...

- JAVA写接口傻瓜($)教程(三)

接上一篇 补充:事实上java的类需要在src文件夹里写,classes文件夹只是会同步src文件夹里的类.如果在classes文件夹里操作java类,是会提示文件只读的.src文件夹中进行代码编写 ...

- vue做nav切换

话不多说,直接上代码. 关键:通过点击来改变thisindex ,又thisinde == index来控制class是否含active来控制样式 简单效果如下:

- linux命令-diff对比文件工具

diff 命令是 linux上非常重要的工具,用于比较文件的内容,特别是比较两个版本不同的文件以找到改动的地方.diff在命令行中打印每一个行的改动.最新版本的diff还支持二进制文件.diff程序的 ...

- C++标准模板库(STL)之Map

1.Map的常用用法 map:映射.可以将任何基本类型,结构体,STL容器映射到任何基本类型包括容器. 使用map,需要加map的头文件,#include<map>和using names ...

- linux常用命令 cut字符截取命令

cut 字符截取 cut [选项] 文件名 选项 -f 列号: 提取第几列 -d 分割符:按照指定的分隔符分割列 默认使用制表符("tab")进行分割 ssgao:Download ...

- BAT面试官告诉你如何回答你的职业规划

前言(Why) 在面试中不论是在一面二面三面这种技术面,还是在最后的hr面,经常会被人问及,"谈谈你的职业规划"这种问题,我们回答的很可能会给我们的面试表现加分,如果回答地不好,对 ...

- 第4天:scipy库

一.SciPy库概述 1.numpy提供向量和矩阵的相关操作,高级计算器 2.SciPy在统计.优化.插值.数值积分.视频转换等,涵盖基础科学计算相关问题. (额,对统计和概率,数理完全一窍不通) 3 ...

- !/usr/bin/env python和!/usr/bin/python的区别

脚本语言第一行 作用:文件中代码用指定可执行程序运行 #!/usr/bin/Python 执行脚本时,调用/usr/bin下python解释器 #!/usr/bin/env python 在环境设 ...