基于Verilog的带FIFO输出缓冲的串口接收接口封装

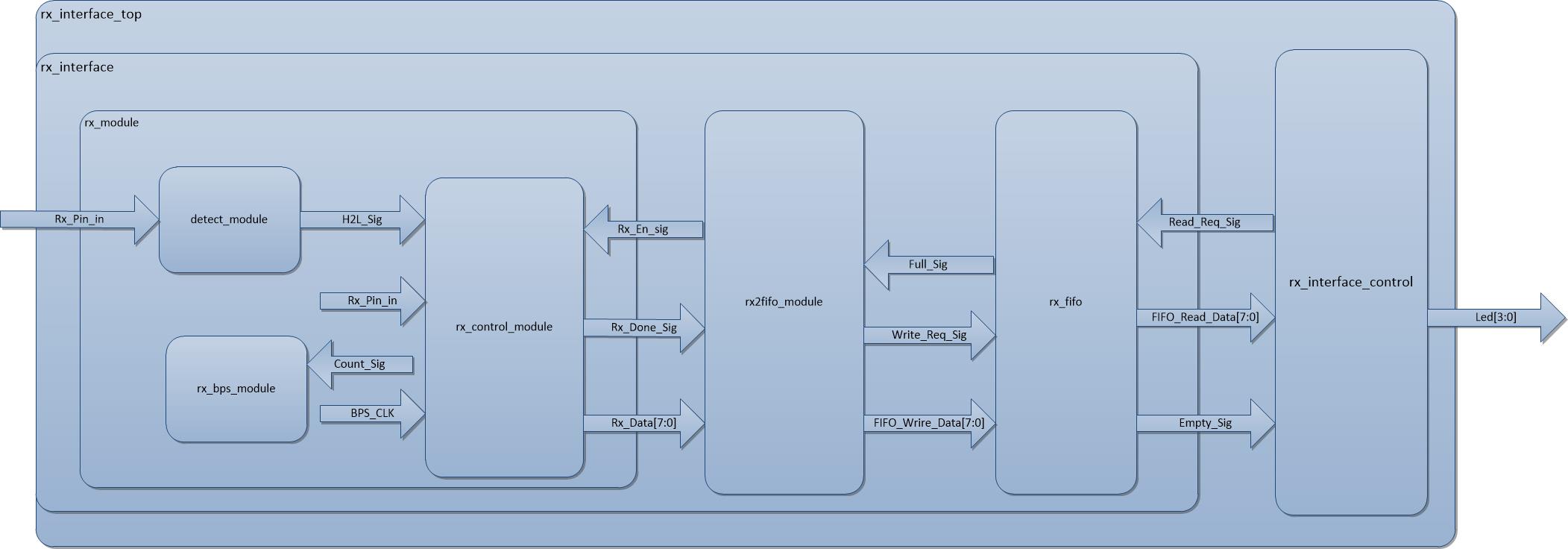

一、模块框图及基本思路

rx_module:串口接收的核心模块,详细介绍请见“基于Verilog的串口接收实验”

rx2fifo_module:rx_module与rx_fifo之间的控制模块,其功能是不断接收并将数据写入rx_fifo

rx_interface:串口接收接口封装,也就是前两个模块的组合

rx_interface_control:串口接收接口控制模块,每隔1s读取一次串口rx_fifo,并将数据的低四位用Led显示出来

rx_interface_top:串口接收接口顶层模块

二、软件部分

detect_module:

module detect_module(

CLK,RSTn,

RX_Pin_in,

H2L_Sig

);

input CLK,RSTn;

input RX_Pin_in;

output H2L_Sig; /**********************************/

reg RX_r1;

reg RX_r2; always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

RX_r1<='b1;

RX_r2<='b1;

end

else

begin

RX_r1<=RX_Pin_in;

RX_r2<=RX_r1;

end

end

/*********************************/ assign H2L_Sig=RX_r2&(!RX_r1); endmodule

rx_bps_module:

module rx_bps_module #(parameter Baud=)(

CLK,RSTn,

Count_Sig,

BPS_CLK

);

input CLK;

input RSTn;

input Count_Sig;

output BPS_CLK; /***************************/

localparam Baud_Div=50_000_000/Baud-;

localparam Baud_Div2=Baud_Div/; reg[:] Count_BPS;

/*************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

Count_BPS<='d0;

else if(Count_BPS==Baud_Div)

Count_BPS<='d0;

else if(Count_Sig)

Count_BPS<=Count_BPS+;

else Count_BPS<='d0;

end

/************************/

assign BPS_CLK=(Count_BPS==Baud_Div2)?'b1:1'b0;

endmodule

rx_control_module:

module rx_control_module(

CLK,RSTn,

H2L_Sig,BPS_CLK,RX_Pin_in,

Count_Sig,RX_En_Sig,RX_Done_Sig,RX_Data

); input CLK,RSTn;

input H2L_Sig,BPS_CLK,RX_En_Sig,RX_Pin_in;

output Count_Sig,RX_Done_Sig;

output [:] RX_Data; reg[:] i;

reg isCount;

reg isDone;

reg [:] rData;

/********************************************/

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

i<='d0;

isCount<='b0;

isDone<='b0;

rData<='d0;

end

else if(RX_En_Sig)

begin

case(i)

'd0:if(H2L_Sig) begin i<=i+1'b1;isCount<='b1; end //接收到下降沿开始启动波特率计数

'd1:if(BPS_CLK) begin i<=i+1'b1; end //起始位

'd2,4'd3,'d4,4'd5,'d6,4'd7,'d8,4'd9:

if(BPS_CLK) begin rData[i-]<=RX_Pin_in;i<=i+'b1;end //数据位

'd10:if(BPS_CLK) begin i<=i+1'b1; end //校验位

'd11:if(BPS_CLK) begin i<=i+1'b1; end //停止位

'd12:if(BPS_CLK) begin i<=i+1'b1;isDone<='b1;isCount<=1'b0; end //一个时钟脉冲的 isDone 信号

'd13:begin i<=1'b0;isDone<='b0; end

endcase

end end /********************************************/

assign Count_Sig=isCount;

assign RX_Done_Sig=isDone;

assign RX_Data=rData; endmodule

rx_module:

module rx_module(

CLK,RSTn,

RX_Pin_in,RX_Done_Sig,RX_Data,RX_En_Sig

); input CLK,RSTn;

input RX_Pin_in,RX_En_Sig;

output RX_Done_Sig;

output [:] RX_Data; wire Count_Sig;

wire BPS_CLK;

wire H2L_Sig; rx_bps_module U0(

.CLK(CLK),.RSTn(RSTn),

.Count_Sig(Count_Sig),

.BPS_CLK(BPS_CLK)

); detect_module U1(

.CLK(CLK),.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.H2L_Sig(H2L_Sig)

); rx_control_module U2(

.CLK(CLK),.RSTn(RSTn),

.H2L_Sig(H2L_Sig),.BPS_CLK(BPS_CLK),.RX_Pin_in(RX_Pin_in),

.Count_Sig(Count_Sig),.RX_En_Sig(RX_En_Sig),.RX_Done_Sig(RX_Done_Sig),.RX_Data(RX_Data)

); endmodule

rx2fifo_module:

module rx2fifo_module(

CLK,RSTn,

RX_Done_Sig,RX_En_Sig,RX_Data,

Write_Req_Sig,FIFO_Write_Data,Full_Sig

);

input CLK,RSTn;

input RX_Done_Sig;

output RX_En_Sig;

input [:] RX_Data;

input Full_Sig;

output Write_Req_Sig;

output [:] FIFO_Write_Data; reg isRx;

reg isWrite;

reg [:] i;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

isRx<='b0;

isWrite<='b0;

i<='d0;

end

else

case(i)

'd0:if(RX_Done_Sig) begin i<=i+1'b1;isRx<='b0; end

else isRx<='b1;

'd1:if(!Full_Sig) begin isWrite<=1'b1;i<=i+'b1;end

'd2:begin isWrite<=1'b0;i<='d0;end

endcase end assign FIFO_Write_Data=RX_Data;

assign RX_En_Sig=isRx;

assign Write_Req_Sig=isWrite; endmodule

rx_interface:

module rx_interface(

CLK,RSTn,

RX_Pin_in,

Read_Req_Sig,Empty_Sig,FIFO_Read_Data

);

input CLK,RSTn;

input RX_Pin_in;

input Read_Req_Sig;

output Empty_Sig;

output [:] FIFO_Read_Data; wire RX_Done_Sig;

wire [:]RX_Data;

wire RX_En_Sig;

rx_module U0 (

.CLK(CLK),

.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.RX_Done_Sig(RX_Done_Sig),

.RX_Data(RX_Data),

.RX_En_Sig(RX_En_Sig)

); wire Write_Req_Sig;

wire Full_Sig;

wire [:]FIFO_Write_Data;

rx2fifo_module U1 (

.CLK(CLK),

.RSTn(RSTn),

.RX_Done_Sig(RX_Done_Sig),

.RX_En_Sig(RX_En_Sig),

.RX_Data(RX_Data),

.Write_Req_Sig(Write_Req_Sig),

.FIFO_Write_Data(FIFO_Write_Data),

.Full_Sig(Full_Sig)

);

rx_fifo U2 (

.clk(CLK), // input clk

.rst(!RSTn), // input rst

.din(FIFO_Write_Data), // input [7 : 0] din

.wr_en(Write_Req_Sig), // input wr_en

.rd_en(Read_Req_Sig), // input rd_en

.dout(FIFO_Read_Data), // output [7 : 0] dout

.full(Full_Sig), // output full

.empty(Empty_Sig) // output empty

); endmodule

rx_interface_control:

module rx_interface_control(

CLK,RSTn,

Read_Req_Sig,FIFO_Read_Data,Empty_Sig,

Led

);

input CLK,RSTn;

output Read_Req_Sig;

input [:] FIFO_Read_Data;

input Empty_Sig;

output [:]Led; /*******************************************/

localparam T1S=50_000_000-;

reg[:] Count_1s;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn) Count_1s<='d0;

else if(Count_1s==T1S) Count_1s<='d0;

else if(isCount) Count_1s<=Count_1s+'b1;

else Count_1s<='d0;

end

/*******************************************/

reg isRead;

reg [:]i;

reg isCount;

always @(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

isRead<='b0;

i<='d0;

isCount<='b0;

end

else

case(i)

'd0:if(Count_1s==T1S) begin isCount<=1'b0;i<=i+'b1; end

else isCount<='b1;

'd1:if(!Empty_Sig) begin isRead<=1'b1; i<=i+'b1;end

'd2:begin isRead<=1'b0;i<='d0; end

endcase

end

/*************************************************/

assign Read_Req_Sig=isRead;

assign Led=FIFO_Read_Data[:]; endmodule

rx_interface_top:

module rx_interface_top(

CLK,RSTn,RX_Pin_in,

Led

);

input RX_Pin_in;

input CLK,RSTn;

output [:]Led; wire Read_Req_Sig;

wire Empty_Sig;

wire[:] FIFO_Read_Data;

rx_interface U0 (

.CLK(CLK),

.RSTn(RSTn),

.RX_Pin_in(RX_Pin_in),

.Read_Req_Sig(Read_Req_Sig),

.Empty_Sig(Empty_Sig),

.FIFO_Read_Data(FIFO_Read_Data)

);

rx_interface_control U1 (

.CLK(CLK),

.RSTn(RSTn),

.Read_Req_Sig(Read_Req_Sig),

.FIFO_Read_Data(FIFO_Read_Data),

.Empty_Sig(Empty_Sig),

.Led(Led)

); endmodule

三、硬件部分

黑金SPARTAN-6开发板

NET "CLK" LOC = T8;

NET "RSTn" LOC = L3;

NET "RX_Pin_in" LOC = C11;

NET "Led[0]" LOC = P4;

NET "Led[1]" LOC = N5;

NET "Led[2]" LOC = P5;

NET "Led[3]" LOC = M6;

基于Verilog的带FIFO输出缓冲的串口接收接口封装的更多相关文章

- 基于Verilog的带FIFO写入缓冲的串口发送接口封装

一.模块框图及基本思路 tx_module:串口发送的核心模块,详细介绍请参照前面的“基于Verilog的串口发送实验” fifo2tx_module:当fifo不为空时,读取fifo中的数据并使能发 ...

- 基于Zabbix API文档二次开发与java接口封装

(继续贴一篇之前工作期间写的经验案例) 一. 案例背景 我负责开发过一个平台的监控报警模块,基于zabbix实现,需要对zabbix进行二次开发. Zabbix官方提供了Rest ...

- 基于Verilog的简单FIFO读写实验

一.模块框图及基本思路 fifo_ip:ISE生成的IP fifo_control:在fifo未满情况下不断写入递增的四位数,每隔1s读出一个数据驱动Led显示 fifo_top:前两个模块的组合 二 ...

- 基于Verilog的奇数偶数小数分频器设计

今天呢,由泡泡鱼工作室发布的微信公共号“硬件为王”(微信号:king_hardware)正式上线啦,关注有惊喜哦.在这个普天同庆的美好日子里,小编脑洞大开,决定写一首诗赞美一下我们背后伟大的团队,虽然 ...

- 基于Verilog HDL整数乘法器设计与仿真验证

基于Verilog HDL整数乘法器设计与仿真验证 1.预备知识 整数分为短整数,中整数,长整数,本文只涉及到短整数.短整数:占用一个字节空间,8位,其中最高位为符号位(最高位为1表示为负数,最高位为 ...

- 基于Verilog HDL 的数字时钟设计

基于Verilog HDL的数字时钟设计 一.实验内容: 利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能.时间设置由开关S1和S2控制,分别是增和减.开关S3是模式选择:0是正常时钟 ...

- 【转】分享两个基于MDK IDE的调试输出技巧

我们在STM32开发调试过程中,常常需要做些直观的输出,如果手头没有相关的设备或仪器,我们可以使用 IDE自带的工具.这里分享两个基于MDK IDE的调试输出技巧. 一.使用其自带的逻辑分析仪查看波 ...

- 基于Opencv自带BP网络的车标简易识别

代码地址如下:http://www.demodashi.com/demo/12966.html 记得把这几点描述好咯:代码实现过程 + 项目文件结构截图 + 演示效果 1.准备工作 1.1 训练集和测 ...

- PHP中的输出缓冲控制

在 PHP 中,我们直接进行 echo . 或者 print_r 的时候,输出的内容就会直接打印出来.但是,在某些情况下,我们并不想直接打印,这个时候就可以使用输出缓冲控制来进行输出打印的控制.当然, ...

随机推荐

- 在Mac os 10.11 下编译Berkeley caffe

安装各种补丁和组件,缺啥装啥. python 采用 2.7.13 最新版. 安装工具 homebrew , pip 很繁琐,但是没难度. 由于本人macbook pro不支持CUDA,所以不用安装. ...

- 用node.js启动mock.js

Node.js Node 是一个让 JavaScript 运行在服务端的开发平台,它让 JavaScript 成为与PHP.Python.Perl.Ruby 等服务端语言平起平坐的脚本语言.官网下载n ...

- PHP的json_encode()函数与JSON对象

一.问题描述 这周搬砖的时候,前端通过ajax获取后端的数据后,照例用 对象.属性 的方式取值,然而结果总是总是不能如预期般展示在页面上. 先写个 demo 还原下场景:选中一个下拉框列表选项后,会在 ...

- Kafka 1.0.0集群安装

环境 主机名 IP 地址 安装路径 系统 sht-sgmhadoopdn-01 172.16.101.58 /opt/kafka_2.12-1.0.0 /opt/kafka(软连接) CentOS L ...

- EAP-MD5计算方法

一.说明 领导要求确认设备进行802.1X认证时,是否直接将用户名密码明文传给交换机.配好端口镜像.搭好Radius环境后进行了抓包分析. 二.计算 2.1 802.1X认证过程 完整流程如下: 客户 ...

- PROJ.4学习——地图投影

PROJ.4学习——地图投影(坐标系投影) 前言 PROJ是由大量的基础投影库构成.这里主要讨论学习PROJ库的相关参数. 这里大部分是讲如何将3D坐标系投影到2D平面上.投影时,涉及到基准线,单位, ...

- C++学习笔记:多态篇之虚函数

一.类型 在引入多态之前,我们先来看一下多态的两种类型: 二.多态性的概念 多态一词最初来源于希腊语,意思是具有多种形式或形态的情形,在C++中是指同样的消息被不同类型的对象接收时导致不同的行为,这里 ...

- 5ci

- Python爬虫入门之正则表达式

在前面我们已经搞定了怎样获取页面的内容,不过还差一步,这么多杂乱的代码夹杂文字我们怎样把它提取出来整理呢?下面就开始介绍一个十分强大的工具,正则表达式! 1.了解正则表达式 正则表达式是对字符串操作的 ...

- 【转载】 [unreal4入门系列之七] UE4中的Actor类和Pawn类

原文地址: http://www.52vr.com/article-558-1.html 现在我们开始进入UE4的代码开发工作.首先,UE4的类框架是非常庞大的,看起来有点让人措手不及.不过正因为UE ...