Verilog中的时间尺度与延迟

- 赋值延时分类:

- 根据信号类型可分为连续赋值延时和寄存器赋值延时,

- 根据延迟特性分为内部延迟和外部延迟

- 连续赋值时延:一般可分为普通赋值时延、隐式时延、声明时延;只有 外部时延。

- 寄存器赋值延时:只有在使用时可分为内部时延 和 外部时延, 但没有声明延时。

- 普通赋值时延

- 隐式延时声明:

- 变量声明延时

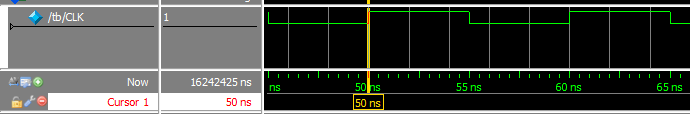

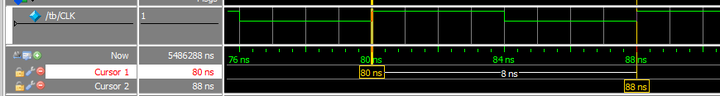

- 惯性延迟

Verilog中的时间尺度与延迟的更多相关文章

- system verilog中的跳转操作

在verilog中,使用disable声明来从执行流程中的某一点跳转到另一点.特别地,disable声明使执行流程跳转到标注名字的声明组末尾,或者一个任务的末尾. verilog中的disable命令 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- 一段比较有意思的代码——介绍system verilog中的新增幅值语句

system verilog中新加了很多幅值语句,虽然都只适用于阻塞幅值,但是在某些场合中非常实用. 下面是一段有意思的代码,覆盖了一些用法. package definitions; typedef ...

- GCD中使用dispatch_after函数延迟处理任务

在实际的开发中,经常会遇到想要在指定的时间间隔后执行某个处理 <一>在GCD中提供了dispatch_after函数来完成这一操作 dispatch_after(dispatch_time ...

- 关于verilog中if与case语句不完整产生锁存器的问题 分类: FPGA 2014-11-08 17:39 260人阅读 评论(0) 收藏

在很多地方都能看到,verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因. 一,什么是锁存器?锁存器与触发器 ...

- 关于Verilog 中的for语句的探讨

在C语言中,经常用到for循环语句,但在硬件描述语言中for语句的使用较C语言等软件描述语言有较大的区别. 在Verilog中除了在Testbench(仿真测试激励)中使用for循环语句外,在Test ...

- Verilog中锁存器与多路选择器

Verilog中锁存器与多路选择器 Verilog是一种硬件描述语言,它代表的是硬件. Verilog代表的就是逻辑门和连接线. 对于一个always@(*)控制的块而言,只要块中的表达式包含的任意的 ...

- verilog中always块延时总结

在上一篇博文中 verilog中连续性赋值中的延时中对assign的延时做了讨论,现在对always块中的延时做一个讨论. 观测下面的程序,@0时刻,输入的数据分别是0x13,0x14 . @2时刻, ...

- verilog中读取文件中的字符串_modelsim高级仿真

今天给个程序大家玩玩.因为今天遇到一个问题,就是要向UART发送指令,指令非常多,都是字符串.一直copy 函数 UART ("COMM_1"); UART ("COM ...

- verilog中的有符号数运算

verilog中的有符号数运算 http://hi.baidu.com/lixu1113/item/d00dc095f86aed48f142159a verilog中的有符号数运算 有符号数的计算:若 ...

随机推荐

- ADC多通道采样DMA传输模板

void MyADC_Init(void){ ADC_InitTypeDef ADC_InitStructure; GPIO_InitTypeDef GPIO_InitStructure; DMA_I ...

- OSPF配置常用命令知识总结

OSPF配置常用命令知识总结 1.display ospf abr-asbr 命令用来显示OSPF的区域边界路由器和自治系统边界路由器信息. [R3]dis ospf abr-asbr OSPF Pr ...

- 怎么在CAD表格中画斜线?CAD表格斜线一分为二绘制步骤

在Excel表格中经常能看到用一条斜线将单元格一分为二,那么,你知道怎么在CAD表格中画斜线吗?本文小编就以浩辰CAD软件为例来给大家分享一下CAD表格斜线一分为二的绘制步骤,一起来看看吧! CAD表 ...

- es 部署 进程、文件数 配置

1. /etc/security/limits.conf elasticsearch soft nofile 65536 elasticsearch hard nofile 65536 elasti ...

- taobao.tbk.sc.newuser.order.get( 淘宝客-服务商-新用户订单明细查询 )

淘宝客订单表结构设计(mysql) CREATE TABLE `tbk_order` ( `id` bigint(20) NOT NULL AUTO_INCREMENT, `member_id` bi ...

- git通过ssh方式免密克隆代码仓库

git上添加ssh公钥 略过 终端命令行 格式: git clone ssh://[user@]host.xz[:port]/path/to/repo.git/ 栗子: git clone ssh:/ ...

- Webservice EASLogin登录接口说明

https://club.kingdee.com/forum.php?mod=viewthread&tid=1332944

- iOS底层原理02-alloc源码分析

首先,从最熟悉的入手 - 对象,看看这三个对象的内容,内存地址和指针地址. LGPerson *p1 = [LGPerson alloc]; LGPerson *p2 = [p1 init]; ...

- QTreeWidget CSS样式

QTreeWidget{ font: 13pt "楷体"; color: rgb(26, 202, 255); border:1px solid rgb(170, 170, 127 ...

- linux改变用户属主

将test文件的属主改为root:sudo chown root test 改变所在组:sudo chgrp root test 同时改变属主和所在组:sudo chown root.root tes ...