基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计

成果展示(优酷视频):

视频: 基于FPGA的VGA显示技术(手机控制)

http://v.youku.com/v_show/id_XNjk4ODE3ODUy.html

视频: 基于FPGA和Labview上位机的VGA显示技术

http://v.youku.com/v_show/id_XNjk4ODE4ODg4.html

1. 实验目标

初步了解FPGA,希望能够做到以下两点:

(1)使用Labview上位机控制VGA显示;

(2)使用手机控制VGA显示。

2. 开发板简介

实验所使用的开发板是Cyclone II系列的黑金开发板,主要是因为笔记本只有USB接口,只能使用USB Blaster进行程序的下载调试。

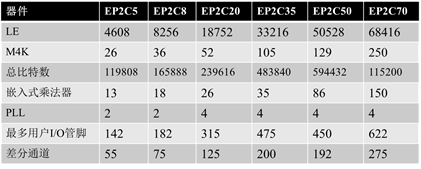

Cyclone II系列器件是Altera低成本Cyclone系列的第二代产品,Cyclone II FPGA的成本比第一代Cyclone 器件低30%,逻辑容量大3倍多。Cyclone II器件采用TSMC经验证的90nm低K绝缘材料工艺技术,是业界成本最低的FPGA。Cyclone II通过使用新型的架构,缩小裸片尺寸,在保证成本优势的前提下提供了更高的集成度和性能。

Cyclone II系列的主要特点:

- 高效率的芯片结构支持从4608LE到68416LE的集成度。

- 包含内部嵌入式乘法器,支持DSP运算。

- 先进的I/O,支持PCI,DDR,DDR2等多种接口。

- 全局时钟管理及嵌入式锁相环。

- 支持Altera IP Core 及Nios II 嵌入式处理器。

Cyclone II系列芯片比较:

3. VGA协议

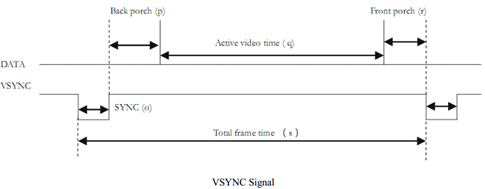

VGA 协议主要由 5 个输入信号组成,亦是 HSYNC Signal, VSYNC Signal, RGB Signal。说简单一点, HSYNC Signal 是 "列同步信号" , VSYNC Signal 是 "行同步信号" , RGB Signal 是"红色-绿色-蓝色

颜色信号" 。

VGA 的扫描是固定的。一帧的屏幕是由"m 行扫描"和"n 列填充"组成。假设以 800x 600 x 60Hz 为例的显示标准 ( 800 宽 x 600 高 x 60Hz ),

那么宏观上它有 600 行和 800 列为一行。

VGA时序图:

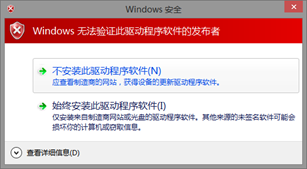

以 800 x 600 x 60Hz 为例,像素信息如下:

4. 串口模块:

在用手机控制VGA显示的时候,需要将手机和FPGA通过蓝牙进行通信。本实验使用的是一个蓝牙模块,通信协议定义如表所示:

|

编号 |

符号 |

引脚说明 |

|

1 |

5V |

蓝牙模块电源 |

|

2 |

TX |

蓝牙模块接收 |

|

3 |

RX |

蓝牙模块发送 |

|

4 |

GND |

蓝牙模块地 |

|

5 |

RST |

复位引脚 |

|

6 |

AT |

蓝牙模块设置引脚 |

5. 遇到的问题

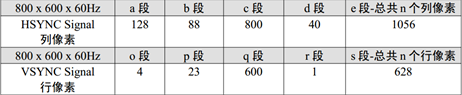

本实验遇到的最大的问题就是USB BLASTER的驱动安装。这是因为win8在安装驱动的时候,如果驱动没有数字签名认证信息,会强制禁止安装。解决方法是通过更改启动项设置,使得系统能够安装驱动。但是经过实际调试,发现驱动安装成功后,下一次开机驱动会失效,需要重新安装。驱动安装过程如下图:

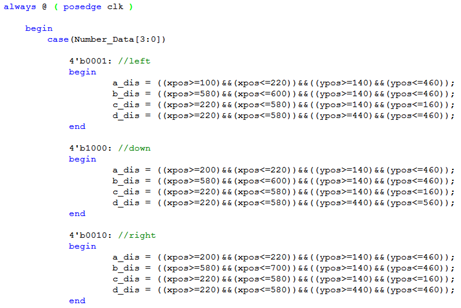

6. 部分FPGA程序

7. 手机APP开发

手机的APP开发使用的是APP INVENTOR工具,它能够网页在线编程Android程序。手机界面如下图所示:

8. Labview上位机

同时还开发了基于Labview的上位机,也可以通过控制FPGA来控制VGA的显示。上位机的运行界面以及部分程序如下:

9. 总结

通过这次实验,学会了初步使用和调试FPGA,对Verilog以及串口等程序有了初步了解。

基于FPGA的VGA显示实验设计的更多相关文章

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

- 基于FPGA驱动VGA显示图片的小问题

学习VGA显示图片的过程中,遇到了一个小问题,我在显示屏上开了一个60x60的框,放了一张图片进去显示,但是最终的结果如下图所示. 出现了一个竖黑边,看了看代码,分析了一下逻辑没问题,然而看这个显示那 ...

- 基于FPGA的HDMI显示设计(三)

上一篇:基于FPGA的VGA显示设计(二) 10月10日 ~ 20日期间实习,令我万万没想到的是实习题目是 “便携式高清电视显示屏测试系统原型设计” 也就是 “基于FPGA的视频显示”. 实习要求用 ...

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- [置顶]

基于FPGA的VGA简易显存设计&NIOS ii软核接入

项目简介 本项目基于Altera公司的Cyclone IV型芯片,利用NIOS II软核,2-port RAM与时序控制模块,实现64*48分辨率的显存(再大的显存板载资源m9k不够用) 实现效果如下 ...

- FPGA驱动VGA显示静态图片

一 .前言 本文设计思想采用明德扬至简设计法.VGA是最常见的视频显示接口,时序也较为简单.本文从利用显示屏通过VGA方式显示测试图案及静态图片着手带大家接触图像显示应用,算是为后续VGA显示摄像头采 ...

- 基于fpga的vga学习(3)

本次学习如何通过vga发送数字.文字.字母, 首先利用建模软件,将想要发送的数据通过数学建模转换,这里我用的软件是PCtoLCD,具体效果如下 这里可以看出,建模将数据装换成0和1,一个字母用16x8 ...

随机推荐

- Java学习的第十九天

1.今天学了接口只能有抽象的常量和方法,接口为interface 承接接口是implements 接口的使用 接口中的方法必须是抽象的,没有构造方法 2.今天没有问题 3.明天学习第六章综合实例 ...

- 使用scrapy框架模拟登录

scrapy模拟登录 注意:模拟登陆时,必须保证settings.py里的COOKIES_ENABLED(Cookies中间件) 处于开启状态 COOKIES_ENABLED = True 或# CO ...

- redhat 7.4从openssh7.6离线升级openssh8.4p1解决方法

具体需求 这几天生产环境服务器又进行了安全扫描,每次都会报一下漏洞错误.虽然只有一个高危问题,但是每次看到ssh远程漏洞都很烧脑 "主要是里面坑太多了",闲话就不说了,今天我们来看 ...

- numpy矩阵

一.创建矩阵 Numpy提供了ndarray来进行矩阵的操作,在Numpy中 矩阵继承于NumPy中的二维数组对象,但矩阵区别于数组,不可共用数组的运算规律. 1.mat("第0行:第1行: ...

- 18、Celery

Celery 1.什么是Clelery Celery是一个简单.灵活且可靠的,处理大量消息的分布式系统 专注于实时处理的异步任务队列 同时也支持任务调度 Celery架构 Celery的架构由三部分组 ...

- Spider_基础总结3_BeautifulSoup对象+find()+find_all()

# 本节内容: # 解析复杂的 HTML网页: # 1--bs.find() bs.find_all() tag.get_text() # find_all(tag/tag_list,attribut ...

- 第05组 Alpha冲刺 (1/6)

.th1 { font-family: 黑体; font-size: 25px; color: rgba(0, 0, 255, 1) } #ka { margin-top: 50px } .aaa11 ...

- 面试官:Redis 主从复制时网络开小差了怎么整?

上周因为实在太忙就认认真真写了一篇水文,吹了一下自己过去的经历,反响竟然超出了我的预期,并且后台还有读者留言表示想看续集的.哈哈,果然大家还是对水文更有热情. 这期我们继续回到之前的 Redis 话题 ...

- C++编程基础练习,入门必备练手

练习1,1 从一个简单程序开始 1,将string头文件注释掉,重新编译这个程序,会发生什么事? 目前还没有发现会发生什么事. 2,将using namespace std注释掉,重新编译,会发生什么 ...

- 使用Ganglia监控系统监控集群(debian)

ganglia是一个集群监控软件,底层使用RRDTool获得数据. Ganglia分为ganglia-monitor和gmetad两部分,前者运行在集群每个节点上(被监控机器)收集RRDTool产生的 ...