FPGA中改善时序性能的方法_advanced FPGA design

本文内容摘自《advanced FPGA design》对应中文版是 《高级FPGA设计,结构,实现,和优化》第一章中的内容

FPGA中改善时序,我相信也是大家最关心的话题之一,在这本书中列举了一些方法供给大家参考。

1,插入寄存器(Add Register Layers),在中文版中被翻译成:添加寄存器层次。即,在关键路径中插入寄存器。

这种方式会增加设计的时滞(clock latency)。插入了几个寄存器,结果输出就会延长几个周期,在不违反设计规格(对clock latency有要求)以及功能没有影响的时滞情况之下可以这么做。

2,并行结构。把串行改成并行。最典型的就是乘法器了。

作为一个16bit的乘法器,最省资源的就是等待16个clock出结果,也可以是设计成面积最大但是出来结果速度最快的,只需要一个周期就可以出来结果。

3,逻辑展开(Flatten Logic Structures)。中文版同样翻译的很保守:展平逻辑结构。

仔细看了看,觉得里面应该包含了连个知识点。第一是逻辑复制,特别是针对大扇出(详情在altera的官方视频资料中有提到),通常使用generate或者是在综合器中设定。第二个是消除代码中的优先级。这里需要多说一句:现在的工具很智能,就算你写成if else 有优先级的结构,有时候也能综合出并行结构。如果并行也符合你的设计要求,为了安全起见,最好还是写成case这种并行结构比较好。

4,寄存器平衡 (Register Balancing)。

寄存器平衡就是在你的关键路径中移动你的寄存器。第一就是你手动移动 —— 改代码。第二就是设定综合器让它自己移动 —— 不到万不得已不这么干,因为这么多导致代码移植性变差。

5,路径重组

这是最有意思的一个方法,也是体现你的设计水平的方式。结果书中给出的例子确实让我惊讶了一下。为啥呢,先贴出代码

第一版:

module randomlogic_1(

output reg [:] Out,

input [:] A, B, C,

input clk,

input Cond1, Cond2);

always @(posedge clk)

if(Cond1)

Out <= A;

else if(Cond2 && (C < ))

Out <= B;

else

Out <= C;

endmodule

第二版:

module randomlogic_2(

output reg [:] Out,

input [:] A, B, C,

input clk,

input Cond1, Cond2); wire CondB = (Cond2 & !Cond1); always @(posedge clk)

if(CondB && (C < ))

Out <= B;

else if(Cond1)

Out <= A;

else

Out <= C;

endmodule

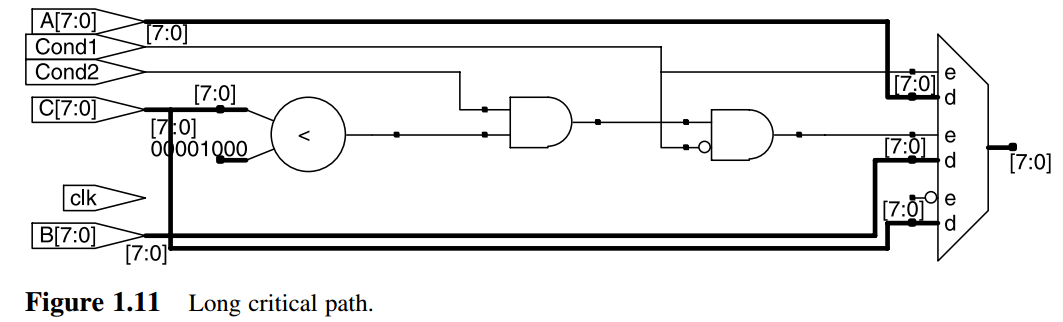

从代码上来看2版好像还比第一版路径更长,因为 out <= B,的路径从 Cond2 && (C < 8) 变成了 (Cond2 & !Cond1) && (C < 8)。似乎还变长了,怎么叫优化了呢?实际上,如果我们不看下面的图,自己模仿RTL Viewer,发现2版的关键路径真的比1短。书中给出的图示也是如此,这是第一版的视图,关键路径经历了4个器件

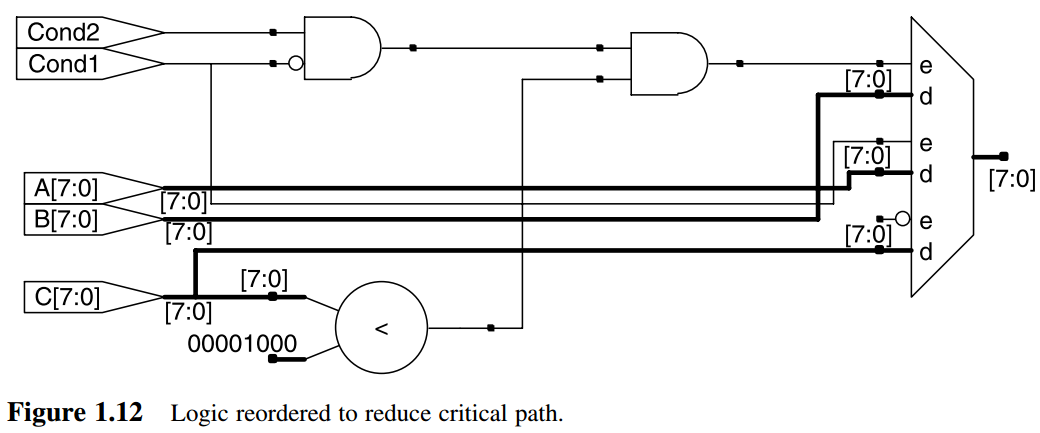

这是第二版的视图,关键路径居然少了一个器件。

这就是我惊讶的地方,因为这种做法从代码上看不出来。所以需要更高的硬件知识才能驾驭啊。

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884

FPGA中改善时序性能的方法_advanced FPGA design的更多相关文章

- ASP.NET中26种性能优化方法

系统类 Type类,Object类,String类, Arrary类,Console类, Exception类,GC类, MarshalByRefObject类, Math类. DateTime结构 ...

- js-JavaScript高级程序设计学习笔记21 改善JavaScript性能的方法

第24章 最佳实践 1.性能 1.避免全局查找 将在一个函数中会用到多次的全局对象保存在局部变量.比如多次使用document.getElement...,可以首先var doc=document,把 ...

- Altera FPGA中的pin进一步说明

最近END china上的大神阿昏豆发表了博文 <FPGA研发之道(25)-管脚>,刚好今天拿到了新书<深入理解Altera FPGA应用设计>第一章开篇就讲pin.这里就两者 ...

- Quartus II中FPGA的管脚分配保存方法

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择“Assignments ->Pin”标签(或者点击按 ...

- FPGA中浮点运算实现方法——定标

有些FPGA中是不能直接对浮点数进行操作的,仅仅能採用定点数进行数值运算.对于FPGA而言,參与数学运算的书就是16位的整型数,但假设数学运算中出现小数怎么办呢?要知道,FPGA对小数是无能为力的,一 ...

- Sql Server中三种字符串合并方法的性能比较

文章来自:博客园-DotNet菜园 最近正在处理一个合并字符吕的存储过程,在一个测试系统的开发中,要使用到字符串合并功能,直接在Sql中做.示例:有表內容﹕名称 內容1 abc1 ...

- 实例分析ASP.NET在MVC5中使用MiniProfiler监控MVC性能的方法

这篇文章主要为大家详细介绍了ASP.NET MVC5使用MiniProfiler监控MVC性能,具有一定的参考价值,感兴趣的小伙伴们可以参考一下 MiniProfiler ,一个简单而有效的迷你剖析器 ...

- 数字IC前后端设计中的时序收敛(二)--Setup违反的修复方法

本文转自:自己的微信公众号<数字集成电路设计及EDA教程> 里面主要讲解数字IC前端.后端.DFT.低功耗设计以及验证等相关知识,并且讲解了其中用到的各种EDA工具的教程. 考虑到微信公众 ...

- (转载)Quartus II中FPGA的管脚分配保存方法(Quartus II)

一.摘要 将Quartus II中FPGA管脚的分配及保存方法做一个汇总. 二.管脚分配方法 FPGA 的管脚分配,除了在QII软件中,选择"Assignments ->Pin&quo ...

随机推荐

- android-supporting-multiple-devices

There are a few common questions asked whenever development begins on a new Android app. What assets ...

- 为什么没有好用的Android游戏引擎?

随着Android平台的不断发展,最近Android开发人员数量呈现出上升势头,就连以往较为冷门的游戏开发领域也涌现出不少生力军.然而,全新的问题正摆在了刚開始学习的人面前,非常多他们从未遇过的问题開 ...

- VBA 开发学习--基础语法3

VBA字符串函数列表 Trim(string) 去掉string左右两端空白 Ltrim(string) 去掉string左端空白 Rtrim(string) 去掉string右端空白 Len(str ...

- 简单C#文字转语音

跟着微软走妥妥的,C#文字转语音有很多参数我就不说了,毕竟我也是初学者.跟大家分享最简单的方法,要好的效果得自己琢磨喽: 先添加引用System.Speech程序集: using System; us ...

- HTML5实现图片选择并预览

<%@ Page Language="C#" AutoEventWireup="true" CodeFile="Default.aspx.cs& ...

- SQL server与Oracle触发器的创建与使用

SQL Server 1创建触发器 GO BEGIN IF (object_id('WMY', 'tr') is not null) DROP trigger WMY END; GO CREATE T ...

- Java随机输出验证码包含数字、字母、汉字

//随机验证码,有数字.字符 //生成随机数,然后再截取,还要限定随机数的范围 String zimu = "ABCDEFGHIJKLMNOPQRSTUVWXYZabcdefghijklmn ...

- 如何为你的美术妹子做Unity的小工具(二)

你想像这样一样 为自己的Unity 小工具打开一个Unity的窗口吗? 看起来就很厉害对不对 妹子看了还不激动吗 ?!

- mysql快速翻页查询方法

SELECT SQL_NO_CACHE *FROM softdb_testWHERE id > (SELECT idFROM softdb_testORDER BY id DESCLIMIT 5 ...

- 框架开发(三)---smarty整合

一 smarty 是什么 Smarty是一个PHP的模板引擎.更明确来说,它可以帮助开发者更好地 分离程序逻辑和页面显示.最好的例子,是当程序员和模板设计师是不同的两个角色的情况,而且 大部分时候都不 ...