Zynq7000系列之芯片系统结构概述

相比较经典的FPGA,Zynq7000系列最大的特点是将处理系统PS和可编程资源PL分离开来,固化了PS系统的存在,实现了真正意义上的SOC(System On Chip)。

1. Zynq7000系列特征概述

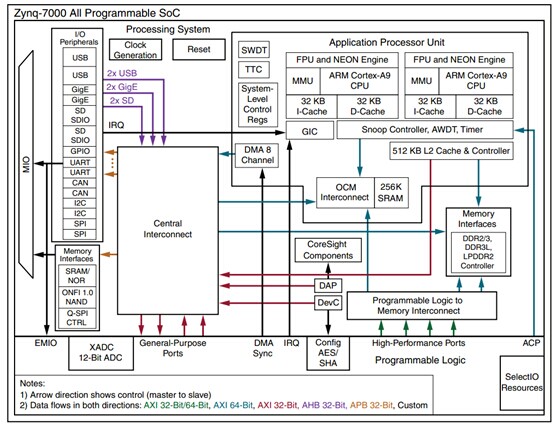

Zynq7000系列是全可编程片上系统,主要包含PS(processing system)和PL(Programmable Logic)两部分。PL采用28nm工艺;PS以2个Cortex A9的ARM核为核心,还包括片上存储器、片外存储器接口(DDR)和一系列的外设接口。Zynq7000系列将ARM CPU和外设集成在一个芯片内,使得Zynq7000系列皆具处理器和FPGA双重特性,特别适用于软硬件协同设计。

图1 Zynq-7000 All Programmable SoC Overview

1.1. PS部分特征

- 双Cortex-A9 ARM核

2.5 DMIPS/MHz per CPU

CPU frequency最高达1GHZ

单精度和双精度的向量浮点单元VFPU

3个看门狗定时器

1个全局定时器

2个 triple-timer 计数器

- Caches

每个CPU独立拥有32KB1级cache

两个CPU共享512KB的2级cache

- On-Chip Memory

片上自举ROM(boot rom)

256KB片上RAM

- External Memory Interfaces

16-bit or 32-bit DDR接口(DDR3, DDR3L, DDR2, or LPDDR2),当器件为DDR3时,最高数据速度可达1066 Mb/s。DDR 控制器有4个数据端口可用于对DDR的读写,分别命名为A、B、C、D。A专用于ARM CPU,B、C专门用于PL部分;D连接到interconnect.单元,可被interconnect上的其他主设备访问。

最高达1GB的地址空间

静态存储器接口(8-bit SRAM,Parallel NOR flash,ONFI1.0 NAND flash,1-bit SPI, 2-bit SPI, 4-bit SPI (quad-SPI), or two quad-SPI (8-bit) serial NOR flash)

- 8-Channel DMA Controller

支持Memory-to-memory, memory-to-peripheral, peripheral-to-memory, scatter-gather 交易。总线接口为64-bit AXI interface,其中有4个通道专用于与PL部分的通信。

- I/O Peripherals and Interfaces

2个 10/100/1000 tri-speed Ethernet MAC peripherals,接口为GMII, RGMII, and SGMII

2个 USB 2.0 接口

2个 CAN 2.0接口

2个SD 卡接口

2个双向SPI接口

2个高速UART接口

两个IIC接口

- GPIO

共118个,其中54个从PS直接连出去GPIO口(通过MIO),64个连接到PL的GPIO口;

最多54可复用IO(MIO)用于外设如USB、UART等的引脚分配,若使能的外设比较多,MIO个数不够时,可以将某些外设的引脚连接到PL,由PL通过通用IO口连接外部设备。如下图所示,并不是所有外设IOP都可以连接到PL,如USB就不可以连接到PL。

图2 MIO Module Block Diagram

- Interconnect

APU,、存储器单元、外设IOP、PL通过interconnect实现高速互联,interconnect支持多个主从设备的互相访问

- PS部分启动方式

PS部分采用众所周知的多阶段启动法,支持NOR, NAND, Quad-SPI, SD,or JTAG.启动。

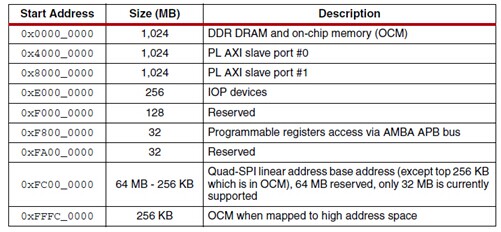

- 地址映射

图2 Zynq7000系列地址映射图

1.2. PL部分特征

该部分资源数目因器件型号不同而不同,以下所列数目皆为XQ7Z045的资源数。

- Configurable Logic Blocks (CLB)

CLB=305K/2个;

- 36 Kb Block RAM

545个

- Programmable DSP Slices

900个,主要是18X25的乘法器和48bit宽度的加法器;

- JTAG Boundary-Scan

- PCI Express Block

Gen2 Speed(5Gbps),最多8个。

- Serial Transceivers

最多16个,最高速度10.3125Gbps

- Two 12-Bit Analog-to-Digital Converters

2个12bit的数模转换器,最高转换速度1MSPS,最多支持17个外部输入。

- 时钟资源

XQ7Z045包含8个CMT,即8个MMCM+8个PLL;其输出时钟相位可为45°、90°、135°、180°、225°、275°、315°;

1.3. PS-PL 接口

PS和PL部分之间有多个接口,具体包括:

1、AXI类数据接口

2个32bit的AXI 主接口

2个32bit的AXI从接口

专用于PL访问DDR控制器的32/64bit的AXI从接口

1个64bit的访问CPU存储器的从接口

2、其他接口

DMA通道信号

PS的中断输入信号

事件信号

触发信号

EMIO

PS提供给PL的时钟信号及复位信号

XADC接口

JTAG接口

Zynq7000系列之芯片系统结构概述的更多相关文章

- Zynq7000系列之芯片引脚功能综述

很多人做了很久的FPGA,知道怎么去给信号分配引脚,却对这些引脚的功能及其资源限制知之甚少:在第一章里对Zynq7000系列的系统框架进行了分析和论述,对Zynq7000系列的基本资源和概念有了大致的 ...

- STC系列STC10F芯片解密STC10L单片机破解复制技术

STC系列STC10F芯片解密STC10L单片机破解 STC10F12XE | STC10F12 | STC10F10XE | STC10F10解密 STC10F08XE | STC10F08 | S ...

- 深入理解javascript函数系列第一篇——函数概述

× 目录 [1]定义 [2]返回值 [3]调用 前面的话 函数对任何一门语言来说都是一个核心的概念.通过函数可以封装任意多条语句,而且可以在任何地方.任何时候调用执行.在javascript里,函数即 ...

- Netty4.x中文教程系列(一) 目录及概述

Netty4.x中文教程系列(一)目录及概述 Netty 提供异步的.事件驱动的网络应用程序框架和工具,用以快速开发高性能.高可靠性的网络服务器和客户端程序. Netty是一个NIO客户端 服务端框架 ...

- Xilinx zynq-7000系列FPGA移植Linux操作系统详细教程

Xilinx zynq-7000系列FPGA移植Linux操作系统详细教程 一:前言 最近手上压了一块米联客的Miz7035,一块xilinx zynq-7000系列的开发板,想着正好学习一下linu ...

- Spring5.0源码学习系列之事务管理概述

Spring5.0源码学习系列之事务管理概述(十一),在学习事务管理的源码之前,需要对事务的基本理论比较熟悉,所以本章节会对事务管理的基本理论进行描述 1.什么是事务? 事务就是一组原子性的SQL操作 ...

- Spartan6系列之芯片配置模式详解

1. 配置概述 Spartan6系列FPGA通过把应用程序数据导入芯片内部存储器完成芯片的配置.Spart-6 FPGA可以自己从外部非易失性存储器导入编程数据,或者通过外界的微处理器.DSP等对 ...

- crtmpserver系列(一):流媒体概述

概述 所谓流媒体按照字面意思理解就是像流一样的媒体,看起来像是废话.流媒体现在司空见惯,所以一般人大概不会有疑问.事实上在流媒体还没有出现的时候,基本上通过网络播放电影就不太现实.通过网络播放电影的时 ...

- crtmpserver系列之一:流媒体概述

阅读目录 概述 流媒体系统的组成 媒体文件封装 传输协议 回到顶部 概述 所谓流媒体按照字面意思理解就是像流一样的媒体,看起来像是废话.流媒体现在司空见惯,所以一般人大概不会有疑问.事实上在流媒体还没 ...

随机推荐

- 使用AtomicInteger原子类代替i++线程安全操作

Java中自增自减操作不具原子性,在多线程环境下是线程不安全的,可以使用使用AtomicInteger原子类代替i++,i--操作完成多线程线程安全操作. 下面是等于i++多线程的自增操作代码: pu ...

- 浪潮服务器装机RAID

下面是在装浪潮服务器NF8480M5收集的资料,但是NF8480M5服务器没有网上说的webBIOS界面需要按住DEL进BIOS,将启动都禁止了再重启,进入页面配置. http://blog.51ct ...

- HDU——2067 小兔的棋盘

小兔的棋盘 Time Limit: 1000/1000 MS (Java/Others) Memory Limit: 32768/32768 K (Java/Others) Total Subm ...

- 在docker上安装运行mysql实例

ps:实验环境是:CentOS Linux release 7.3 64位1.获取mysql镜像从docker hub的仓库中拉取mysql镜像docker pull mysql查看镜像docker ...

- spring-cloud-starter-ribbon提供客户端的软件负载均衡算法

Ribbon是什么? Ribbon是Netflix发布的开源项目,主要功能是提供客户端的软件负载均衡算法,将Netflix的中间层服务连接在一起.Ribbon客户端组件提供一系列完善的配置项如连接超时 ...

- 使用Vundle管理配置Vim的插件

1.介绍: 安装需要Git,触发git clone,默认将每一个指定特定格式插件的仓库复制到~/.vim/bundle/. 搜索需要Curl支持. Windows用户请直接访问Windows setu ...

- js滚轮换切屏

因为全项目不是自己写的,仅仅是帮别人写js滚轮代码,并且别人项目也还未上线.所以仅仅贴出自己写的那段部分代码, 效果:鼠标滚轮滚动时.网頁屏幕一屏一屏的上下切换 (下面代码在本地电脑的IE,chrom ...

- Python3标准库(一) 内置函数

Python中内置了很多的函数,而学习标准库我们需要事先熟悉这些内置函数,所以在这里一个个进行介绍.有些函数比较简单,只给予文字描述,而有些函数会给出示例代码帮助理解. 1.abs(x):返回一个整数 ...

- 深圳MPD大会 讲师演讲稿 2014-10

深圳MPD大会 讲师演讲稿 2014-10 互联网下的蛋-姜志辉.pdf: http://www.t00y.com/file/76704370 俞炜-互联网研发整形术 终于版.pdf: htt ...

- CA certificate

1 什么是CA certificate CA证书本质上是一把公钥. 2 为什么需要CA证书 是为了避免黑客冒充服务器,服务器通过CA证书证明自己是真的服务器,而不是黑客. 就是说,一旦客户端有了一个服 ...