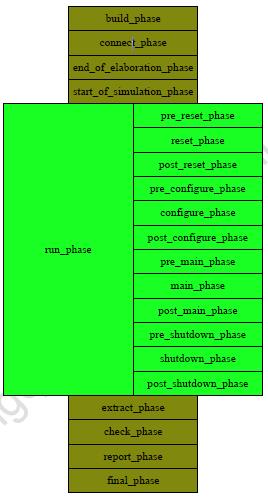

UVM基础之------uvm phases机制

代码的书写顺序会影响代码的实现,在不同的时间做不同的事情,这是UVM phase的设计哲学,UVM phase提供了一个通用的TB phase 解决方案。支持显示的隐式的同步方案,运行时刻的线程控制和跳转。只要把代码填入对应的phase,这些代码就会自动执行。phase 的引入在很大程度上解决了代码顺序杂乱可能会引发的问题。它本质上是通过把代码顺序强制固定来实现这个目的的,如 build_phase 的代码一定在connect_phase之前执行 ,而 connect_phase的代码一定在 end_of_elaboration_phase之前执行等等。遵循 UVM 的这种代码顺序划分原则,可以在很大程度上减少验证平台开发者的工作量,让其从一部分杂乱的工作中解脱出来。在本篇里面主要介绍在uvm phase里面的一些基本的概念。

UVM基础之------uvm phases机制的更多相关文章

- UVM基础之---------uvm report 机制分析

uvm 中的信息报告机制相对来说比较简单,功能上来说主要分为两部分: 第一通过ID对component的信息报告冗余级别进行控制,针对每个冗余级别进行不同的行为控制.这部分工作主要由uvm_repor ...

- UVM基础之-------uvm factory机制override<博>

override功能是UVM中一个比较重要的功能,这个功能也是在factory里面实现的,我们会在env或者具体的case中使用override功能. class case_x extends bas ...

- UVM基础之---------uvm factory机制register

factory机制的一大特点就是根据类的名字来创建类的实例. factory 机制中根据类名来创建类的实例所用到的技术:一是参数化的类,二是静态变量和静态函数.这两者是factory机制实现的根本所在 ...

- UVM基础之---------uvm factory机制base

从名字上面就知道,uvm_factory用来制造uvm_objects和component.在一个仿真过程中,只有一个factory的例化存在. 用户定义的object和component types ...

- UVM基础之-------uvm report机制的使用

后面的例子我会继续补充: 1. 因为uvm默认定义的message格式比较长,非常不利于debug过程中的分析使用,一般情况下,开始使用uvm,都要利用uvm_report_server重新定义mes ...

- UVM基础总结——基于《UVM实战》示例

一.前言 工作一直在做SoC验证,更关注模块间的连接性和匹配性,所以相比于擅长随机约束激励的UVM来说,定向测试的概念更容易debug.当然前提是IP已经被充分验证.因此觉得接触UVM的机会较少.到现 ...

- Cadence UVM基础视频介绍(UVM SV Basics)

Cadence关于UVM的简单介绍,包括UVM的各个方面.有中文和英文两种版本. UVM SV Basics 1 – Introduction UVM SV Basics 2 – DUT Exampl ...

- UVM基础之------uvm_transaction

uvm_transaction继承自uvm_object,添加了timing和recording接口,该类是uvm_sequence_item的基类.下边将做剖析 1. 这个类提供了时间戳属性(tim ...

- UVM基础之---Command-line Processor

提供一个厂商独立的通用接口命令行参数,支持分类: 1. 基本参数和值:get_args,get_args_matches 2. 工具信息:get_tool_name(),get_tool_ve ...

随机推荐

- WinExec可能会引起消息重入

WinExec不仅会造成延迟,并且还会引起消息的重入. 以下是调用堆栈: WinvoiceCC.exe!CWinvoiceCCDlg::OnMsgHttpReq(unsigned int wParam ...

- Swift 函数Count,Filter,Map,Reduce

原创Blog,转载请注明出处 blog.csdn.net/hello_hwc 前言:和OC不同,Swift有非常多全局的函数,这些全局函数对简化代码来说非常实用.眼下Swift出到了2.0,只是我这篇 ...

- 【动态规划】Dynamic Programming

动态规划 一.动态规划 动态规划(Dynamic Programming)是一种设计的技巧,是解决多阶段决策过程最优化问题的通用方法. 基本思想:将待求解问题分解成若干个子问题,先求解子问题,然后从这 ...

- mysql连接字符串,连接字段结果集

archie2010 ${原来姹紫嫣红开遍,似这般都付与扣钉八哥} mysql连接字符串,连接字段结果集 select CONCAT('My', 'S', 'QL连接字符串') as MySql; 连 ...

- 容器与容器编排实战系列 1 -- Docker 安装

CentOS7.4 下安装Docker 详细步骤 第一步:安装Docker yum install -y yum-utils device-mapper-persistent-data lvm2 yu ...

- ios19---xib

// // ViewController.m #import "ViewController.h" @interface ViewController () @end @imple ...

- Linux/Android——input系统之 kernel层 与 frameworks层交互 (五)【转】

本文转载自:http://blog.csdn.net/jscese/article/details/42291149 之前的四篇博文记录的都是linux中的input体系相关的东西,最底层以我调试的u ...

- CPU卡详解【转】

本文转载自:http://blog.csdn.net/logaa/article/details/7571805 第一部分 CPU基础知识 一.为什么用CPU卡 IC卡从接口方式上分,可以分为接触式I ...

- Elementui tabs组件内添加组件

1. Elementui tabs组件内添加组件 1.1. 需求 今天的一个需求是在后台框架的基础上添加tab页,结果页面如下 原本上述红框内的内容是不存在的,直接点击左侧菜单栏进行页面跳转,现加了t ...

- 汇编程序49:实验14 访问CMOS RAM(显示系统时间)

assume cs:code ;安装程序,使用指令out和in指令 code segment start: mov ax,cs mov ds,ax mov si,offset sub1 mov ax, ...