《FPGA全程进阶---实战演练》第十章 数码管实验

1基础理论部分

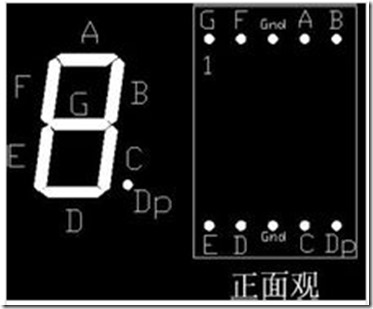

led数码管是由多个发光二极管封装在一起组合的“8”字型的器件,引线内部已经完成,如下图10.1所示,图10.2为实物图。

图10.1 数码管内部结构

那么我们想要控制数码管的亮灭,其实也就是控制发光二极管的亮灭,分别用高低电平去控制。对于数码管来说,读者若是学过单片机及其他MCU的话,其实都知道数码管的控制有两个信号是比较重要的,一个是段选信号,一个是位选信号,位选信号是针对有多个数码管时,需要控制哪一个数码管发亮,段选就是控制数码管显示什么数字。

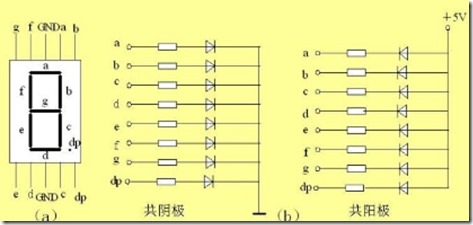

那么在购买数码管的时候,往往买回来时上面没有标注各引脚信息。这时不要慌,首先你购买时要分清共阳极还是共阴极数码管,共阳极和共阴极数码管电路示意图如图10.2所示。然后可以利用万用表打到“二极管”档位,然后万用表正极接触数码管一个引脚,负极去挨个触碰其他引脚,直到数码管发亮时,可以记录对应的引脚信息即可。

图10.2 数码管共阳和共阴极电路图

1.1 静态显示

静态驱动也称直流驱动。静态驱动是指每个数码管的每一个段码都由一个I/O端口进行驱动,或者使用如BCD码二-十进制译码器译码进行驱动。静态驱动的优点是编程简单,显示亮度高,缺点是占用I/O端口多,如驱动5个数码管静态显示则需要5×8=40根I/O端口来驱动。

1.2 动态显示

动态驱动是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O线控制。

2 Verilog代码实现部分

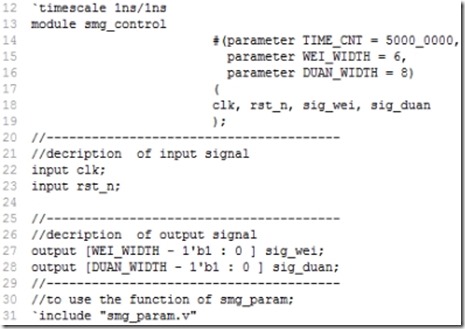

现在要实现数码管的静态显示功能,从0加到f,时间间隔为1s。封装接口为

2.1 smg_control模块

上述是整个模块的声明,并且调用了smg_param.v的文件,用于数码管解码参数的设置,关于include的用法可以参考其他语法书籍。

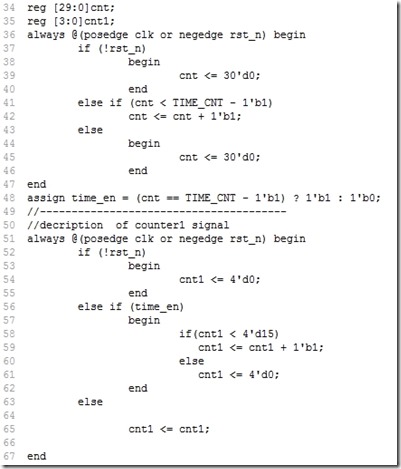

两个计数器,一个用于实现时钟计数1s,一个用于数码管编解码计数控制。

上述是实现数码管解码部分,注意smg_param.v中参数调用的方法。

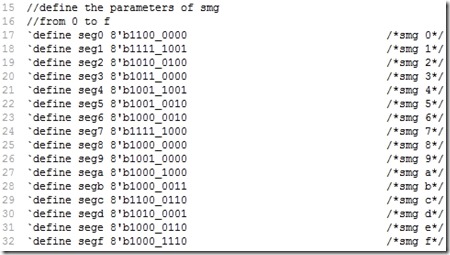

2.2 smg_param模块

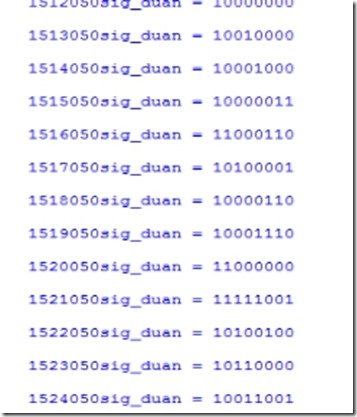

3 Modelsim仿真部分

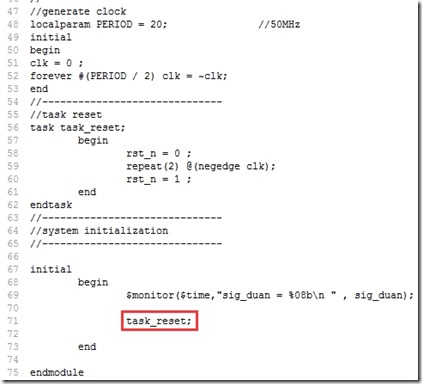

仿真程序很简单,只需添加时钟和复位信号即可。测试的脚本文件如图10.3所示,因测试时将计数改到50,所以周期是1000ns。

图 10.3 测试脚本文件

《FPGA全程进阶---实战演练》第十章 数码管实验的更多相关文章

- 《FPGA全程进阶---实战演练》第三十二章 Signal Tap II 应用实例

还有几天就要交文章终稿了,三年的研究生生活也快要结束了,时间飞快,岁月如梭,但学习技术的热情仍然不能松懈,不懂的东西太多,需要实时保持奋斗!!过些天会继续更新<FPGA全程进阶---实战演练&g ...

- 《FPGA全程进阶---实战演练》第十二章 二进制码与格雷码PK

大家在写程序的时候,可能会听闻,什么独热码,什么格雷码,什么二进制码等等,本节意在解释这几种编码之间的区别和优势以及用verilog怎么去实现,下面先介绍这几种编码的区别. 1 基础理论部分 1.1 ...

- 《FPGA全程进阶---实战演练》第五章 基于74HC595的LED操作

1基础理论部分 1.1分频 分频,是的,这个概念也很重要.分频是指将一单一频率信号的频率降低为原来的1/N,就叫N分频.实现分频的电路或装置称为“分频器”,如把33MHZ的信号2分频得到16.5MHZ ...

- 《FPGA全程进阶---实战演练》第四章之实验平台软硬件使用简介

本章主要是讲解读者在进行FPGA逻辑设计之前的准备工作,需要下载Quartus II软件和 Modelsim 软件,一个是用来进行FPGA逻辑设计,一个是用来对逻辑进行理论分析与验证. 1.1 qua ...

- 《FPGA全程进阶---实战演练》第十一章 VGA五彩缤纷

1基础理论部分 VGA(video graphics array)即视频图形阵列,是IBM在1987年随PS/2一起推出的使用模拟信号的一种视频传输标准.VGA相比与现在的视频传输接口来说已经过时,不 ...

- 《FPGA全程进阶---实战演练》第一章之如何学习FPGA

对于很多初学者,大部分都是急于求成,熟不知越是急于求成,最终越是学无所成,到头来两手空空,要学好FPGA,必须弄懂FPGA本质的一些内容. 1.FPGA内部结构及基本原理 FPGA是可以编程的,必须通 ...

- 《FPGA全程进阶---实战演练》第一章之FPGA介绍

1 什么是FPGA FPGA也即是Field Programmable Gate Array的缩写,翻译成中文就是现场可编程门阵列.FPGA是在PAL.GAL.CPLD等可编程器件的基础上发展起来的新 ...

- 《FPGA全程进阶---实战演练》第二章之焊接板子及调试注意事项

1.若是读者第一次做板子,强烈建议画完PCB板后将PCB图打印出来,然后对照你买的芯片将芯片放置对 应的位置,然后查看所有的封装格式适不适合,否则等你做出板子来后再试,为时晚矣.笔者虽然知道要这么 做 ...

- 《FPGA全程进阶----实战演练》第二章之系统搭建

1 系统方案 对于设计一款硬件平台,首先要确定整体框架,确定各个模块所需要的芯片以及电压分配情况.图2.6是笔者曾经设计的硬件平台系统. 图2.6系统框图 对于选定一个系统方案之后,接下来做的要先去查 ...

随机推荐

- 最全Java锁详解:独享锁/共享锁+公平锁/非公平锁+乐观锁/悲观锁

在Java并发场景中,会涉及到各种各样的锁如公平锁,乐观锁,悲观锁等等,这篇文章介绍各种锁的分类: 公平锁/非公平锁 可重入锁 独享锁/共享锁 乐观锁/悲观锁 分段锁 自旋锁 01.乐观锁 vs 悲观 ...

- MySQL 数据库新用户授权

--- 新建数据库用户授权 --远程的 GRANT ALL PRIVILEGES ON `testdb`.* TO 'username'@'%' IDENTIFIED BY 'pwd2017'; -- ...

- 【MySQL】MySQL表设计的常用数据类型

整数类型,tinyint.smallint.mediumint.int.bigint 如果需要保存整数(不含小数),可以选择tinyint.smallint.mediumint.int.bigint, ...

- (转)Using Python3.5 in Ubuntu - Trusty

转自:https://www.reddit.com/r/IPython/comments/3lf81w/using_python35_in_ubuntu_trusty/Note:照这个方案安装pyth ...

- Lua应用——tables应用,查找是否为保留字

Lua中的table功能确实强大.因为table是Lua中的唯一数据结构.今天有点晕,少说两句多拷贝代码吧. 实例: 假定你想列出在一段源代码中出现的所有标示符,某种程度上,你需要过滤掉那些语言本身的 ...

- SpringBoot热部署配置(基于Maven)

热部署的意思是只要类中的代码被修改了,就能实时生效,而不用重启项目.spring-boot-devtools 是一个为开发者服务的一个模块,其中最重要的功能就是自动应用代码更改到最新的App上面去.原 ...

- 'Project Name' was compiled with optimization

'Project Name' was compiled with optimizationhtml, body {overflow-x: initial !important;}html { font ...

- PHP判断ajax请求:HTTP_X_REQUESTED_WITH

PHP判断ajax请求的原理: 在发送ajax请求的时候,我们可以通过XMLHttpRequest这个对象,创建自定义的 header头信息, 在jquery框架中,对于通过它的$.ajax, $.g ...

- 【Unity笔记】Terrain地形制作坍塌/深坑

Unity的Terrain组件在[set the terrain height]分页下,height高度为0时,可理解为该地形的海平面高度,此时就不能地形下榻.把height调到100,点击[flat ...

- [开发笔记]-实现winform半透明毛玻璃效果

亲测win7下可用,win8下由于系统不支持Aero效果,所以效果不是半透明的. 代码: 博客园插入不了代码了..... public partial class Form1 : Form { int ...