基于FPGA的VGA接口使用

前言

什么是VGA?

VGA(视频图形阵列)是IBM公司制定的一种视频数据传输标准。

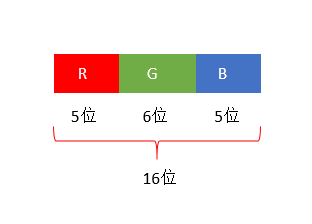

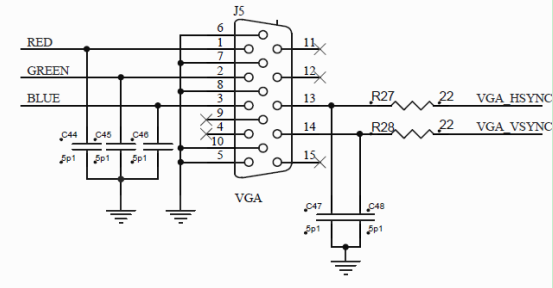

接口信号主要有5个:R(Red),G(Green),B(Blue),HS(Horizontal synchronization水平同步),VS(Vertical synchronization垂直同步)。水平同步也叫行(line)同步,垂直同步也叫帧(frame)同步。信号都是模拟信号。

用途:连接CRT显示器或者带VGA接口的LCD液晶显示器。

VGA的接口原理是什么?行消隐,场消隐?

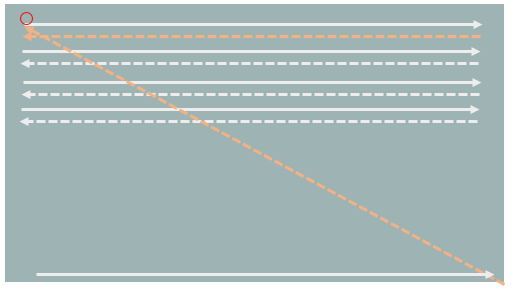

逐行扫描的方式,电子束从屏幕左上角一点开始,从左向右逐行扫描。每扫描完一行,电子束回到屏幕的左边下一行的起始位置。当所有行扫描完毕后,电子束回到屏幕的左上角起始位置,开始下一次扫描。水平方向电子束从右侧回到左侧所需的时间叫行消隐;电子束从右下角回到左上角起始位置所需的时间叫场消隐。

听大佬说缩短消隐区,但太短测试我未通过,还是按标准来吧。

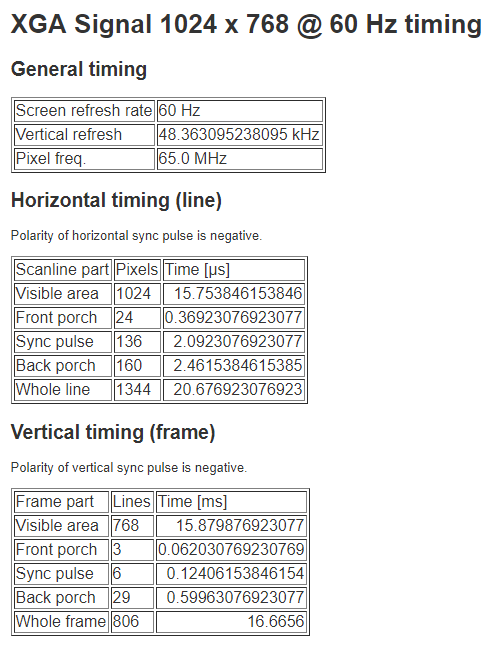

VGA时序参数?

可以从网站上查询到你所需要的参数:http://tinyvga.com/vga-timing

本次进行1024*768分辨率下的VGA三道杠条纹显示开发:

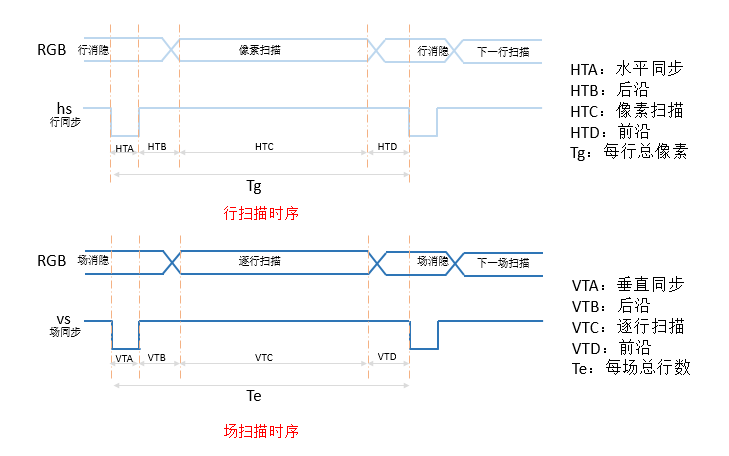

VGA接口的工作时序?

图像的显示是以像素为单位的,行同步信号hs的负脉冲到来时要由RGB送出在当前行显示的像素,下一个负向脉冲用来显示下一行。当整个屏幕显示一遍后,由帧同步信号vs送出一个负向脉冲,又从左上角显示。

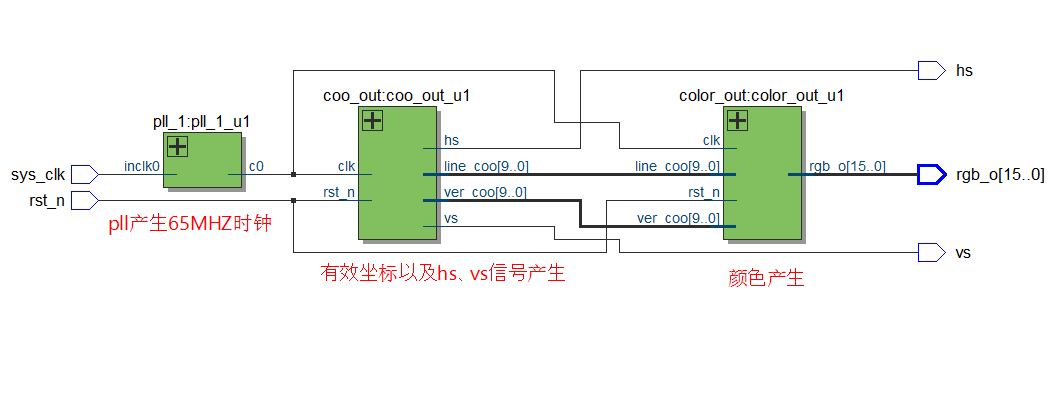

功能划分:(懒到不想画图了)

编码实现:

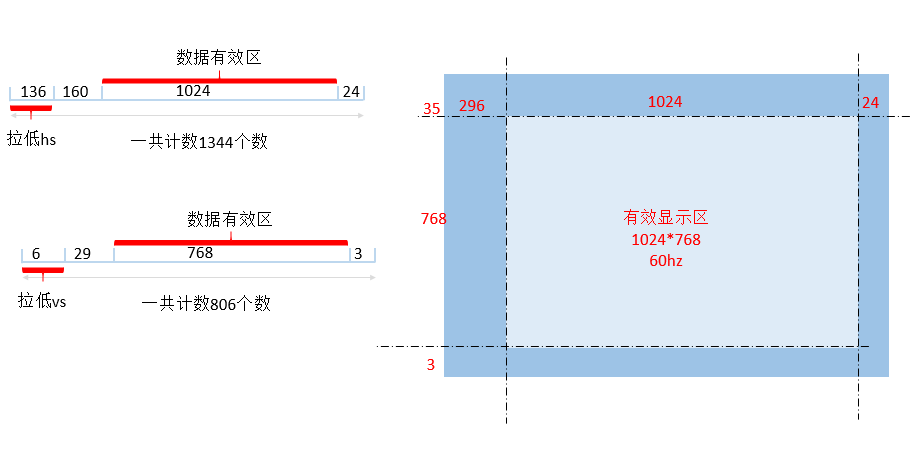

系统时钟确定:T=刷新hz*总像素点

总像素点=水平计数*垂直计数=1344*806

推得:T=60*1344*806=65mhz(约等于)

坐标与hs、vs信号产生。

//************************************************

// Filename : coo_out.v

// Author : kingstacker

// Company : School

// Email : kingstacker_work@163.com

// Device : Altera cyclone4 ep4ce6f17c8

// Description : product the coodinate and hs vs;

//************************************************

module coo_out #(parameter WIDTH = )(

//input;

input wire clk, //65mhz;

input wire rst_n,

//output;

output wire hs, //horizontal synchronization;

output wire vs, //vertical syn;

output reg [WIDTH-:] line_coo, //line coodinate;

output reg [WIDTH-:] ver_coo //vertical coodinate;

); //1024*768;

localparam HTA = 'd136, //sync pulse;

HTB = 'd160, //back porch;

HTC = 'd1024, //visible area;

HTD = 'd24, //front porch;

VTA = 'd6, //sync pulse;

VTB = 'd29, //back porch;

VTC = 'd768, //visible area;

VTD = 'd3, //front porch;

LINE_CNTMAX = HTA+HTB+HTC+HTD-'b1, //max line count;

VER_CNTMAX = VTA+VTB+VTC+VTD-'b1, //max ver count;

HSTART = HTA+HTB,

VSTART = VTA+VTB;

reg [WIDTH+:] line_cnt;

reg [WIDTH+:] ver_cnt;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

line_cnt <= 'd0;

end //if

else begin

if (line_cnt == LINE_CNTMAX) begin

line_cnt <= 'd0;

end //if

else begin

line_cnt <= line_cnt + 'b1;

end //else

end //else

end //always

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

ver_cnt <= 'd0;

end //if

else begin

if ((ver_cnt == VER_CNTMAX)&&(line_cnt == LINE_CNTMAX)) begin

ver_cnt <= 'd0;

end //if

else begin

ver_cnt <= (line_cnt == LINE_CNTMAX)? (ver_cnt + 'b1) : ver_cnt;

end //else

end //else

end //always

assign hs = (line_cnt < HTA) ? 'b0 : 1'b1;

assign vs = (ver_cnt < VTA) ? 'b0 : 1'b1;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

line_coo <= ;

ver_coo <= ;

end //if

else begin

if((line_cnt >= HSTART)&&(line_cnt < HSTART + HTC)&&(ver_cnt >=VSTART)&&(ver_cnt < VSTART + VTC)) begin

line_coo <= line_cnt - HSTART;

ver_coo <= ver_cnt - VSTART;

end

end //else

end //always endmodule

三道杠产生:

//************************************************

// Filename : color_out.v

// Author : kingstacker

// Company : School

// Email : kingstacker_work@163.com

// Device : Altera cyclone4 ep4ce6f17c8

// Description :

//************************************************

module color_out #(parameter WIDTH = )(

//input;

input wire clk,

input wire rst_n,

input wire [WIDTH-:] line_coo,

input wire [WIDTH-:] ver_coo,

//output;

output reg [:] rgb_o

);

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

rgb_o <= 'd0;

end //if

else begin

if(ver_coo < 'd255) begin

rgb_o <= {'b11111,6'd0,'d0};

end

else begin

if (ver_coo < 'd511) begin

rgb_o <= {'d0,6'b111111,'d0};

end

else begin

rgb_o <= {'d0,6'd0,'b11111};

end

end

end //else

end //always endmodule

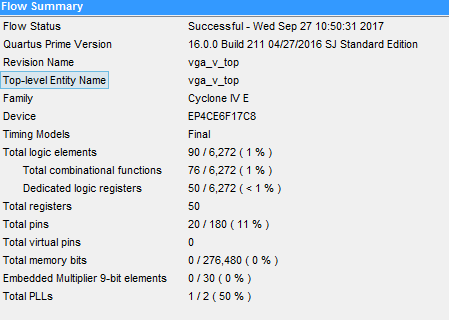

综合资源使用:

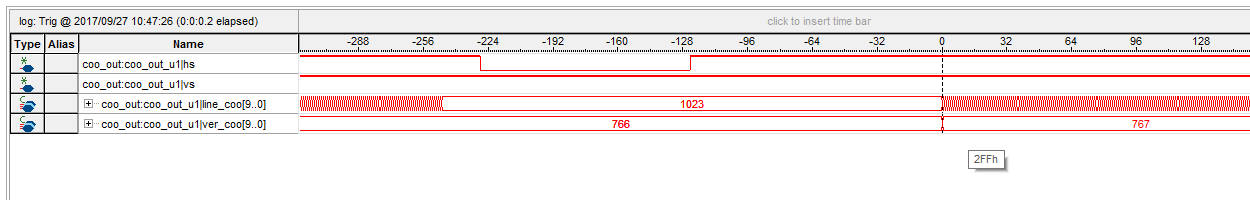

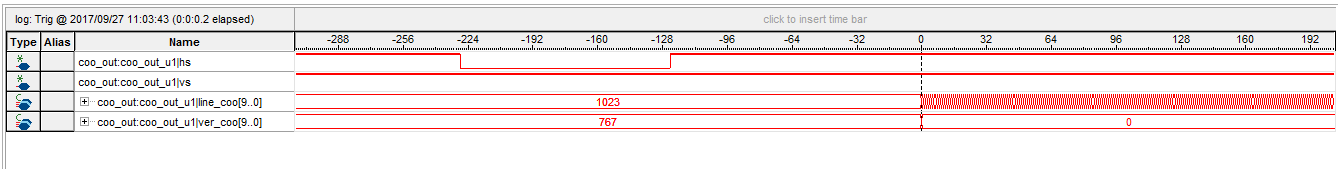

抓波:

接显示器看看:三道杠少年

修改color_out:九宫格(很无聊的东西hhhhhh)

图片放rom显示:100*100

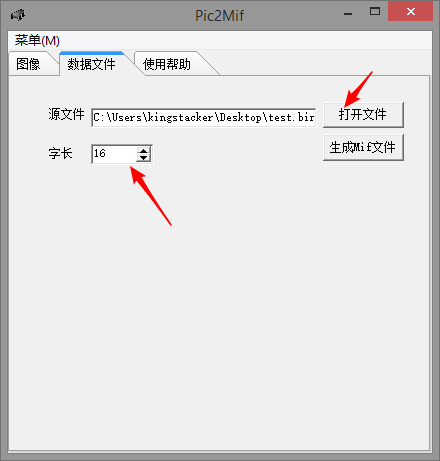

mif文件可由matalb生成,也可以用下面两个软件生成(更方便):

用lmage2Lcd生成bin文件:

bin文件转换为mif文件:

再把mif文件放rom即可。

显示器显示图片:

以上。

基于FPGA的VGA接口使用的更多相关文章

- 基于FPGA的VGA可移植模块终极设计【转】

本文转载自:http://www.cnblogs.com/lueguo/p/3373643.html 略过天涯 基于FPGA的VGA可移植模块终极设计 一.VGA的诱惑 首先,VGA的驱动,这事, ...

- 基于FPGA的VGA显示实验设计

基于FPGA的VGA显示实验设计 成果展示(优酷视频): 视频: 基于FPGA的VGA显示技术(手机控制) http://v.youku.com/v_show/id_XNjk4ODE3ODUy.htm ...

- 基于FPGA的VGA显示设计(二)

上一篇:基于FPGA的VGA显示设计(一) 参照 CrazyBingo 的 基于FPGA的VGA可移植模块终极设计代码 的工程代码风格,模块化处理了上一篇的代码,并增加了一点其它图形. 顶层 ...

- 基于FPGA的VGA显示静态图片

终于熬到暑假了,记过三四周的突击带考试,终于为我的大二画上了一个完整的句号,接下来终于可以静心去做自己想做的事情了,前一阵子报了一个线上培训班,学学Sobel边缘检测,之前一直在学习图像处理,但是因为 ...

- 基于FPGA的PCIe接口实现(具体讲解了数据流向)

时间:2014-12-09 来源:西安电子科技大学电子工程学院 作者:姜 宁,陈建春,王 沛,石 婷 摘要 PCI Express是一种高性能互连协议,被广泛应用于网络适配.图形加速器.网络存储.大数 ...

- 基于FPGA的VGA显示设计(一)

前言 FPGA主要运用于芯片验证.通信.图像处理.显示VGA接口的显示器是最基本的要求了. 原理 首先需要了解 : (1)VGA接口协议:VGA端子_维基百科 .VGA视频传输标准_百度 引脚1 RE ...

- 基于FPGA的VGA可移植模块终极设计

一.VGA的诱惑 首先,VGA的驱动,这事,一般的单片机是办不到的:由于FPGA的速度,以及并行的优势,加上可现场配置的优势,VGA的配置,只有俺们FPGA可以胜任,也只有FPGA可以随心所欲地配置( ...

- [置顶]

基于FPGA的VGA简易显存设计&NIOS ii软核接入

项目简介 本项目基于Altera公司的Cyclone IV型芯片,利用NIOS II软核,2-port RAM与时序控制模块,实现64*48分辨率的显存(再大的显存板载资源m9k不够用) 实现效果如下 ...

- FPGA学习-VGA接口

一般FPGA开发板的VGA会向用户暴露两共五个种接口,第一种是时序信号,用于同步传输和显示:第二种是色彩信号,用于随着时序把色彩显示到显示器上 时序接口 行同步信号-用于指示一行内像素的显示 场同步信 ...

随机推荐

- 后台管理系统之系统操作日志开发(Java实现)

一,功能点 实现管理员操作数据的记录.效果如下 二,代码实现 基于注解的Aop日志记录 1.Log实体类 package com.ideal.manage.guest.bean.log; import ...

- Java 读取配置文件数据

Properties类 Properties类,是一个工具类,包含在java.util包中. 功能:可以保存持久的属性,通常用来读取配置文件或者属性文件,将文件中的数据读入properties对象中, ...

- python生成个性二维码学习笔记

在linux环境下进行编码 1.先进家目录,自行创建Code文件夹 cd Code 2.下载MyQR库 sudo pip3 install MyQR 3.下载所需资源文件并解压 Code/ $ wge ...

- Python3练习题 018:打印星号菱形

Python的内置方法 str.center(width [, fillchar]) 就能轻而易举打印出来:str即是数量不等的星号,width即是最大宽度(7个空格),默认填充字符fillchar就 ...

- C#设计模式之6:抽象工厂模式

前面分析了简单工厂模式和工厂方法模式,接着来看一下抽象工厂模式,他与工厂方法模式有一些相似的地方,也有不同的地方. 先来看一个不用工厂方法模式实现的订购披萨的代码: 对象依赖的问题:当你直接实例化一个 ...

- day 7-17 多表查询

一. 准备表 #部门表 create table dep( id int, name varchar(20) ); #员工表 create table emp( id int primary key ...

- Day 4-2 time & datetime模块

time模块. import time time.time() #输出: 1523195163.140625 time.localtime() # 获取的是操作系统的时间,可以添加一个时间戳参数 # ...

- 获取打开页面时的当前时间(yyyy-MM-dd hh:mm:ss)

Date.prototype.Format = function (fmt) { var o = { "M+": this.getMonth() + 1, //月份 "d ...

- Django Rest framework 框架之认证使用和源码执行流程

用这个框架需要先安装: pip3 install djangorestframework 如果写了一个CBV的东西,继承了View. # 继承Django里面View class APIView(Vi ...

- Python基础知识2-内置数据结构(下)

bytes.bytearray #思考下面例子: a = 1 b = a print(a == b)#True print(a is b)#True print(id(a) is id(b))#Fal ...