07-verilog & sytem verilog

一.数据类型

二值逻辑变量

bit

- 不赋值的时候,变量初始默认为0

- x或z的值会转变为0

- bit vector--bit矢量

bit [msb,lsb] variable_name = [initial_value]

- 位宽:最高位为MSB,最低位为LSB

- 不加任何描述,默认为unsigned,无符号数;表示有符号数需要加signed进行描述

- 二值逻辑方便编译器的优化,效率更高,性能更好;但是不支持X和Z状态,不适用于RTL设计

建立自己的仿真目录

- sim -- 仿真目录,放Makefile文件

- RTL -- 放RTL代码

- TB -- 放testbench

- 使用tb文件进行仿真

module tb_test;

//定义变量

bit [3:0] a;

bit [4:0] b;

initial begin

a = 4'b0;

b = -10;

$display("a = %b",a);

$display("b = %b",b); // 10110 就是-10的补码

end

endmodule

- begin end之间就是代码块

- $display()就类似于print()函数

- 使用Makefile进行测试

Makefile文件

PLATFORM = LINUX64

FLIST := ../tb/tb_test.v

run:

vcs -sverilog $(FLIST) -debug_all -P ${NOVAS_HOME}/share/PLI/VCS/LINUX64/novas.tab ${NOVAS_HOME}/share/PLI/VCS/LINUX64/pli.a -R -kdb -lca

wave:

verdi -simflow -elab simv.daidir/kdb.elab++ -ssf sim.fsdb

clean:

rm csrc novas_dump.log sim.fsdb simv simv.daidir ucli.key verdi_config_file novas.conf novas.rc verdiLog -rf

通过make run进行仿真

byte\shortint\int\longint

- byte 8bit

- shortint 16bit

- int 32bit

- longint 64bit

byte/shortint/int/longint variable_name = initial_value;

- 默认都是有符号数,十进制数

- 在前端设计中,这些数据类型是很少用到的

shortint temp = 256;

int sample,ref_data = -9876;

longint a,b;

longint unsigned testdata;

real & shortreal

- real 等于C语言中的double,64bit

- shortreal等于C语言中的float,32bit

- 有符号数

- 在验证覆盖率的时候会用到

real/shortreal variable_name = initial_value

real alpha = 100.0,coverage_result;

coverage_result = $get_coverage();

if(coverage_result = 100.0)...

四值逻辑变量

- 四值逻辑:0,1,x,z

- 如果不声明数值,变量的初始值为x;在进行设计的时候要避免x态传递

reg & logic

- 四值逻辑在verilog中使用reg

reg [MSB:LSB] variable_name = initial_value;

- 在SV中使用logic变量

logic [MSB.LSB] variable_name = initial_value;

- reg和logic如果不用signed修饰,默认都是无符号数

- logic继承了reg所有的特性,但是logic可以进行连续赋值,并且只有一个驱动;如果定义了一个reg变量,是不能用assign对其进行赋值的,但是logic变量可以用assign进行赋值

- SV中:logic相当于reg和只有一个驱动的wire

module tb_test;

wire [3:0] b;

assign b = din_c;

assign b = din_d; //多个变量和b连接,多驱动,前提是cd具有推拉结构,OC,OD门

wire [3:0] e;

assign e = din_c; //单驱动

endmodule

integer & time

- integer,32bit有符号数

- time,64bit无符号数

integer a = -100,b;

time current_time;

b = -a;

current_time = $time;// $time内置函数,返回仿真时间

if(current_time>100ms).....

枚举类型

将所有的情况列举出来,在状态机中使用的比较多,比如FSM有限状态机

- 默认的数据类型是int

- 初始化值是0

- 可以使用枚举变量.name,显示枚举字符

enum [data_type] {named constants} enum_var1,enum_var2....;

module tb_test;

enum bit[2:0] {IDLE=3'b001,TEST=3'b010,START=3'b100} st; //声明枚举类

initial begin

st = START;

$display("st=%3b,name=%s",st,st.name); //st = 100,name=START

$finish;

end

endmodule

- 使用typedef定义枚举类,方便例化

typedef enum [data_type] {named constants} enumtype;

typedef enum bit[2:0] {IDLE=3'b001,TEST=3'b010,START=3'b100} state; //定义枚举类

state st; //例化一个枚举

initial begin

st = START;

$display("st=%3b,name=%s",st,st.name); //st = 100,name=START

$finish;

end

- 不使用枚举类型还可以使用parameter

parameter variable_name = initial_value;

固定数组

type(数据类型 bit reg logic..) [位宽] array_name [size] = initial value;

- 超过边界的写操作将被忽略

- 超过边界的读操作:2值逻辑返回0,四值逻辑返回x

- 支持多维数组

- size--就是数组长度,index从0开始

integer number[5]; //定义一个长度为5的数组,不给初值

int b[2] = {3,7};

int c[2][3] = {{3,7,1},{5,1,9}}; //定义二维数组

byte d[7]][2] = {default:-1} ; 将所有元素的值都设置默认-1

bit [31:0] a[2][3] = c; //数组可以通过赋值的方式进行复制

for(int i = 0;i<$dimensions(a);)

$display($size(a,i+1);) // 2,3,32

- $dimensions(数组)--返回数组的维数

- $size(数组,数组维数)--返回给定数组维数数组元素的个数

module tb_test;

logic [3:0] arr[3]; //定义长度为3的一维数组,每个元素为三位二进制数

logic [3:0] arr2[3][3]; //定义二维数组

initial begin

arr[0] = 4'd2;

end

endmodule

二.操作符

语法规则

- verilog和system verilog一样,都是大小写敏感的

- 注释 // /**/

- 数制格式

<size>'<base><number>

- base-b表示2进制 ,d表示10进制,h表示16进制数

- size是将数值转化为二进制数的时候的二进制位宽

32'h_beef_cafe

操作符

- 一般在写除法的时候,是需要设计特定的算法进行计算的,硬件当中实现除法比较麻烦

- 自增和自减用在for循环中使用的比较多

- 逻辑运算&& || !

- 逻辑等于,不等于 == !==

- 逻辑与或非,在运算的时候需要参与运算的位数应该都是一位的

左移和右移运算

module tb_test

logic [3:0] a;

initial begin

a = 4'b0011;

d = $signed(4'b0011); //转化为有符号数

b = a << 2;

c = d >>> 2;

$display("b = %4b",b); //左移低位补零,1100

$display("c = %4b",c); //右移,逻辑运算右移>>,高位补0,算术右移>>>,高位补符号位 c = 1111

end

endmodule

- 按位与或

module tb_test.v

logic [3:0] a;

logic [3:0] b;

initial begin

a = 4'b0011;

b = 4'b0011 & 4b'1100;

$display("b = %4b",b);

$finish;

end

endmodule

- 缩减运算符,单目运算符,第一位与下一位进行运算,最后输出一位

- 三目运算符

module tb_test.v

logic [3:0] a;

logic [3:0] b;

logic sel;

logic [3:0] mux;

initial begin

mux = sel ? a : b;

$finish;

end

endmodule

- {a,b} -- 将ab两个数连接在一起,

a = 4b'1100;

b = 4b'0011;

c = {a,b}; // 1100_0011

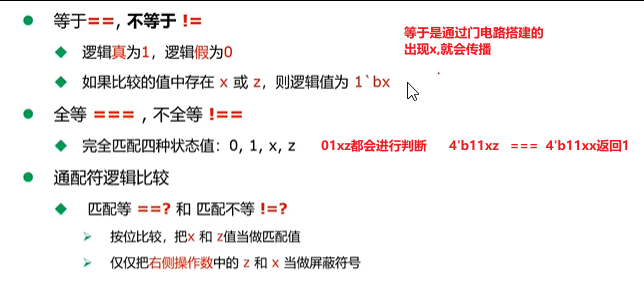

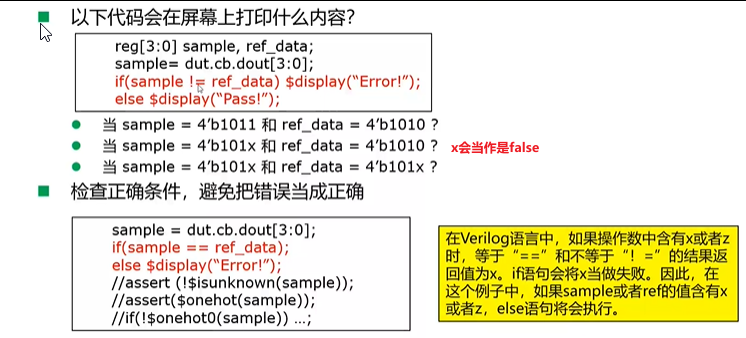

逻辑比较运算符

== != 遇到x和z,就会返回x

=== !=== 会将0 1 x z都进行匹配

通配比较符

匹配等==?和不匹配等!=?,按位比较,把x和z值当作匹配值,仅仅把右侧操作数中的z和x当作屏蔽信号

可以理解为,右边能够匹配上左边就返回真,xz可以取任意值0或1

a=4'b1111;

b=4'b11xz

a==?b//数字相等,只要x和z能通配到1就可以是匹配等,返回逻辑值为1'b1,真

A = 010z;

B = 0101;

A ==? B; //右边匹配不上左边 x

B ==? A; // z=1的时候,右边===左边 1

赋值语句

- -= += *= /= %=

- 在assign中使用复合赋值运算,会形成组合逻辑环comb loop

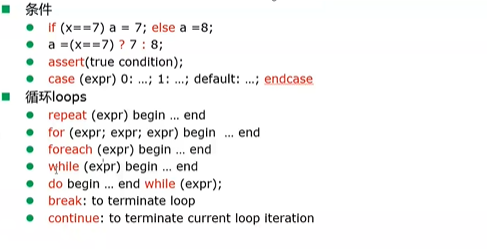

三.控制语句

自增和自减运算符

经常用在for循环中

for(int i = 0 ; i < 3; i++)begin

.....

end

i = 1;

j = i++; // j = 1

j = ++1; // j = 2

j = i--; // j = 1

j = --i; // j = 0

在阻塞赋值总使用自增自减运算符,会造成竞争与冒险

module tb_test;

integer i,j;

initial begin

i = 0;

j = 0

while(i++<5) begin //先判断再加一,当i=5时,判断不满足,还要再加1,最后i = 6

end

while(++j<5) begin // 先加1,再判断,j=5

end

end

endmodule

自定义类型

使用typedef为一个数据类型创建符号

typedef logic [31:0] vec;

vec a; // 创建32位a变量

vec b; // 创建32位b变量

在一些变量定义比较长的时候进行使用

数据类型转换

type'(value或variable)

logic signed [31:0] a;

logic [31:0] b;

logic [63:0] c;

assign c = a*b; //error,有符号数*无符号数出错,需要进行数据类型转换

assgin c = unsigned(a)*b;

bit [7:0] playload[]; //不给数组长度就是定义了一个动态数组

int temp = $random; // 生成一个随机数

playload = new [(temp%3)+2]; //实例化数组并指定长度

playload = new [(uint'(temp)%3)+2];

playload = new [(unsigned'(temp)%3)+2];

顺序控制

1.for循环

sv中循环遍历可以在for语句中定义,verilog中只能定义在外部

for循环中声明的i和外部声明的i是不相同的,互不影响

for(int i;i<3;i++) begin

end

- while

while() begin

end

- continue/break/return

- return 结束函数和task;用于循环,停止循环

- continue 用于循环语句,结束本次循环,执行下次循环

- break 用于循环语句,跳出循环

- do ... while

- while循环的时候,不一定会执行

- do..while至少会执行一次

do begin

...

end while(条件)

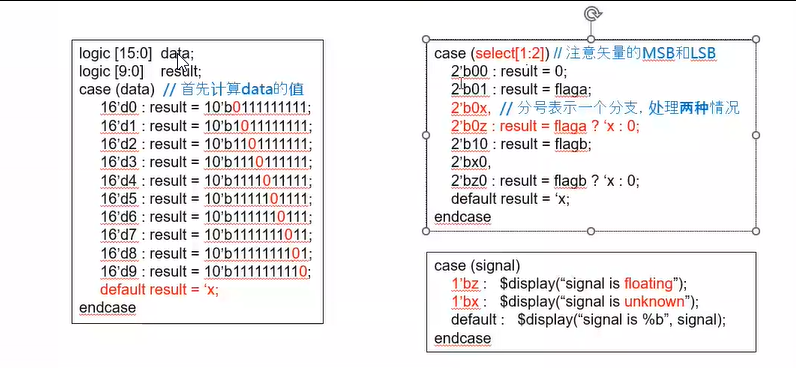

5.case

先计算表达式值,将case中的值与表达式的值进行匹配,匹配成功执行语句

- 匹配是从上到下匹配的

case(expr)

value1: xxxxxx

value2: xxxxxx

...

default xxxx

endcase

6.casez或casex

- casez 不关心z

- 忽略对应位上的z

sel = 4'b1100;

casez(sel)

4b'1101:data = 4'b01;

4b'zz00:data = 4'b00; //casez会匹配zz00 casez就不关心value中的z位置对应的值

default data = 4'b0011;

endcase

- casex忽略对应位置出现的x和z

- @ & wait

- @ 等待时间发生才执行后面的程序,可以是信号变量,上升沿,下降沿,事件变量

always@(posedge Clk) begin

...

end

- wait(expr) begin...end 是不可综合的

- 延迟信息 #5 5个时间单位,单位体现在timescale = 1np/100ps

07-verilog & sytem verilog的更多相关文章

- Verilog笔记——Verilog数字系统设计(第二版)夏宇闻

本片记录Verilog学习笔记,主要是和以往用的C语言的不同之处,以例子.代码的形式记录.学习以<Verilog数字系统设计>(第二版)为参考资料,援助作者夏宇闻. 1. C语言和Veri ...

- 【Verilog】verilog实现奇数次分频

实现占空比为50%的N倍奇数分频:首先进行上升沿触发进行模N计数,计数到某一个值时进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%的奇数n分频时钟.再者 同时进行下降沿触发的 ...

- system verilog中的类型转换(type casting)、位宽转换(size casting)和符号转换(sign casting)

类型转换 verilog中,任何类型的任何数值都用来给任何类型赋值.verilog使用赋值语句自动将一种类型的数值转换为另一种类型. 例如,当一个wire类型赋值给一个reg类型的变量时,wire类型 ...

- Verilog Tips and Interview Questions

Verilog Interiew Quetions Collection : What is the difference between $display and $monitor and $wr ...

- verilog 介绍

Verilog HDL Verilog HDL是在C语言的基础上发展起来的一种硬件描述语言,语法较自由.VHDL和Verilog HDL两者相比,VHDL的书写规则比Verilog HDL烦琐一些,但 ...

- verilog语法实例学习(4)

Verilog模块 Verilog中代码描述的电路叫模块,模块具有以下的结构: module module_name[ (portname {, portname})]; //端口列表 [parame ...

- verilog FAQ(zz)

1. What is the race condition in verilog? Ans :The situation when two expressions are allowed to exe ...

- 全平台轻量开源verilog仿真工具iverilog+GTKWave使用教程

前言 如果你只是想检查Verilog文件的语法是否有错误,然后进行一些基本的时序仿真,那么Icarus Verilog 就是一个不错的选择.相比于各大FPGA厂商的IDE几个G的大小,Icarus V ...

- 【FPGA学习】根据datasheet编写Verilog驱动(PCF8574 IO扩展板练习)

在之间的博客中已经讲了如何阅读一本datasheet并编写Verilog驱动代码,而在这篇博客中就加以应用,为PCF8574 IO扩展板编写驱动并观察效果,至于为什么选择这个,一方面是因为这个芯片功能 ...

- 【黑金原创教程】【FPGA那些事儿-驱动篇I 】实验十四:储存模块

实验十四比起动手笔者更加注重原理,因为实验十四要讨论的东西,不是其它而是低级建模II之一的模块类,即储存模块.接触顺序语言之际,“储存”不禁让人联想到变量或者数组,结果它们好比数据的暂存空间. . i ...

随机推荐

- 华企盾DSC防泄密软件:svn、git更新后有感叹号常见处理方法

1.查看客户端日志检查TSVNcache.exe进程是否是legal:1 2.TSVNcache.exe进程是否允许访问未配置加密进程的后缀 3.svn服务器不是加密进程也未装网络驱动,或者加密类型未 ...

- 数字孪生结合GIS能够在公共交通领域作出什么贡献?

数字孪生结合地理信息系统(GIS)在公共交通领域具有潜在的重大贡献,这种结合可以帮助城市更高效地规划.运营和改进公共交通系统.以下是一些关键方面的讨论,以说明数字孪生和GIS在这一领域的作用: 数字孪 ...

- 万界星空科技MES系统中的生产调度流程

MES系统生产调度的目标是达到作业有序.协调.可控和高效的运行效果,作业计划的快速生成以及面向生产扰动事件的快速响应处理是生产调度系统的核心和关键. 为了顺利生成作业计划,需要为调度系统提供完整的 ...

- Python——第五章:csv模块

未来我们会使用爬虫获取到一些json文件,例如去英雄联盟官方爬取英雄的数据库 查看代码 {"hero":[{"heroId":"1",&qu ...

- 玩转Python:处理音频文件,两个非常重要的库,很实用,附代码

pyaudio和sounddevice都是用于Python中音频处理和流的库,允许用户通过他们的API录制.播放和处理音频数据.下面是对这两个库的简要介绍: PyAudio PyAudio 提供了 P ...

- 通过 KernelUtil 截取 QQ / TIM 客户端 ClientKey 详细教程

前言 众所周知,由于最新版本 QQ 9.7.20 已经不能通过模拟网页快捷登录来截取 Clientkey,估计是针对访问的程序做了限制,然而经过多方面测试,诸多的地区.环境.机器也针对这种获取方法做了 ...

- Spring MVC的生命周期与简单三大组件的简单介绍

1.说到Spring MVC就会想到它是基于MVC设计模式的思想来设计的: 那么MVC设计模式是什么呢? 下面来介绍一下 MVC 设计模式 MVC是模型(model)-视图(view)-控制器(con ...

- C++中自定义结构体或类作为关联容器的键

目录 1. 概述 2. 实例 1. 概述 STL中像set和map这样的容器是通过红黑树来实现的,插入到容器中的对象是顺序存放的,采用这样的方式是非常便于查找的,查找效率能够达到O(log n).所以 ...

- 亿级日活业务稳如磐石,华为云CodeArts PerfTest发布

摘要:近日,华为云性能测试服务CodeArts PerfTest全新上线,提供低门槛.低成本的一站式云化性能测试解决方案. 本文分享自华为云社区<亿级日活业务稳如磐石,华为云CodeArts P ...

- 对象存储只能按文件名搜索,你out了吧

摘要:不少大公司的一个桶里都是几亿几十亿的对象,那他们都是怎么检索的呢? 本文分享自华为云社区<对象存储只能按文件名搜索? 用 DWR + ElasticSearch 实现文件名.文件内容.图片 ...