zedboard通过BRAM实现PS和PL的简单通信

使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

本文所使用的开发板是zedboard

PC 开发环境版本:Vivado 2016.2 Xilinx SDK 2016.2

---------------------

作者:wangdaling

来源:CSDN

原文:https://blog.csdn.net/rzjmpb/article/details/50365915 https://blog.csdn.net/rzjmpb/article/details/50365915

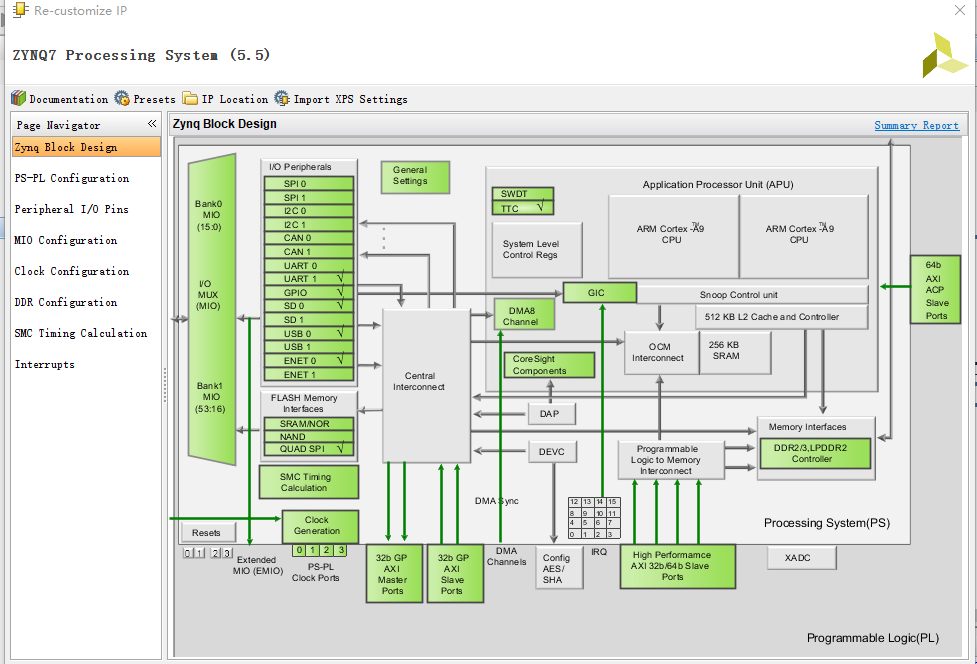

一、实现的结构原理图

1、PL端硬件架构搭建

新建工程后在Create Block Design中添加IP,点击添加IP的按钮后在弹出的搜索框中搜索ZYNQ时添加PS,搜索BRAM时添加AXI BRAM Controller 和Block Memory Generator,然后对PS中的相应接口做参数设置

2、软件SDK中的代码如下:

#include <stdio.h>

#include "platform.h"

#include "xparameters.h"

#include"xparameters_ps.h"

#include"xil_printf.h"

#include"xil_io.h"

//#define DDR_BASEARDDR XPAR_DDR_MEM_BASEADDR+0x10000000

int main()

{

init_platform();

int i;

int rev;

xil_printf("-----The test is start...\n\r");

for(i=0;i<15;i++)

{

Xil_Out32(XPAR_BRAM_0_BASEADDR+i*4,0x10000000+i);

}

for(i=0;i<15;i++)

{

rev=Xil_In32(XPAR_BRAM_0_BASEADDR+i*4);

xil_printf("the address at %x data is: %x \n\r",XPAR_BRAM_0_BASEADDR+i*4,rev);

}

xil_printf("-----The test is end!-------\n\r");

cleanup_platform();

return 0;

}

3、编译软件部分的代码,

4、将zedboard 板子的JTAG和PROG的端口与PC电脑端相连

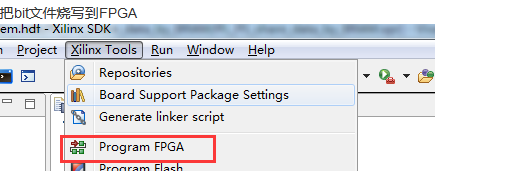

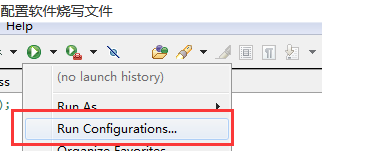

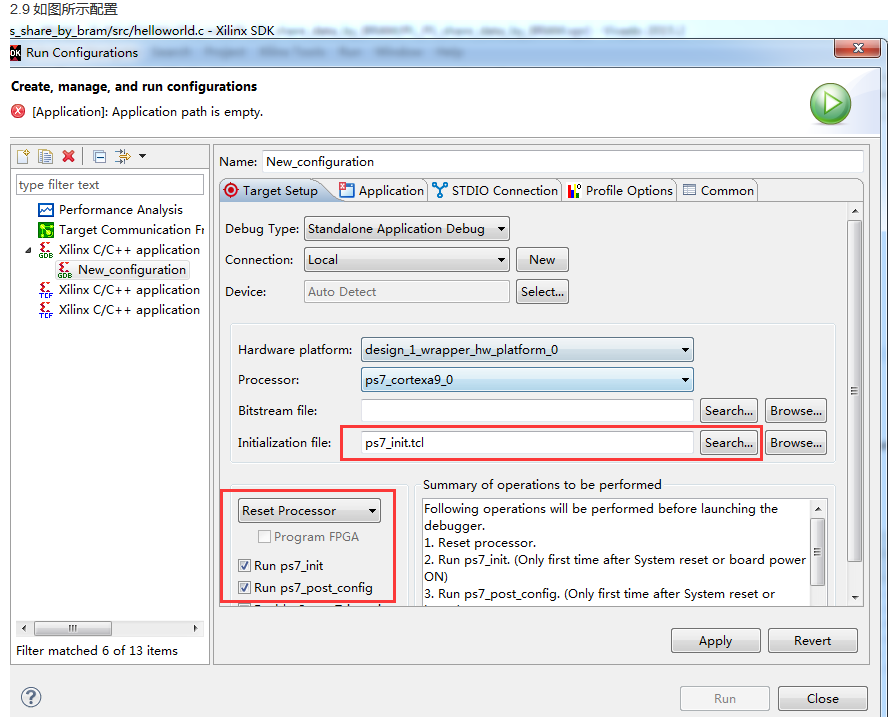

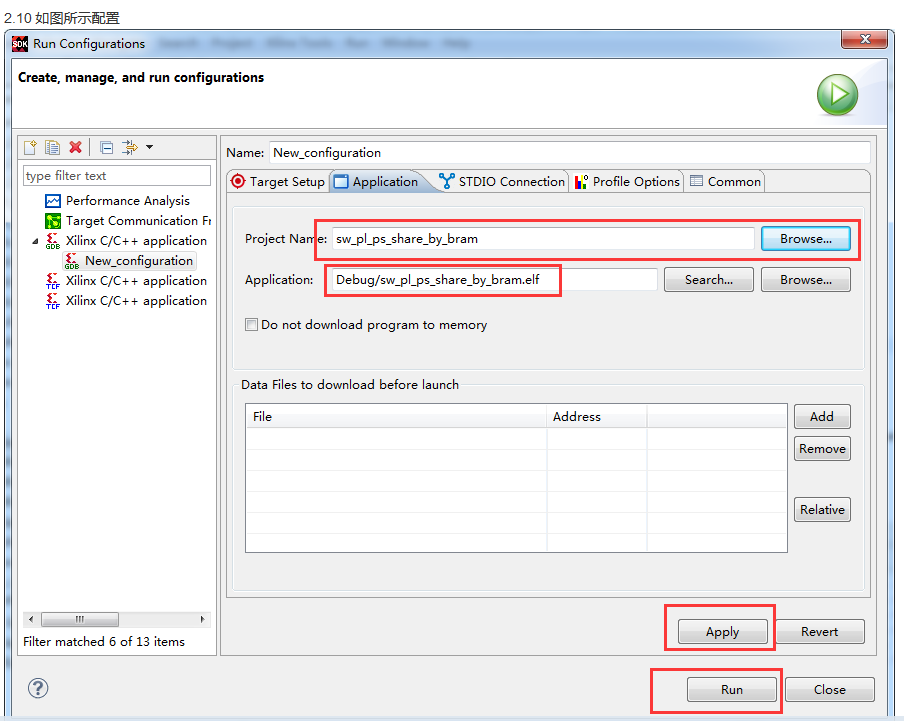

5、然后program FPGA(从硬件部分生成的bitstream),run configuration,run

zedboard通过BRAM实现PS和PL的简单通信的更多相关文章

- 第十二章 ZYNQ-MIZ702 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- 第十一章 ZYNQ-MIZ701 PS读写PL端BRAM

本篇文章目的是使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将 ...

- Zedboard学习(三):PL下流水灯实验 标签: fpgazynqPL 2017-07-05 11:09 21人阅读 评论(0)

zynq系列FPGA分为PS部分和PL部分. PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分. PS: 处理系统 (Processing System) , 就是与F ...

- 使用axi_datamover完成ZYNQ片内PS与PL间的数据传输

分享下PS与PL之间数据传输比较另类的实现方式,实现目标是: 1.传输时数据不能滞留在一端,无论是1个字节还是1K字节都能立即发送: 2.PL端接口为FIFO接口: PS到PL的数据传输流程: PS到 ...

- [原创]基于Zynq PS与PL之间寄存器映射 Standalone & Linux 例程

基于Zynq PS与PL之间寄存器映射 Standalone & Linux 例程 待添加完善中

- Zynq PS和PL间的连接

跨越PS和PL的信号 AXI总线.EMIO.其他(看门狗.重启信号.中断信号.DMA接口信号) AXI标准 AXI(高级可扩展接口)是ARM AMBA的一部分.AMBA总线主要用于片上系统.AXI总线 ...

- PS与PL协同设计

https://blog.csdn.net/Fei_Yang_YF/article/details/79676172 什么是PS和PL ZYNQ-7000是Xilinx推出的一款全可编程片上系统(Al ...

- zedboard学习记录.2.PS+PL 流水灯与uart

1.建立一个工程. 硬件设计 2.IP integrator -> create block desgin;Run Block Automation. 3.add IP -> AXI GP ...

- Vivado设计二:zynq的PS访问PL中的自带IP核(基于zybo)

1.建立工程 首先和Vivado设计一中一样,先建立工程(这部分就忽略了) 2.create block design 同样,Add IP 同样,也添加配置文件,这些都和设计一是一样的,没什么区别. ...

随机推荐

- How to Convert a Class File to a Java File?

What is a programming language? Before introducing compilation and decompilation, let's briefly intr ...

- 研发协同平台持续集成之Jenkins实践

导读 研发协同平台有两个核心目标,一是提高研发效率 ,二是提高研发质量,要实现这两个核心目标,实现持续集成是关键之一. 什么是持续集成 在<持续集成>一书中,对持续集成的定义如下:持续集成 ...

- [ERROR]pip insall pyodbc

- 错误代码如下: pip install pyodbc Looking in indexes: http://172.16.1.250/repository/douban/simple Collec ...

- 自己用C语言写NXP S32K116 serial bootloader

了解更多关于bootloader 的C语言实现,请加我QQ: 1273623966 (验证信息请填 bootloader),欢迎咨询或定制bootloader(在线升级程序). 每次我有了新的EVA ...

- IP切换脚本

1. 新建bat文件: 2. 将下面内容拷贝进bat文件: 3. 运行bat文件: @echo off color 00title IP切换脚本:start @echo --------------- ...

- asp.net MVC项目开发之统计图echarts柱状图(一)

echarts统计图doc网址:http://echarts.baidu.com/echarts2/index.html 使用echarts,需要引用在js中,如果你已经下载echarts的js包,可 ...

- AOP in .NET

AOP in .NET AOP是所有现代OOP语言开发框架中的基础功能,随着Spring框架的普及,对于AOP的使用已经像喝水一样普通.可是知其然还要其所以然.本文将基于.NET环境探讨实现AOP的底 ...

- HTML连载69-透视属性以及其他属性练习

一.透视属性 1.什么是透视 透视简单来说就是近大远小 2.注意点:一定要注意,透视属性必须添加到需要呈现近大远小效果的元素的父元素. 3.格式:perspective:数字px; 这里的数字代 ...

- centos docker redis 安装

1.下载redis镜像 docker pull redis 2.下载redis.conf文件 https://redis.io/topics/config 这边查找自己服务器redis对应的版本文件 ...

- Django之F与Q查询

F查询 from django.db.models import F,Q # 1.查询库存数大于卖出数的书籍 res = models.Book.objects.filter(kucun__gt=F( ...